前言

简单整理,深入学习参考教科书

注意:555定时器不要求

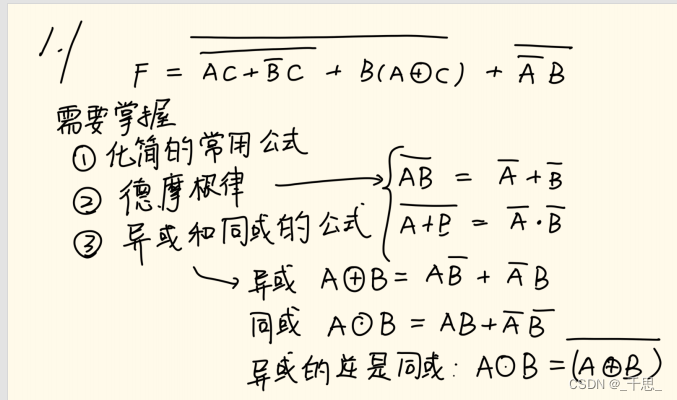

1. 逻辑函数化简(第4章 布尔代数和逻辑化简)

1.1 题型一:给一个表达式,要求化简,一般这道题考察的是对于德摩根的理解以及常用的一些化简公式(当然重点还是德摩根)

例题:

补充:

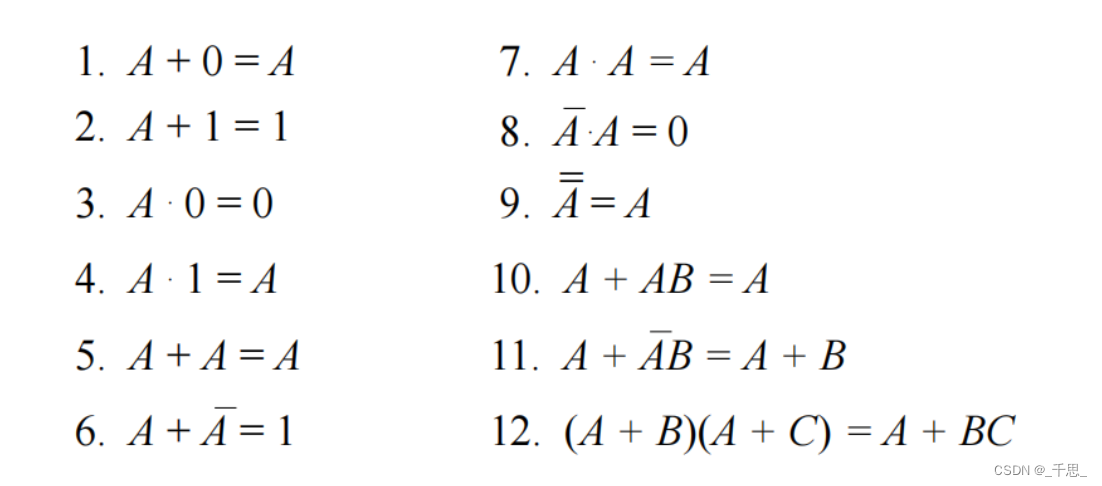

- 化简常用的公式

- 同或和异或

异或的概念:异或运算在逻辑上表示当两个输入不同时,输出为真(1);当两个输入相同时,输出为假(0)

同或的概念:同或运算在逻辑上表示当两个输入相同时,输出为真(1);当两个输入不同时,输出为假(0)。

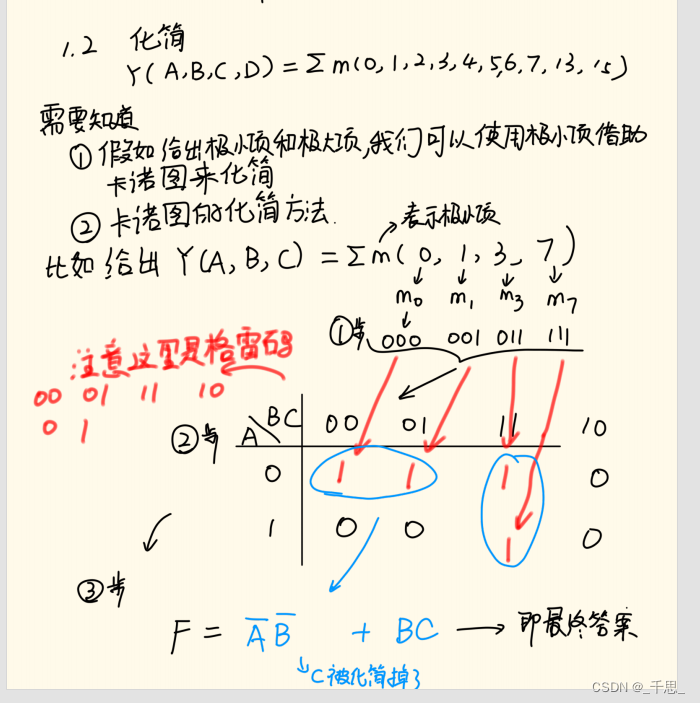

1.2 F给出最小项,要求化简,这里一般结合卡诺图进行化简

2. 给一个选择器要求实现给定的逻辑函数

考察:选择器或者译码器实现组合逻辑函数

这个一般是画图,把给定的极小项用 与或非 门实现逻辑函数

思路上和下面第4类似,以第4的思路来

3. 组合逻辑设计(第五章组合逻辑分析、第六章组合逻辑电路、第九章计数器(重点是9.5同步计数器的设计))

考察:组合电路设计过程(考试不会给出功能表)

题目:

使用D触发器实现一个二位的格雷码(00 01 11 10)计数器,要求如下

- 写出状态图

- 由状态图导出次态表

- 卡诺图化简并且给出逻辑表达式

- 给出电路图

注意最后的逻辑表达式是关于Q的!

这个过程比较繁琐,不过思路上还是比较清晰,课本上讲解的很清楚,不过有一点注意的是有时候会加入一路,让ADD/^DOWN 控制加减,这里最后异或或者同或处理即可

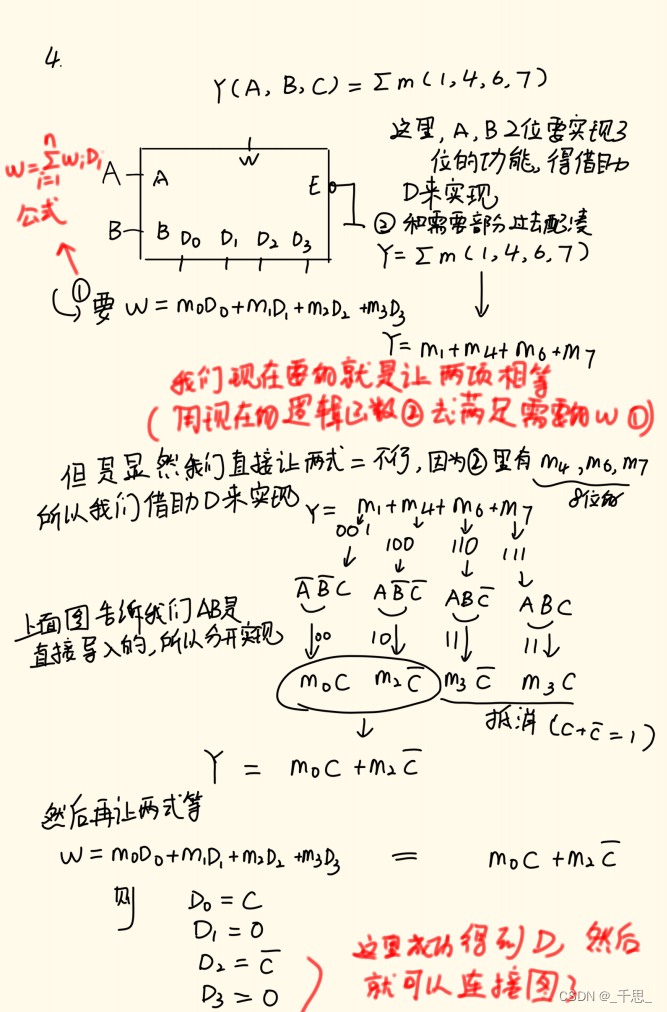

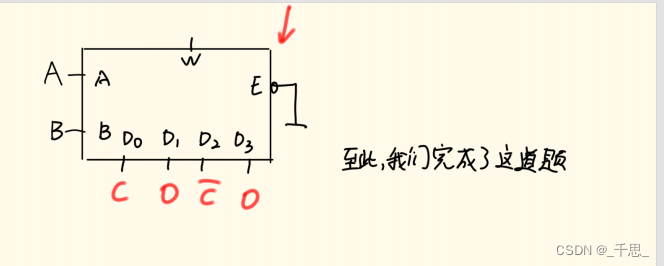

4. 使用3-8实现一个4位极小项的 逻辑函数

考察:选择器或者译码器实现组合逻辑函数

这个题主要考察的是对于 m i ∗ D i m_i*D_i mi∗Di这个公式,原始给定的是16位的,但是要求使用8位完成,这里就需要使用这个公式,然后用 S 0 , S 1 , S 2 S_0,S_1,S_2 S0,S1,S2进行选择

给一道另外的例题

5. 表决问题,3个人 ABC ,多数1为1,否则0,要求给出真值表,卡诺图化简后的结果以及只使用与非门给出电路图

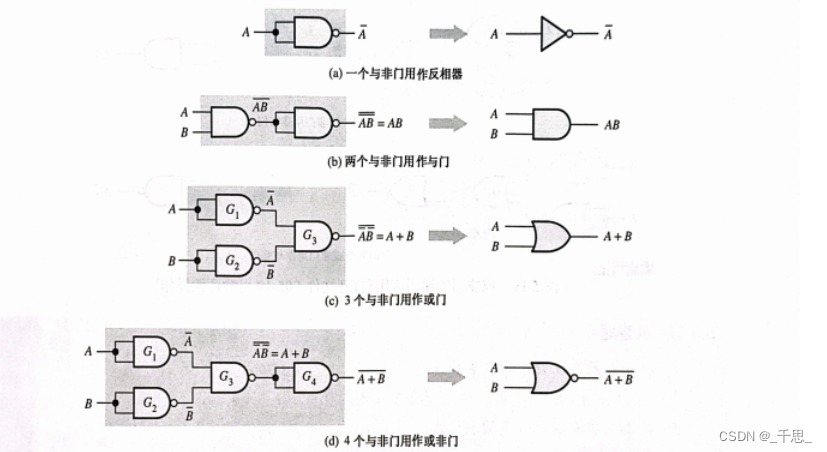

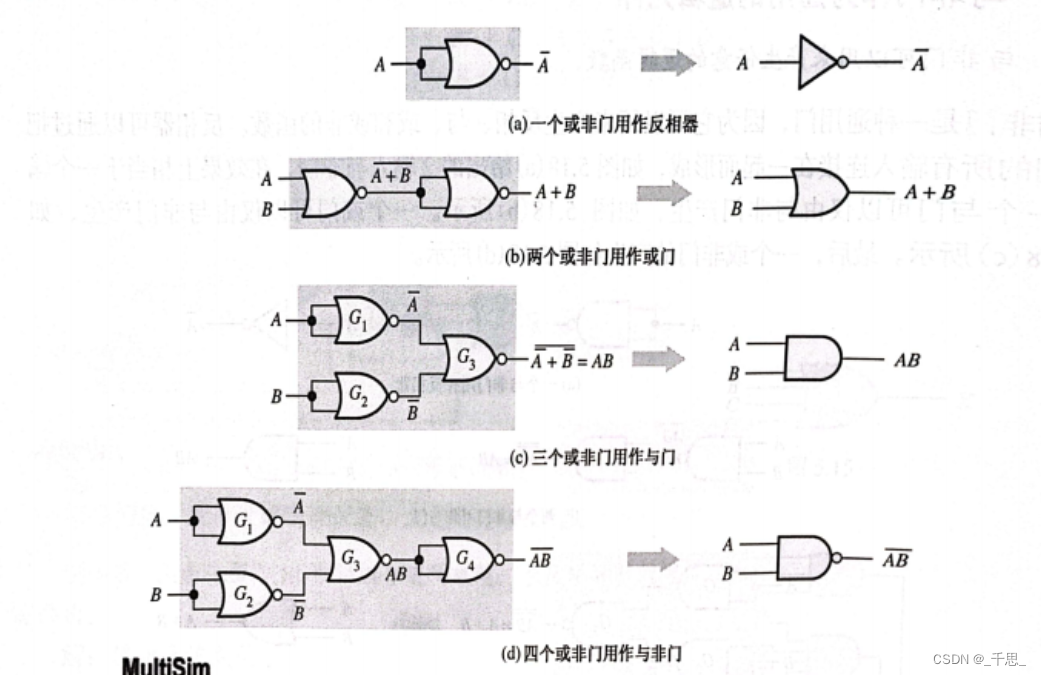

这里前两个到不难,只是后面这个只使用与非门给出电路图,注意连续两级使用与非门即可实现三项或的关系

(图片来自教科书与非门或非门)

6.给出一个JK触发器的CLK以及J,K要求给出Q的变换

考察:画时序图即可,给一个现成的器件和给出引脚的功能描述,给出输入的时序画出输出的时序来(注意这里需要画出时钟+时序输出);

画图即可

7. 并行输入全1,前4个时钟无效,给出后9个时钟的 Q 7 Q_7 Q7

111111110

考察:画时序图即可,给一个现成的器件和给出引脚的功能描述,给出输入的时序画出输出的时序来(注意这里需要画出时钟+时序输出);

![<span style='color:red;'>大</span><span style='color:red;'>数据</span>分析<span style='color:red;'>与</span>挖掘-<span style='color:red;'>期末</span><span style='color:red;'>复习</span>大纲[HBU]](https://img-blog.csdnimg.cn/5f969dee1f6a4cb3a0cc54cc9ff48b6c.png)

![[C++]——同步异步日志系统(7)](https://i-blog.csdnimg.cn/direct/afe78e44d54945ee9aaa324d610b8b16.png)