实验内容

将差分时钟信号转化为 192MHz 时钟信号作为输出。

实验原理

PLL,即锁相环,一种反馈控制电路,具有时钟倍频、分频、相位偏移和可编程占空比的功能。

实验步骤

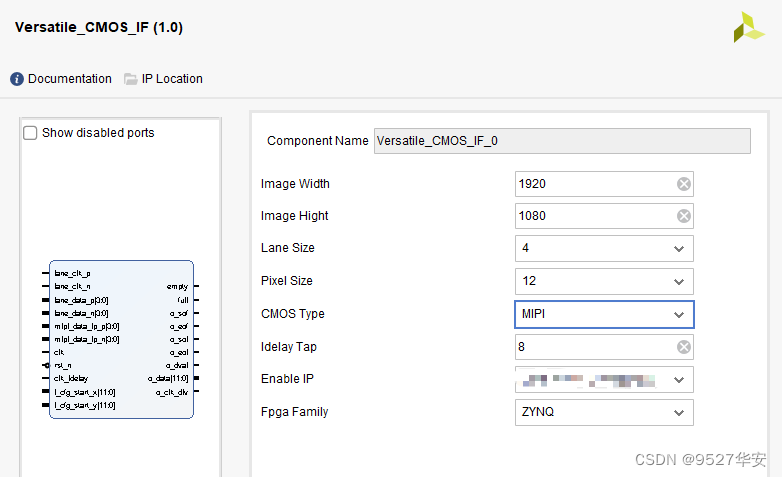

添加 clocking wizard IP核,输入为 200MHz 差分时钟,输出为 192MHz 和 96MHz 时钟信号

例化IP核

/**********************************************

*********** PLL 例化

**********************************************/

clk_wiz_0 inst_clk(

// Clock out ports

.clk_out1(sys_clk_192M), // output clk_out1

.clk_out2(sys_clk_96M), // output clk_out2

// Status and control signals

.reset(!rst), // input reset

.locked(locked), // output locked

// Clock in ports

.clk_in1_p(sys_clk_p), // input clk_in1_p

.clk_in1_n(sys_clk_n) // input clk_in1_n

);

实验结果

- 可以从图中看出,产生所需频率的时钟信号需要一定的时间,locked 信号为高电平时才会输出稳定的时钟信号,输出频率满足设定要求,在 locked 信号拉高之前,时钟信号不稳定。

- 调用 clocking wizard IP 核后,IP 核会自动添加约束,可以在 constraints wizard -> existing create clock constraints 里面来查看。