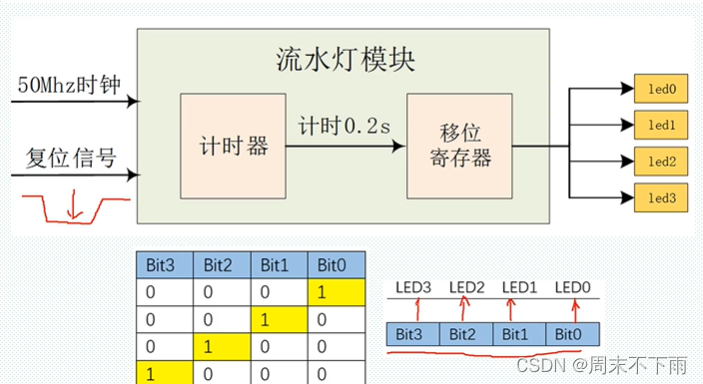

创建工程

- 型号选择:以 AXU9EG 开发板为例,芯片选择 xczu9eg-ffvb1156-2-i

创建 HDL 代码

- 注意:由于输入时钟为 200MHz 的差分时钟,因此需要添加 IBUFDS 原语连接差分信号

`timescale 1ns / 1ps

module led

#(

parameter CNT_MAX = 'd199_999_999

)(

input wire sys_clk_p,

input wire sys_clk_n,

input wire rst, //同步低复位

output reg led

);

reg [31:0] timer_cnt;

wire sys_clk;

/**********************************************

*********** IBUFDS 原语

**********************************************/

IBUFDS IBUFDS_inst(

.O(sys_clk),

.I(sys_clk_p),

.IB(sys_clk_n)

);

/**********************************************

*********** 信号赋值

**********************************************/

// 赋值 timer_cnt

always@(posedge sys_clk) begin

if(!rst) begin

timer_cnt <= 32'b0;

end

else if(timer_cnt >= CNT_MAX) begin

timer_cnt <= 32'b0;

end

else begin

timer_cnt <= timer_cnt + 32'd1;

end

end

// 赋值 led

always@(posedge sys_clk) begin

if(!rst) begin

led <= 1'b1;

end

else if(timer_cnt >= CNT_MAX) begin

led <= ~led;

end

end

endmodule

仿真

- 此步骤的目的是进行功能验证,不需要时可以忽略。仿真前需要编写激励文件 testbench

`timescale 1ns / 1ps

module tb_led(

);

parameter CNT_MAX = 32'd10;

reg sys_clk_p;

wire sys_clk_n;

reg rst;

wire led;

led #(

.CNT_MAX(CNT_MAX)

)tb_led(

.sys_clk_p(sys_clk_p),

.sys_clk_n(sys_clk_n),

.rst(rst),

.led(led)

);

// 初始化clk信号

assign sys_clk_n = ~sys_clk_p;

initial begin

sys_clk_p = 0;

forever #2.5 sys_clk_p = ~sys_clk_p;

end

// 初始化rst信号

initial begin

rst = 0;

#100;

rst = 1;

end

endmodule

仿真得到的时序波形图:

添加管脚约束

综合是将HDL代码转换为门级网表的过程,实现是将门级网表映射到目标FPGA设备的过程。

- 执行综合 run synthesis

- 等待综合完毕,open synthesized design

- 选择 I/O Planning,根据原理图和手册来定义引脚

- ctrl+s 保存

以 AXU9EG 开发板为例:

| 名称 | 位置 |

|---|---|

| led | AM13 |

| rst | AN12(对应 PL KEY) |

| sys_clk_p | AL8 |

添加时序约束

- constraints wizard

- 设置时钟频率

- 重新综合一遍,因为综合是将RTL代码转换为门级网表,并根据时序和其他约束进行逻辑优化。如果在综合之后添加或修改了时序和管脚约束,综合工具不会自动知道这些约束的变化,所以最好重新 run synthesis

综合后的原理图:

生成 bit 文件

- generate bitstream

下载

拨码开关调整到 JTAG 模式,连接 JTAG 接口后,上电

open hardware manager -> open target -> auto connect 后,成功扫描到硬件

- 选择芯片,右键 program device

- 点击 program 等待下载完成

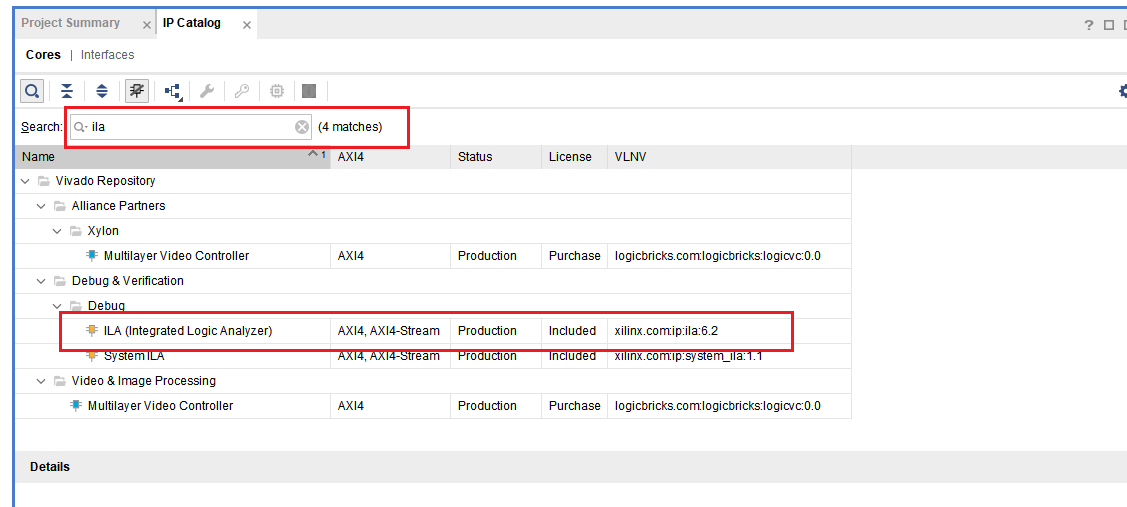

ILA 在线调试

- IP Catalog -> 搜索 ILA

- Number of Probes:需要采样的信号数量

- Sample Data Depth:采样深度

- Probe Width:信号的位宽

- 在 HDL 代码中例化 ILA

/**********************************************

*********** ILA 例化

**********************************************/

ila_0 inst_ila (

.clk(sys_clk), // input wire clk

.probe0(timer_cnt) // input wire [31:0] probe0

);

- 重新生成比特流,并连接

- 选择 ILA 窗口

- 点击运行即可看到采集信号的波形,采集的个数为设置的采样深度

- 可以添加采样触发条件

最终调试窗口结果

![[leetcode] shortest-subarray-with-sum-at-least-k 和至少为 K 的最短子数组](https://i-blog.csdnimg.cn/direct/054603904a2b44d290b4a97266939257.png)