1 DDR3 8倍预取

- DDR3相比DDR2外部IO时钟又提高了一倍,因此DDR3外部IO时钟是内核时钟的4倍,再加上双沿采样,因此DDR3可以实现8倍预取

2 DDR3 芯片位宽

- DDR3使用8倍预取技术,指的是芯片位宽(DQ数据线位宽)与内核存储单元位宽之比为1:8,但DDR3的芯片位宽有多种选择,一般有×4、×8、×16,虽然芯片位宽不同,但它们与内核存储单元位宽都是8倍的关系。下面给出不同芯片位宽的DDR3的功能框图。

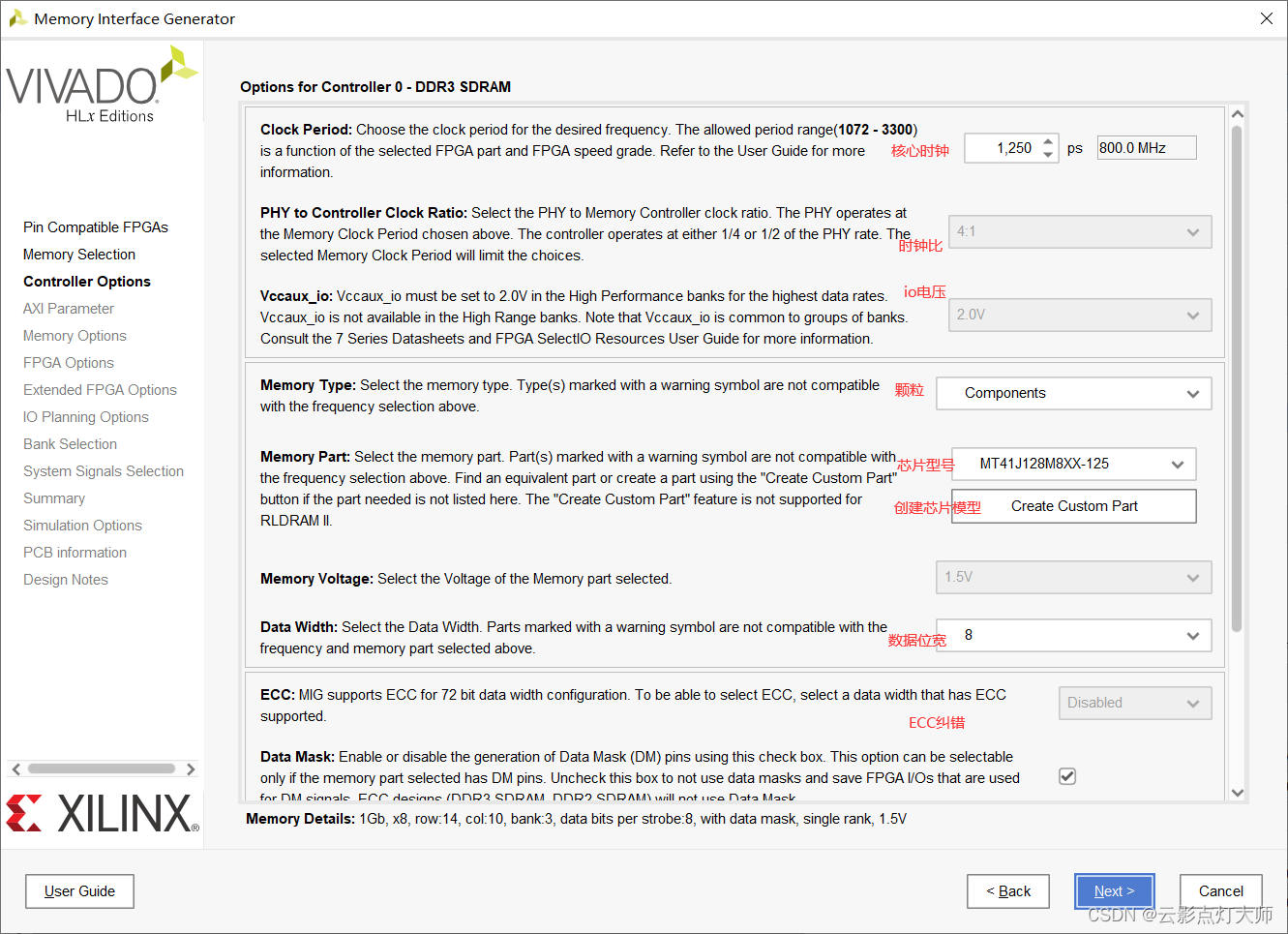

3 MIG ip核

我们在使用DDR3芯片的时候,并不需要自己写verilog代码来实现DDR3芯片复杂的接口时序,以vivado为例,vivado中提供了MIG ip核可以实现DDR3芯片的接口时序,我们只需要写一个读写控制器,把这个MIG ip核给用起来就好了。

DDR3读写控制器,它的作用是控制MIG ip核。然后MIG ip核生成对应的控制时序,用来控制外部DDR3芯片。

初始化时序、读写时序、刷新、预充电等等由MIG ip核完成。下图是xilinx 7系列FPGA内存接口的解决方案。在FPGA的内部,包含DDR3读写控制器和MIG ip核。MIG ip核与读写控制器连接的接口叫做用户接口(UI),MIG ip核通过IO port与DDR3芯片连接的接口叫做物理接口(Physical Interface)。

读写控制器与MIG ip核均为FPGA内部电路,DDR3为一个存储芯片,与FPGA是两个不同的芯片