上回书说到数电中的最常用的表达式——逻辑表达式(由布尔代数组成)以及常用的两种图表——真值表(真值表表示的是所有的输入可能的线性组合以及输出)和卡诺图(卡诺图则是一种化简工具,排除冗余项,合并可合并项)。

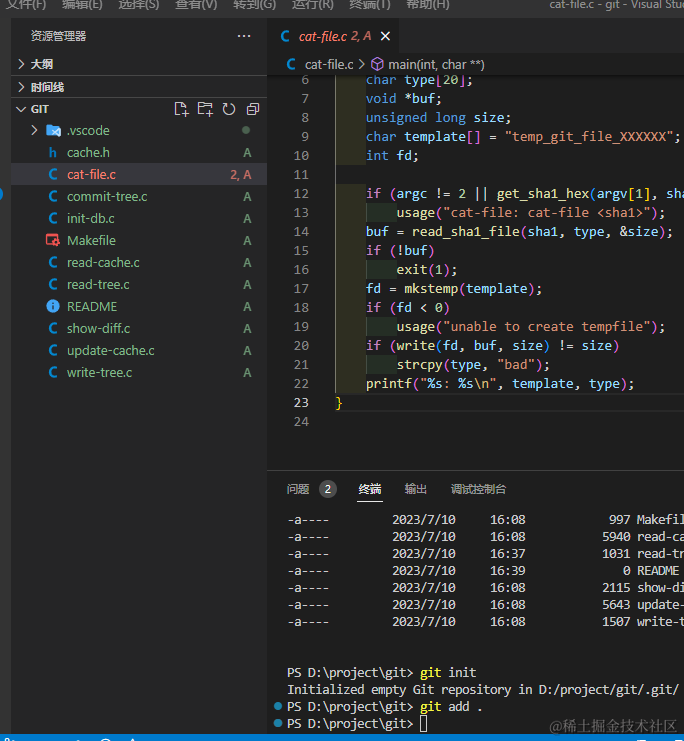

今天,先来看看昨天说的基本逻辑电路功能图的Modelsim的Verilog仿真,代码较为丑陋,请多包涵。

首先是主要的程序文件sign.v。

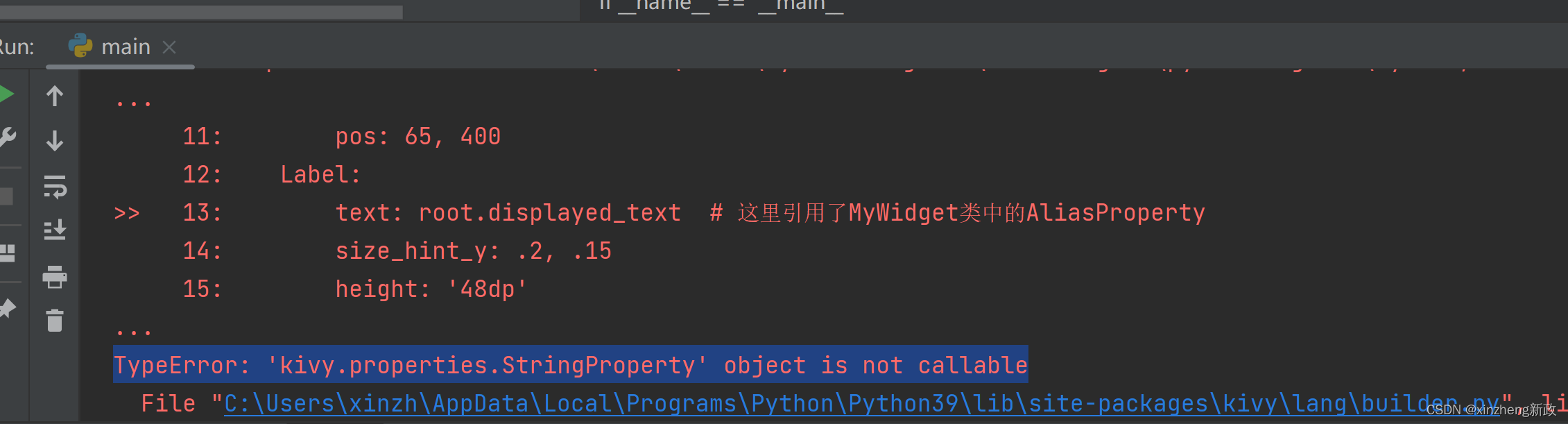

module sign(

input wire a,b, //输入

output wire p0,p1,p2,p3,p4 //输出

);

assign p0 = b&a; //与门

assign p1 = a|b; //或门

assign p2 = ~a; //非门

assign p3 = a^b; //异或门

assign p4 = ~(a^b); //同或门

endmodule

其次是测试文件sign_tb.v。

`timescale 1ns/1ns

module sign_tb;

wire p0,p1,p2,p3,p4;

reg a,b;

sign U(.p0(p0),.p1(p1),.p2(p2),.p3(p3),.p4(p4),.a(a),.b(b));

initial // initializes the register variable to a definite value of one

begin

#20 a=0;b=0;

#20 a=0;b=1;

#20 a=1;b=0;

#20 a=1;b=1;

#20 $stop;

end

endmodule

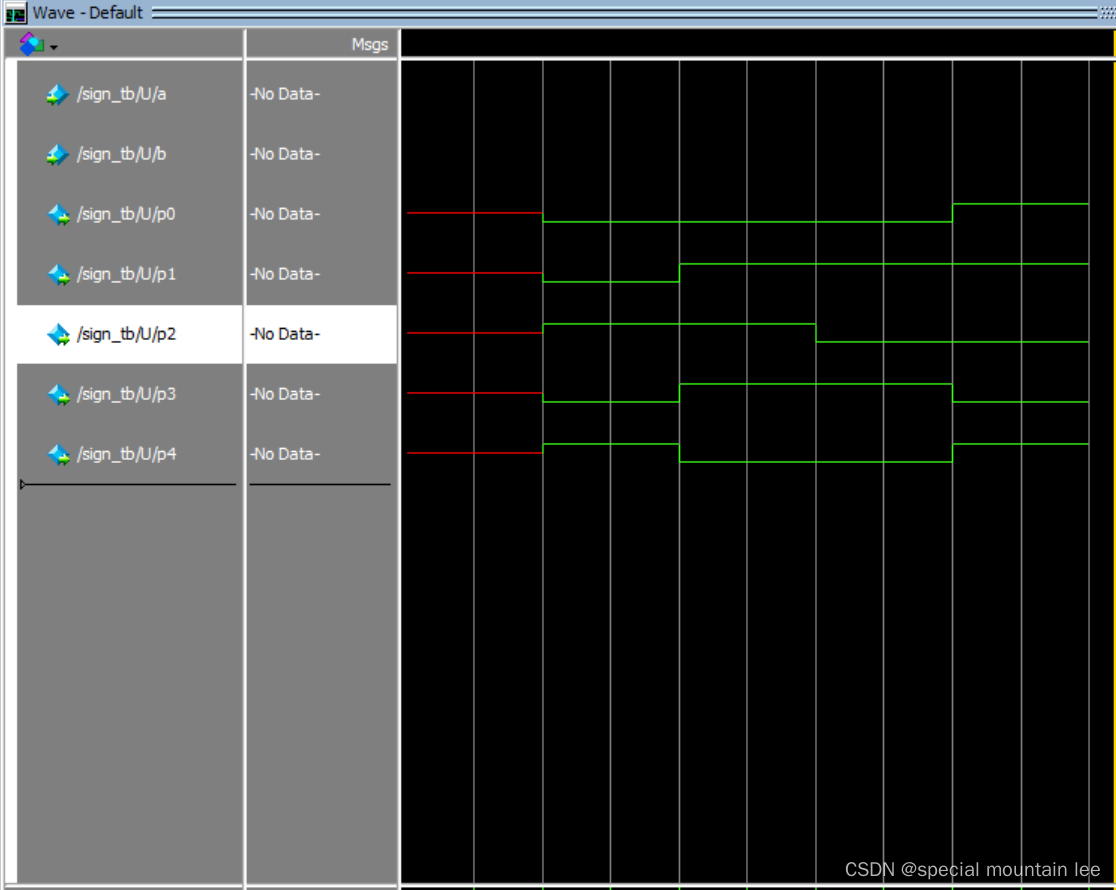

这是Verilog文件在Modelsim中运行的两个必要的文件,看看仿真图,大家可以对比真值表记忆理解。

此外,大家除了使用这软件编程的程序呢,也可以通过Multisim来模拟硬件的仿真。在Mutisim里面只需要点击放置其他数字,找到TTL,就能够看见各种门电路,当然还有一些能够起到门电路功能的芯片,也包含在里面,大家可以去探索。后续也会出一点Modelsim以及Multisim的一些仿真实例。

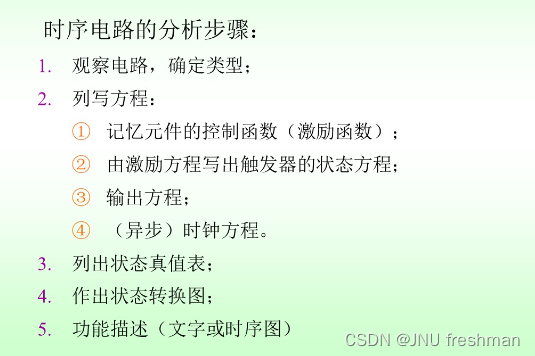

好了,完成昨天遗留的部分,咱们继续记笔记,本次咱们看的是组合逻辑电路的分析与设计。组合逻辑电路是数字电路的一种类型。组合逻辑电路在任何时刻的输出仅仅取决于当时的输入信号,而与电路原来的状态无关,这里就要注意了,因为在后面的时序电路中,它的输出是次态和现态有关。组合逻辑电路呢,它里面最重要的部分就是门电路,把这些门组合起来,就能够构成组合逻辑电路了。

接着,就是它的两个考点,一个是组合逻辑电路的分析,步骤如下:1、确定逻辑电路的输入和输出:根据题目,明确有哪些输入变量以及对应的输出变量。2、写出逻辑表达式:根据电路中逻辑门的连接关系,从输入到输出逐步推导,写出每个输出变量与输入变量之间的逻辑表达式。3、化简逻辑表达式:使用逻辑代数的定律和公式,对表达式进行化简,以得到最简形式。4、列出真值表:将输入变量的所有可能取值组合逐一列出,并计算出对应的输出值。5、分析逻辑功能:根据真值表,总结和描述电路的逻辑功能,即说明在不同输入组合下输出的情况。另外一个则是组合逻辑电路的设计,步骤如下:1、明确设计要求:根据题目,确定电路的输入和输出变量,以及它们之间需要实现的逻辑关系。例如,设计一个判断两个一位二进制数是否相等的电路。2、列出真值表:根据设计要求,列出输入变量的所有可能组合以及对应的输出值。3、写出逻辑表达式:根据真值表,通过逻辑函数的化简方法(如卡诺图、公式法等)写出最简的逻辑表达式。4、画出逻辑电路图:根据化简后的逻辑表达式,使用逻辑门电路画出相应的逻辑电路图。但是,这里它有时候会恶心你,非得用与非门,或者是或非门去画电路图,这就要去转换式子了。我也是无语了。有那么多的门不用,非得选唯一的一种门电路。个人看法:不要为了用一个考点,而去出题目,多一点创新不好吗?

最后,来看组合逻辑电路的应用——半加器和全加器,半加器是一种实现两个一位二进制数相加的组合逻辑电路。它能产生本位和(Sum)以及向高位的进位(Carry),但不考虑低位来的进位。半加器由一个异或门和一个与门构成。异或门用于产生本位和,与门用于产生向高位的进位。全加器是能够计算三个一位二进制数相加的组合逻辑电路。它不仅考虑两个加数,还考虑来自低位的进位,并产生本位和以及向高位的进位。全加器通常由两个半加器和一个或门构成。其中一个半加器用于计算两个加数的和,另一个半加器用于计算这个和与低位进位的和,或门用于产生向高位的进位。

今天,就讲到这里,大家想想怎么去仿真。明天再告诉大家。

欲知后事如何,且听下回分解。OVO.......