一、实验目的

1. 熟悉Candence IC514软件,学会使用计算器对静态功耗,斜率等参数的导入与仿真。

2. 学习CMOS反相器,CMOS与非门,CMOS或非门的设计流程,分析影响电路性能的相关参数(静态功耗,Vm ……)。

3. 理解CMOS反相器做匹配的重要性(不同W下的VTC曲线),理解组合逻辑电路要达到反相器的性能需要对栅宽做哪些调整。

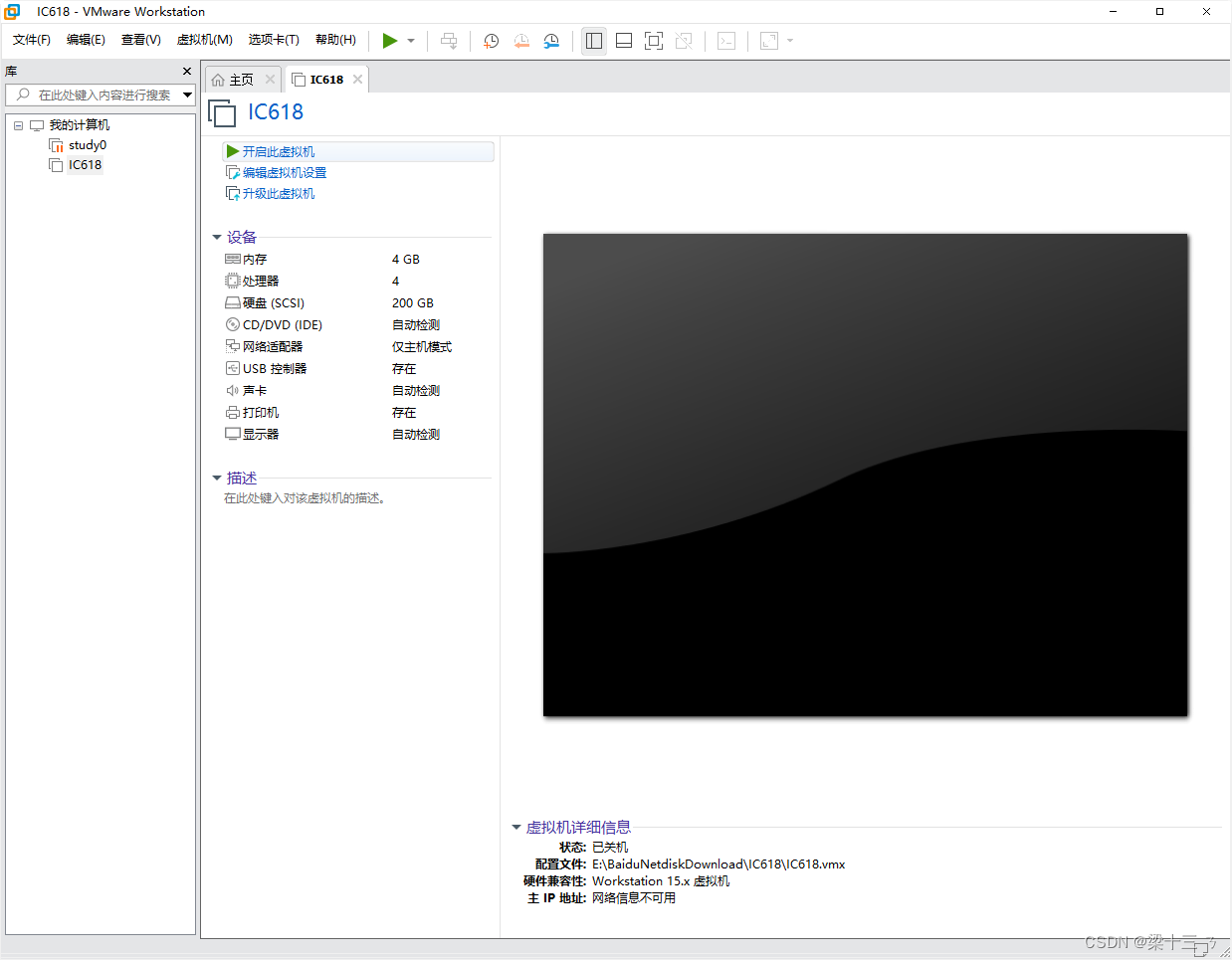

二、实验环境

集成电路设计实验室;Red Hat Enterprise linux5、Cadence IC Design Tools 5.10.41

三、实验原理

1. 噪声容限:

图1 噪声容限定义

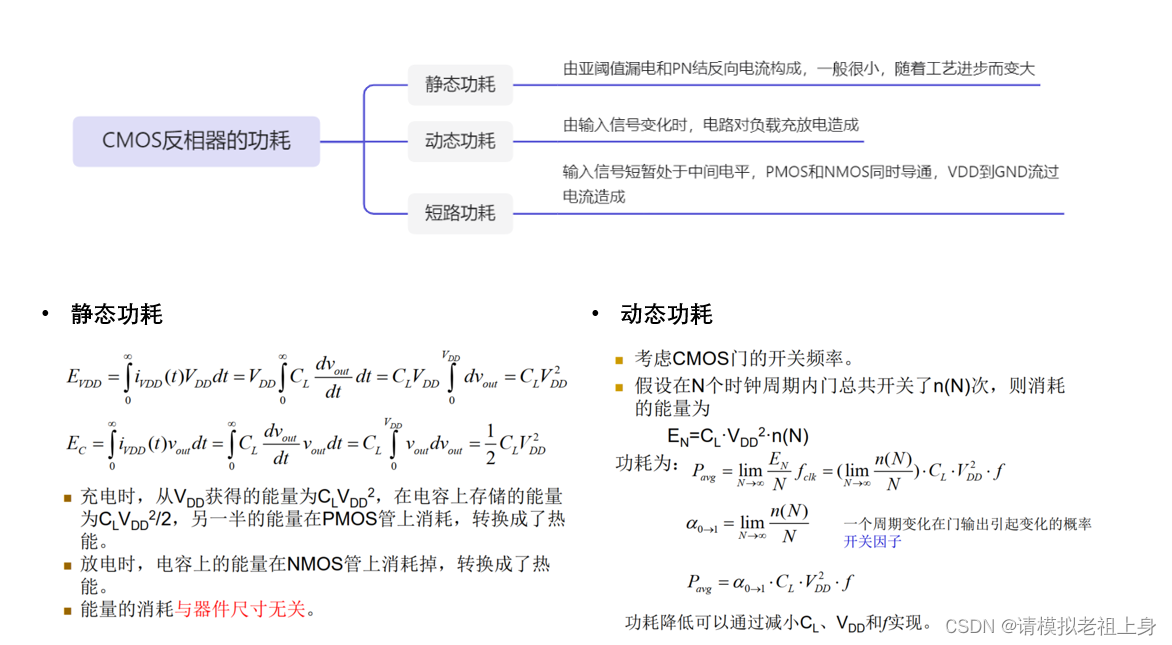

2. 数字电路的功耗:

图2 数字电路功耗一览

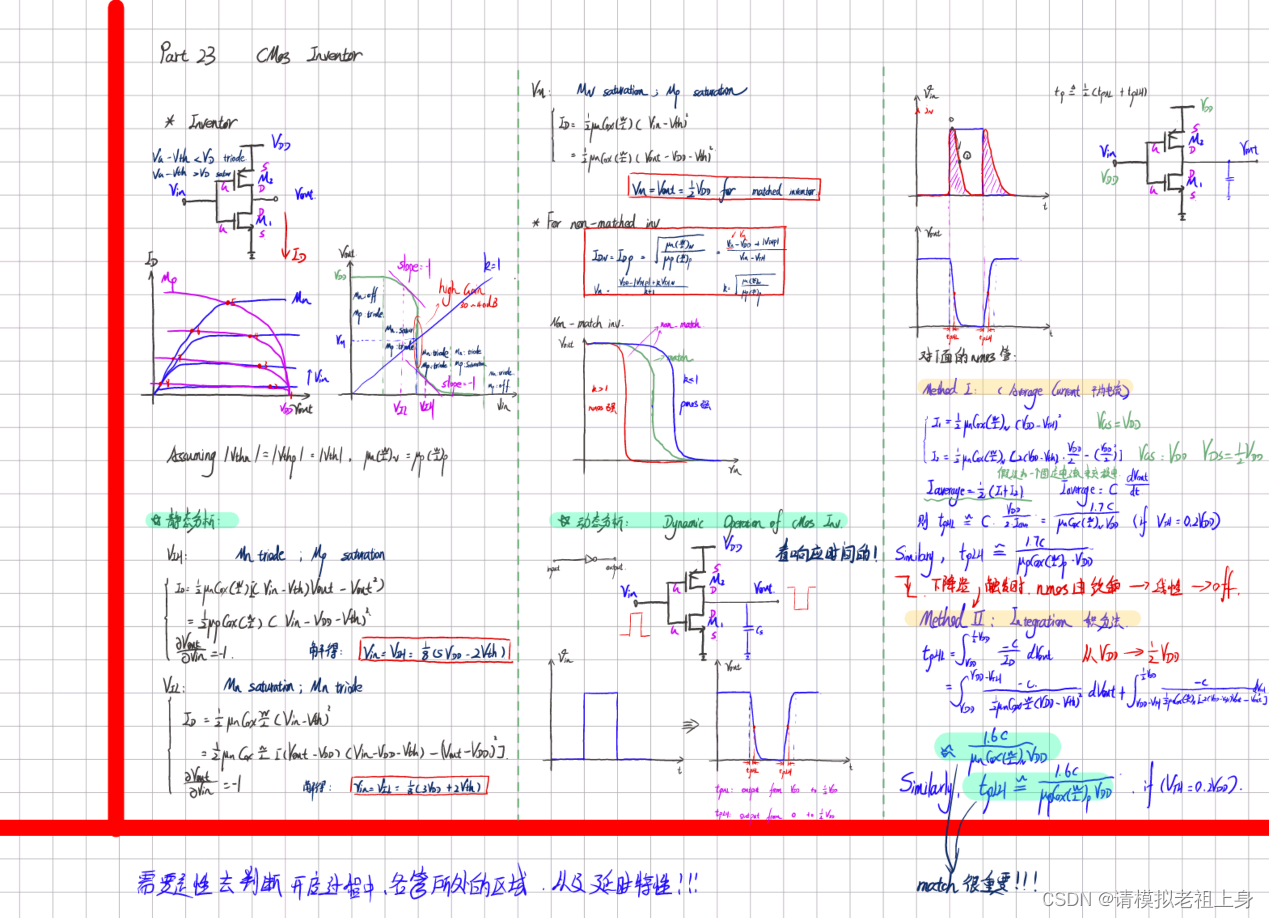

3. CMOS反相器电路详解:

图3 CMOS反相器电路详解

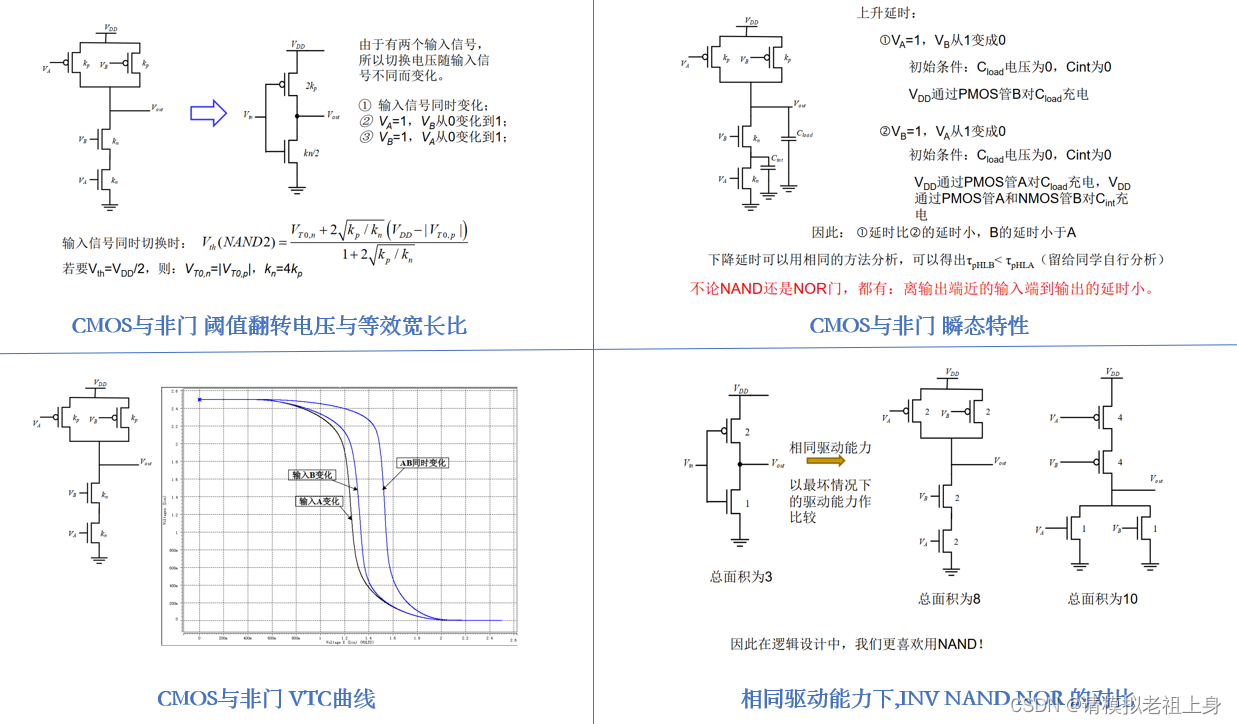

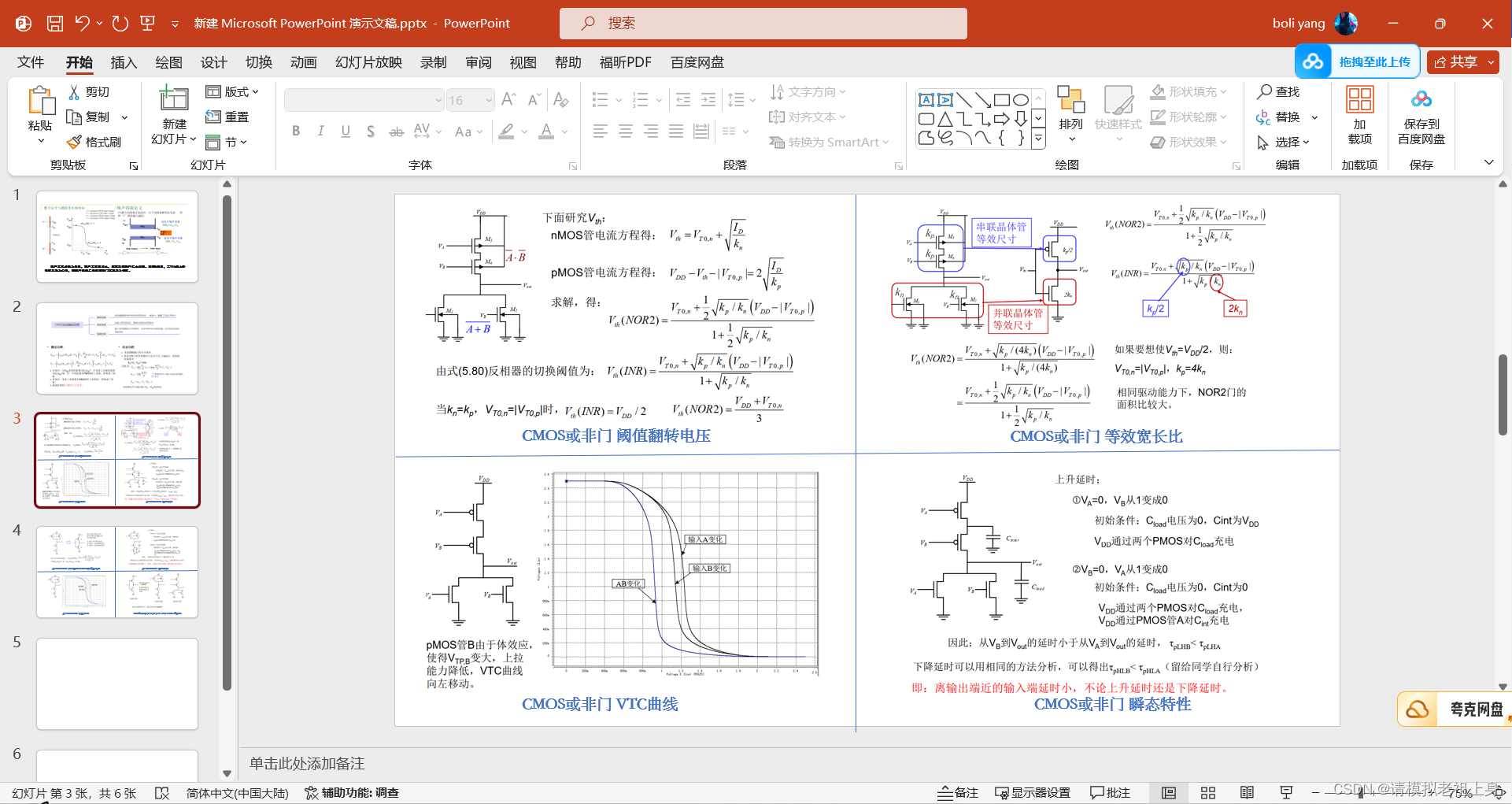

4. CMOS或非门电路详解:

图4 CMOS或非门电路详解

5. CMOS 与非门电路详解:

图5 CMOS与非门电路详解

四、实验步骤

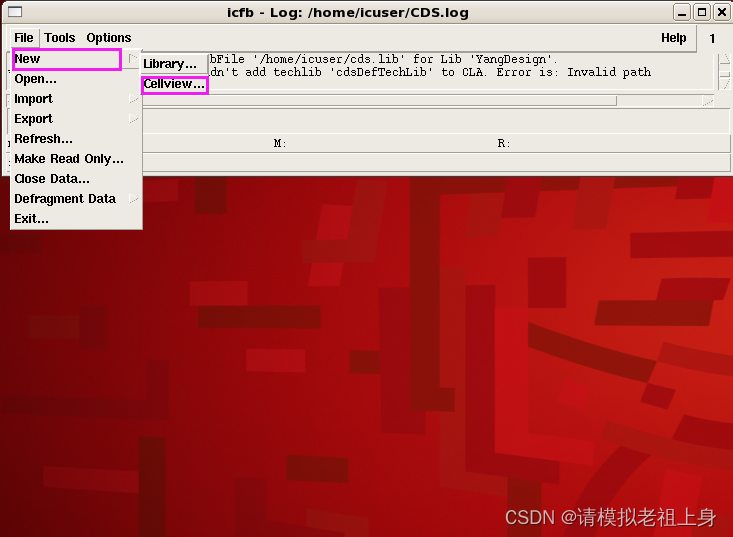

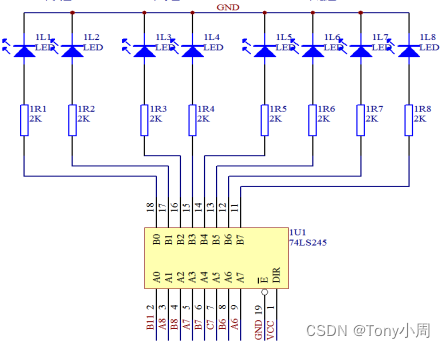

1.新建“cell view”,放置元器件,绘制schematic

图6 新建cell view |

图7 在图形界面中添加器件 |

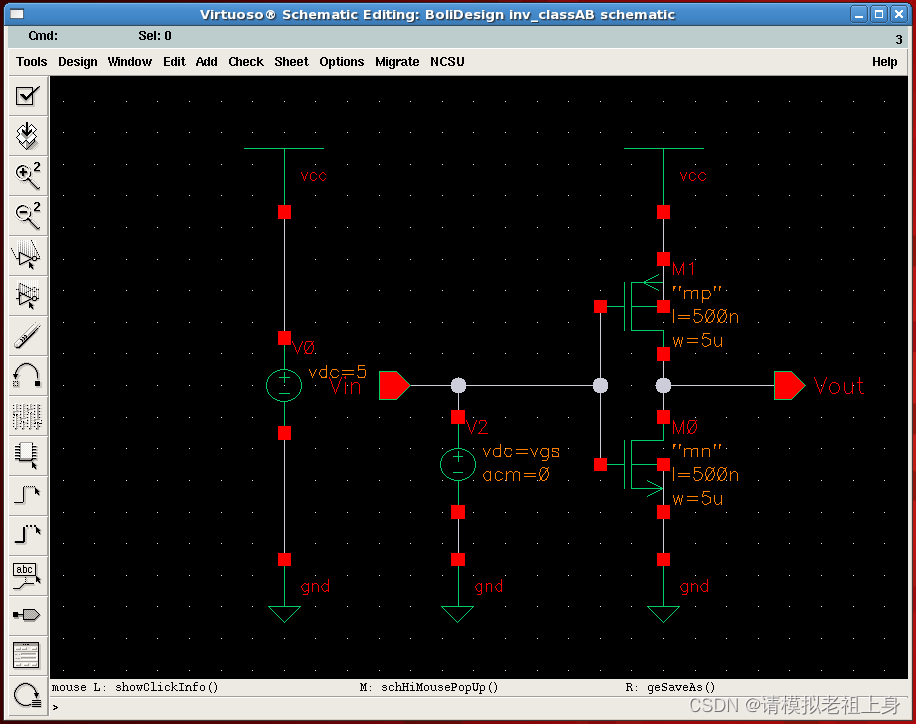

图8 依次添加器件并连接完成 |

图9 依次添加器件并连接 |

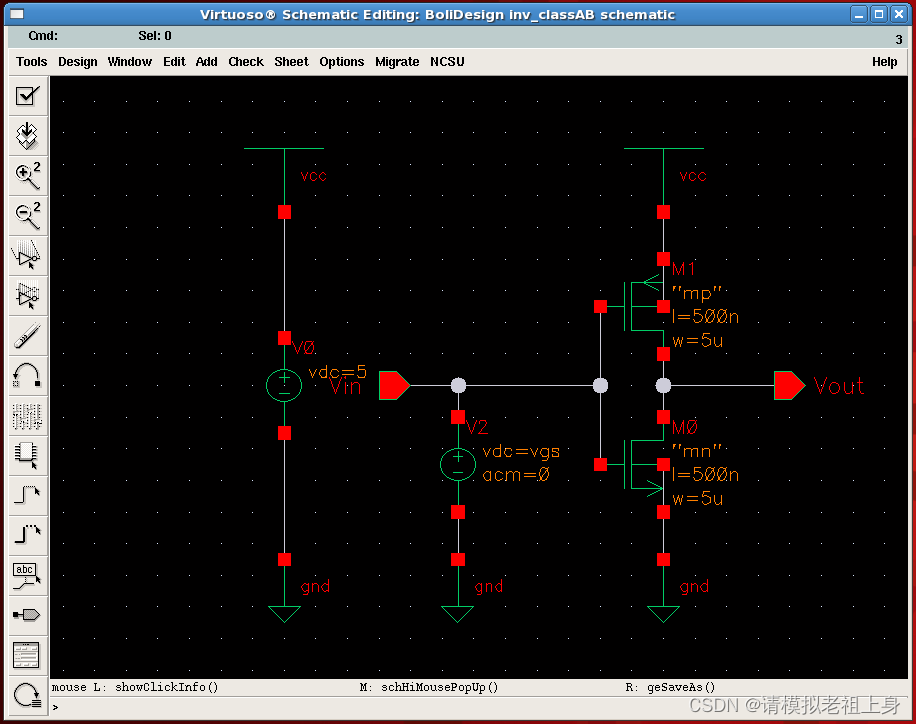

2.【实验一】CMOS反相器电路设计

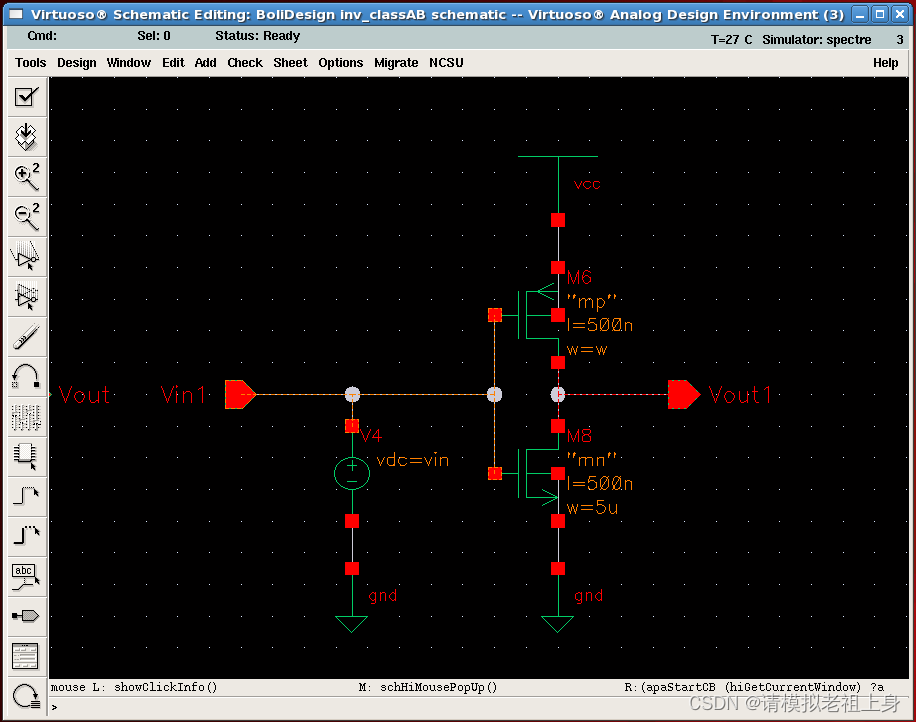

Schematic:

图10 CMOS 反相器原理图

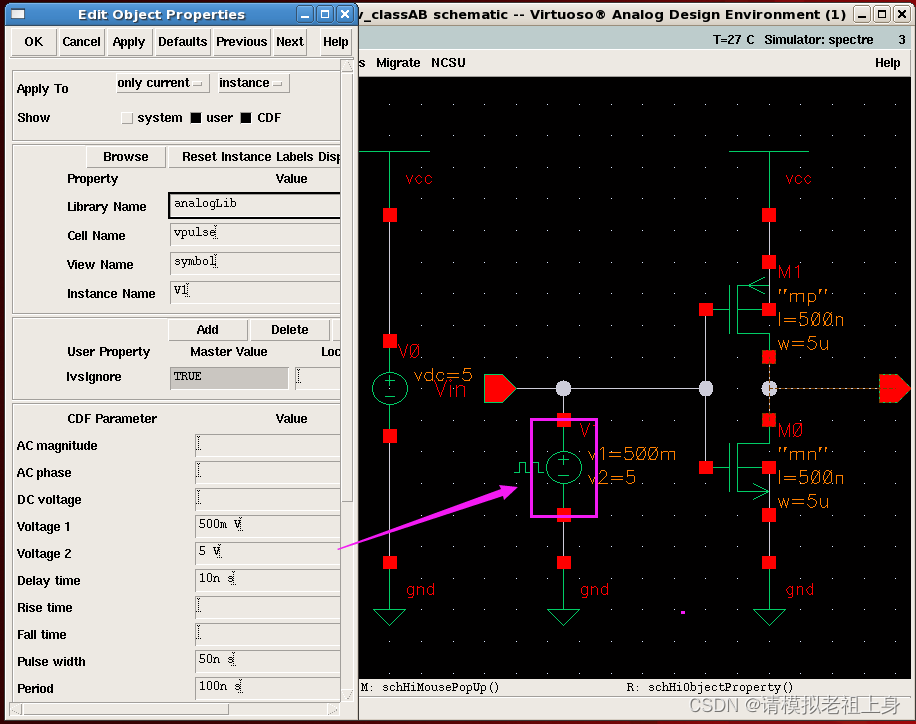

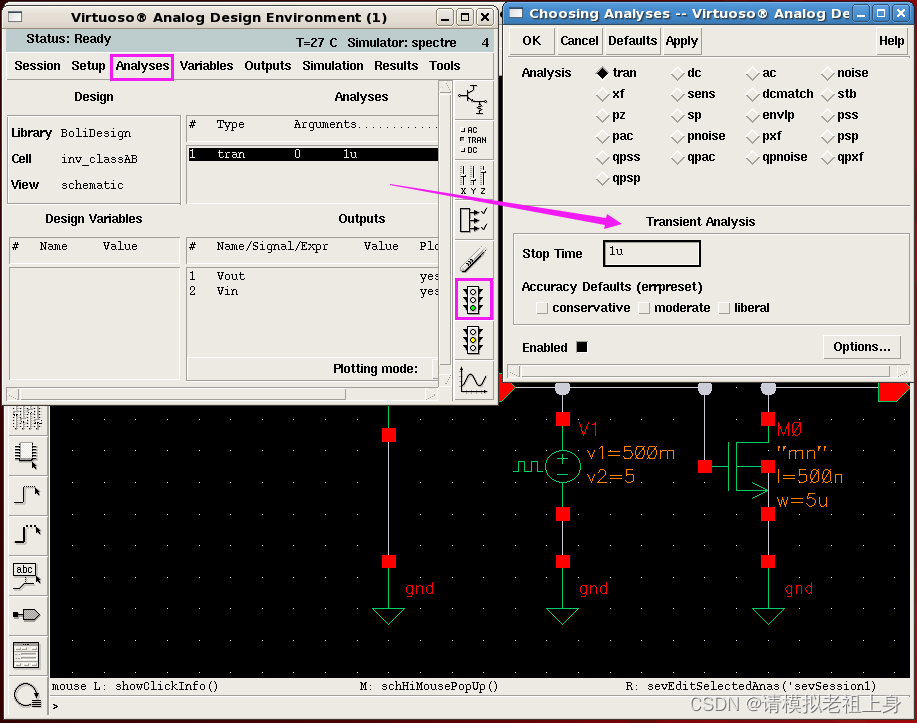

a. Trans 仿真

图11 方波发生器参数记录 |

图12 Trans仿真环境配置 |

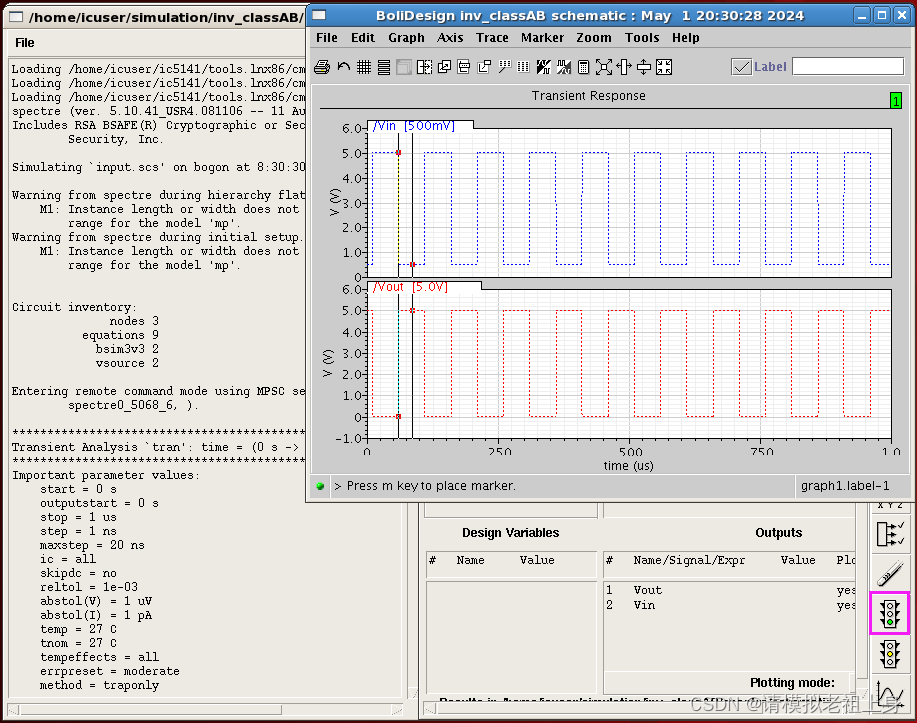

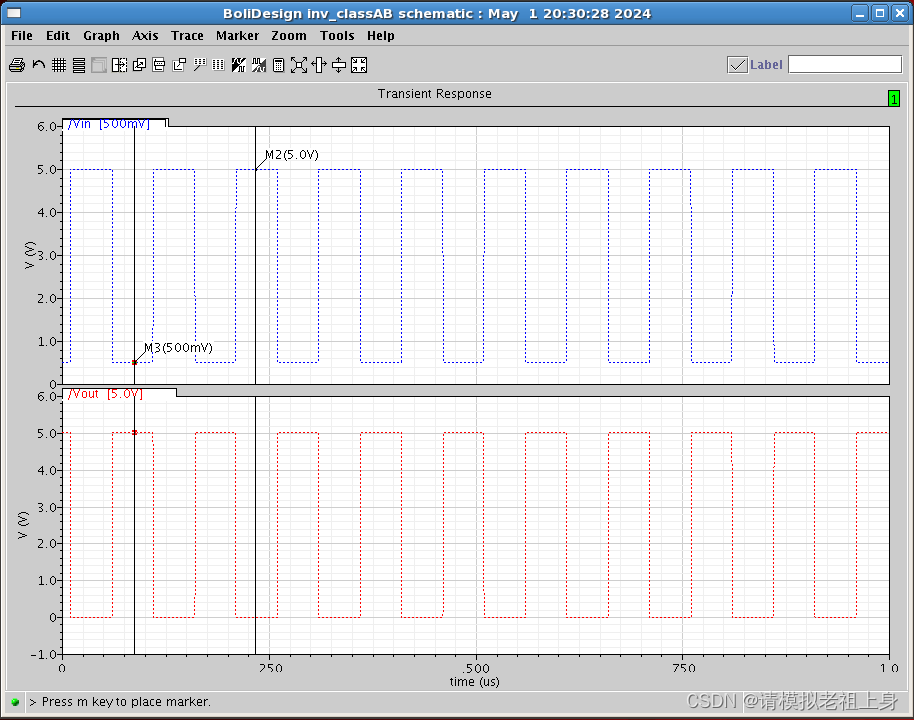

图13 仿真得到瞬态的输入输出曲线 |

图14 输入输出曲线 |

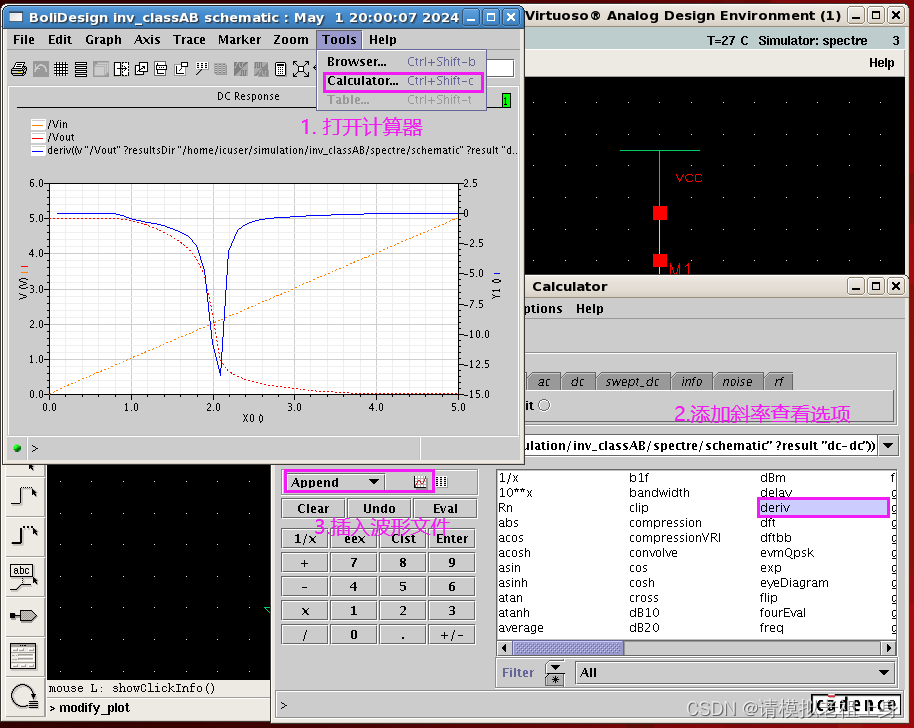

b. DC分析VTC

图15 DC仿真环境搭建 |

图16 DC_VTC曲线输出情况 |

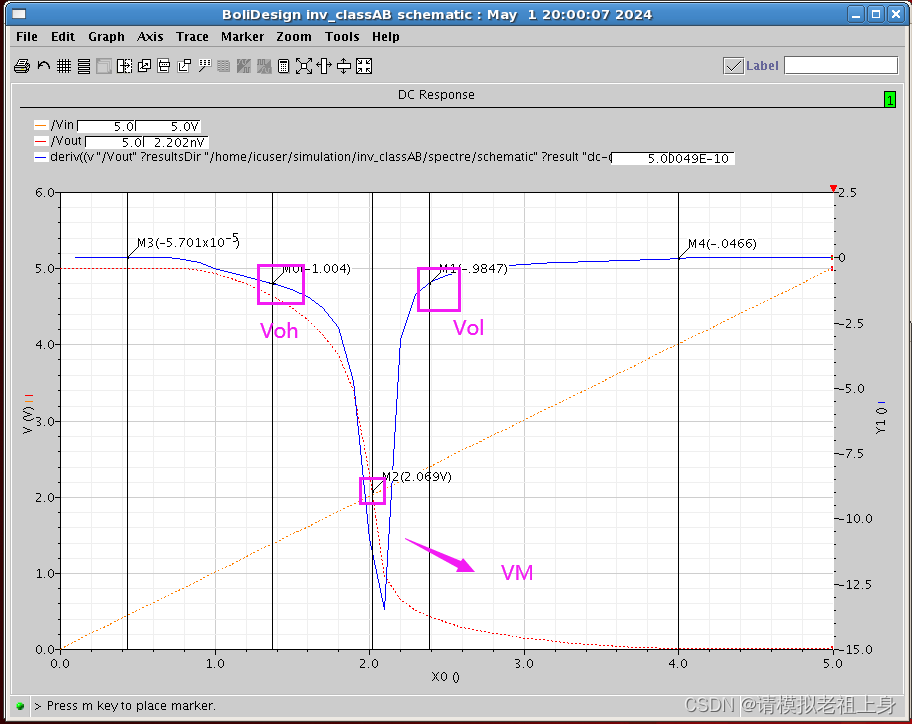

图17 插入Vout的斜率曲线,寻找VOL,VOH |

图18 VTC曲线重要节点展示 |

【备注】Vm=2.069,VOH=1.37,VOL=2.387

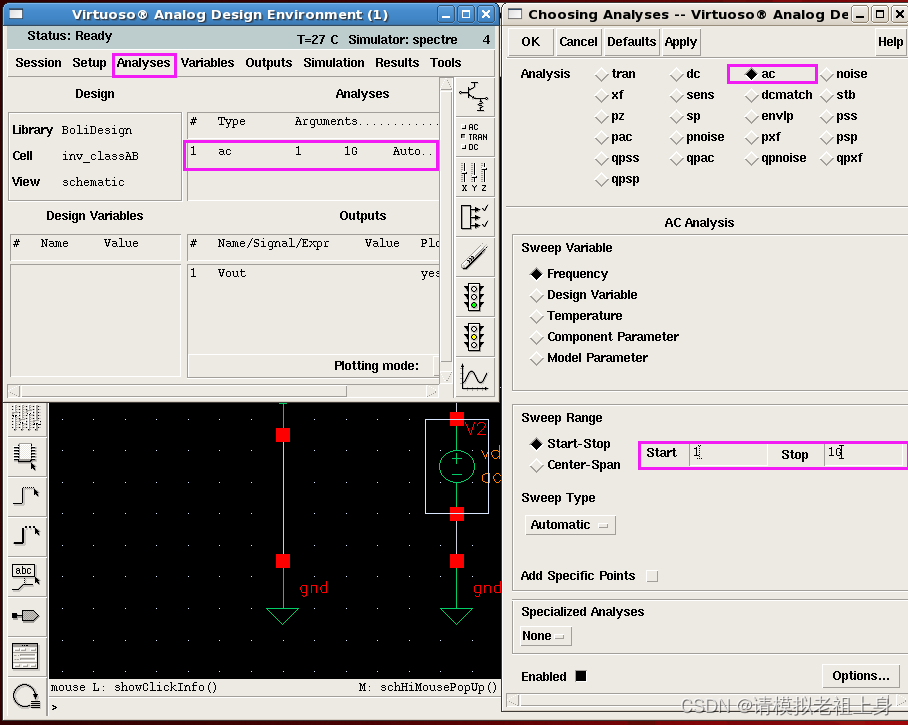

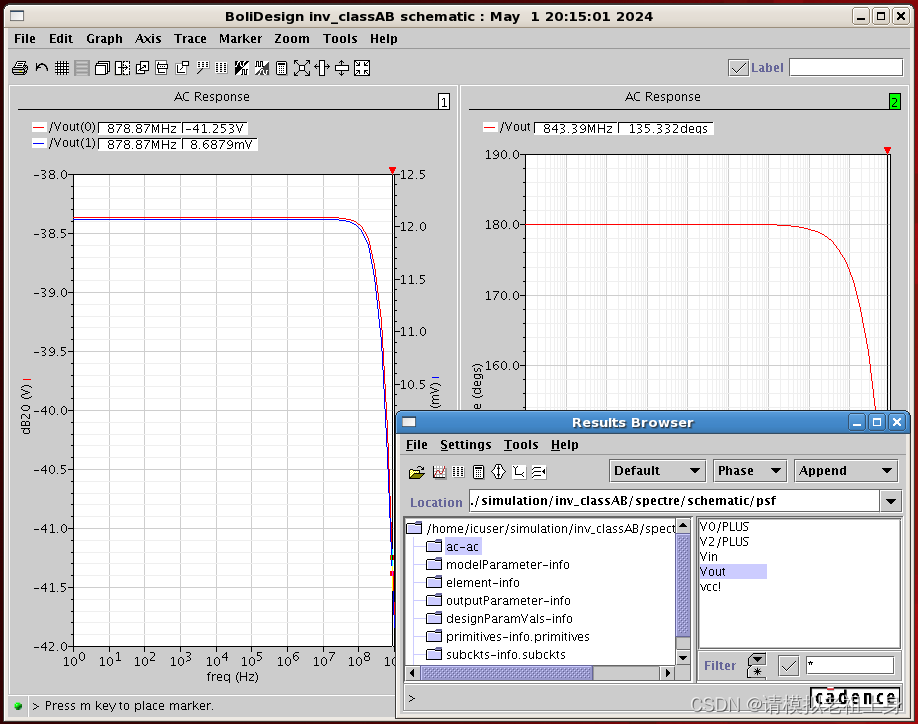

c. AC分析

图19 AC仿真环境搭建 |

图20 幅频特性曲线输出情况 |

图21 导出幅频特性与相频特性曲线 |

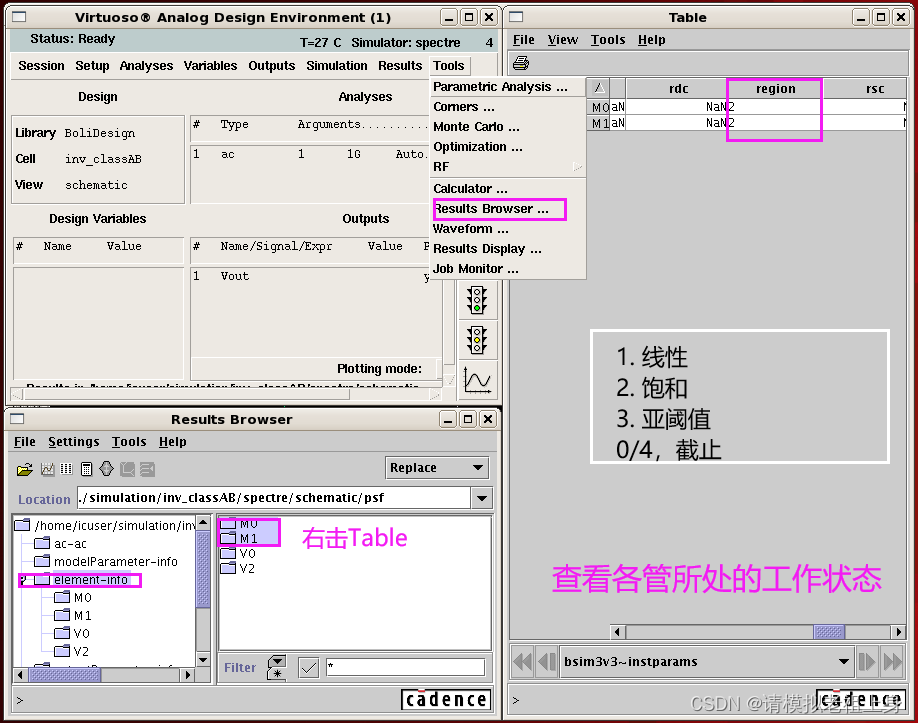

图22 查看电路各个MOS管所处的工作区 |

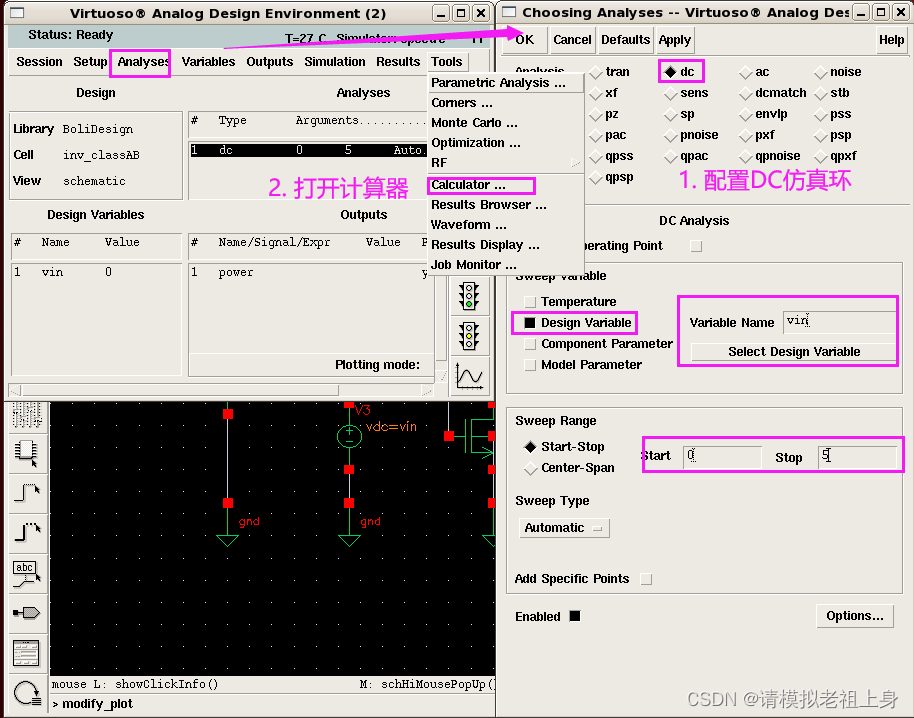

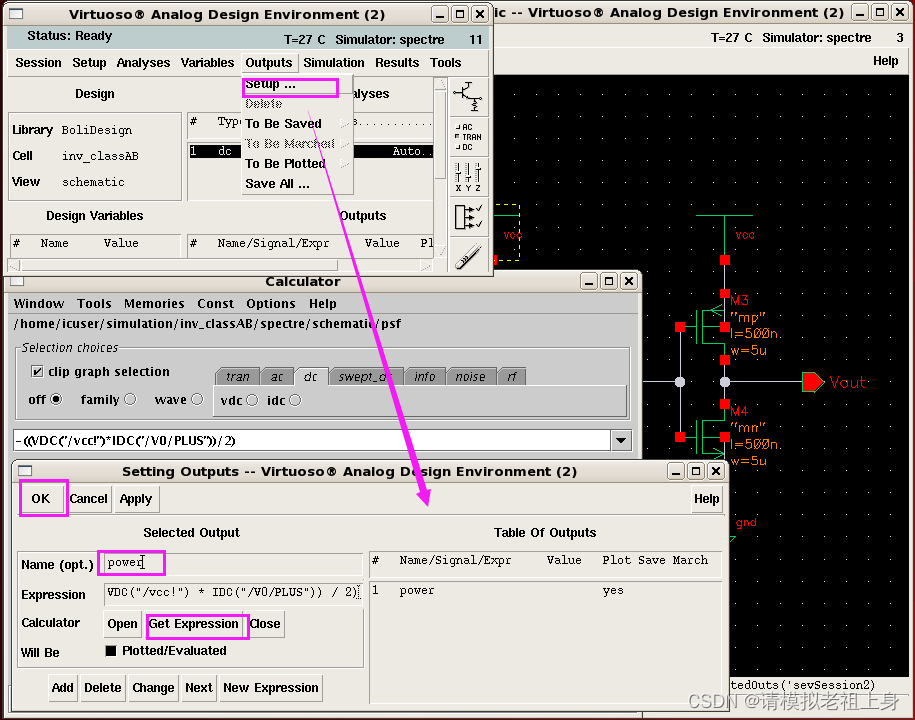

d. 静态泄露功耗

图23 静态泄露功耗仿真电路图 |

图24 DC仿真环境搭建 |

图25 导入静态功耗表达式到输出端 |

图26 仿真得到开关过程中的静态泄露功耗 |

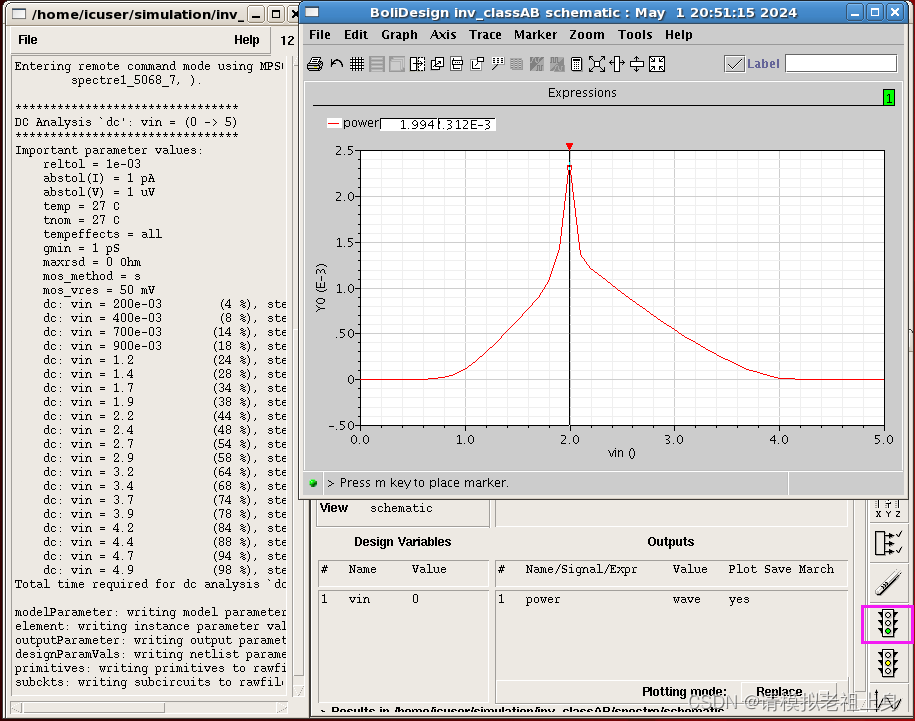

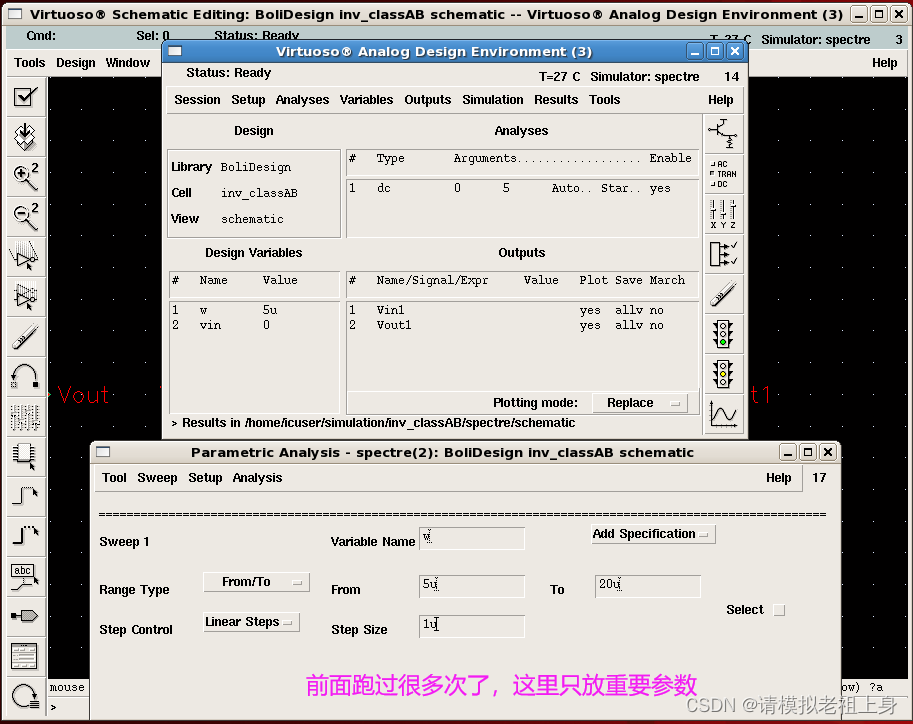

3.【实验二】改变MOS的栅宽之比,探究匹配对噪声容限的影响

Schematic:

图27 设置栅宽为参数的反相器电路图

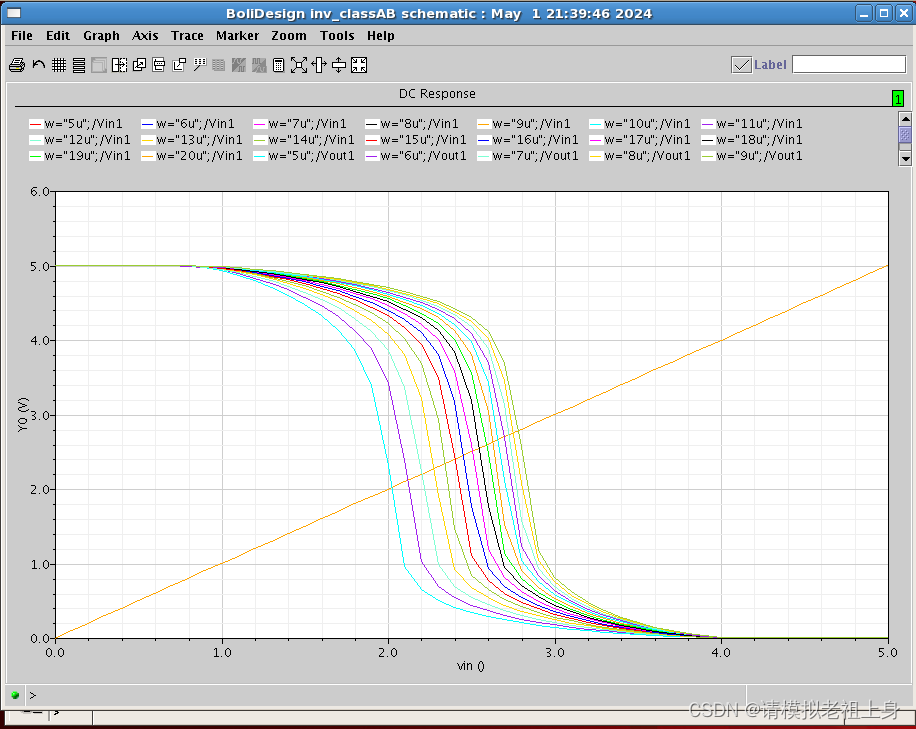

a. 栅宽对inv DVT曲线的影响

图28 DC仿真重要参数一览 |

图29 仿真得不同栅宽下的VTC曲线 |

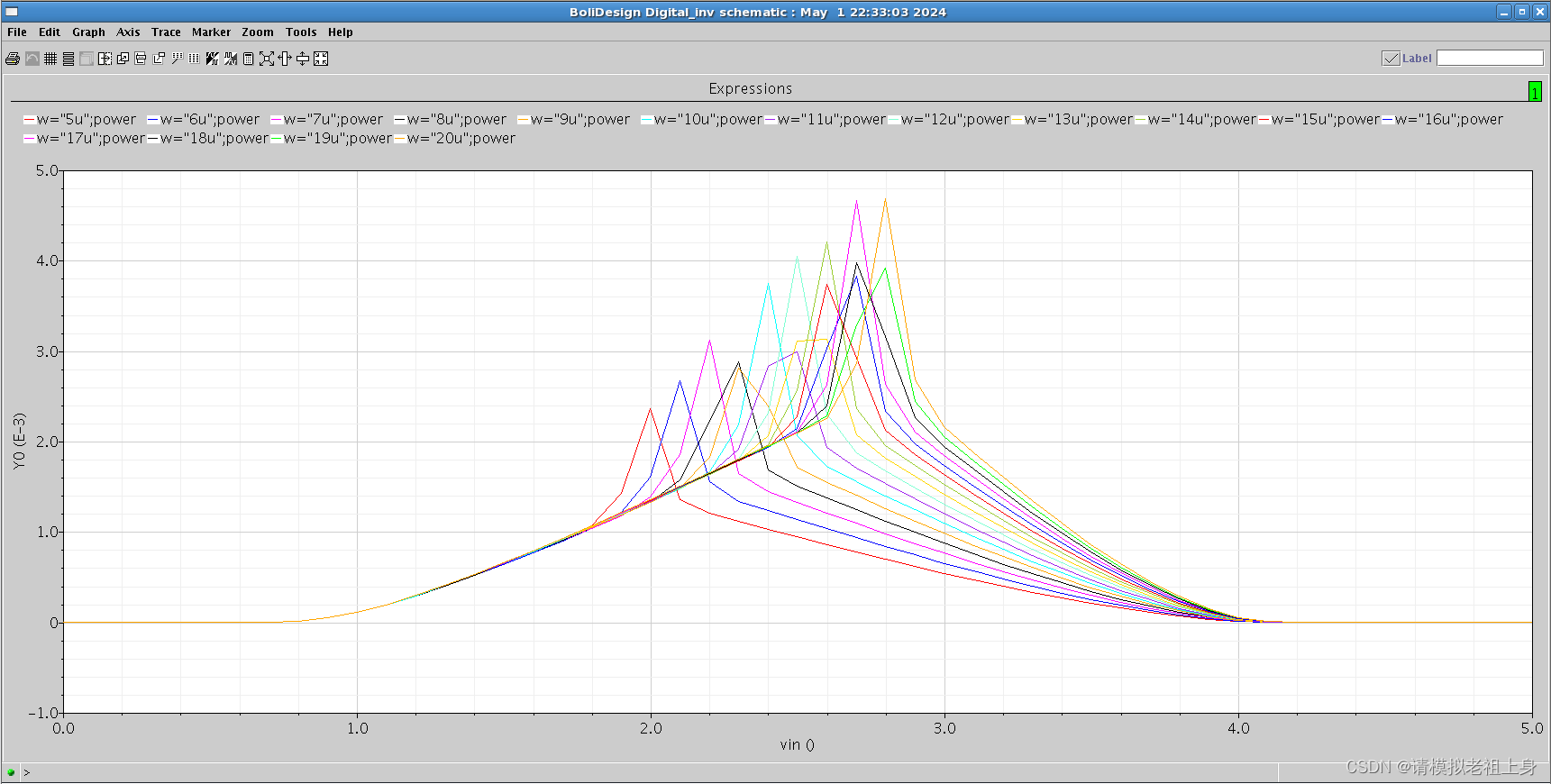

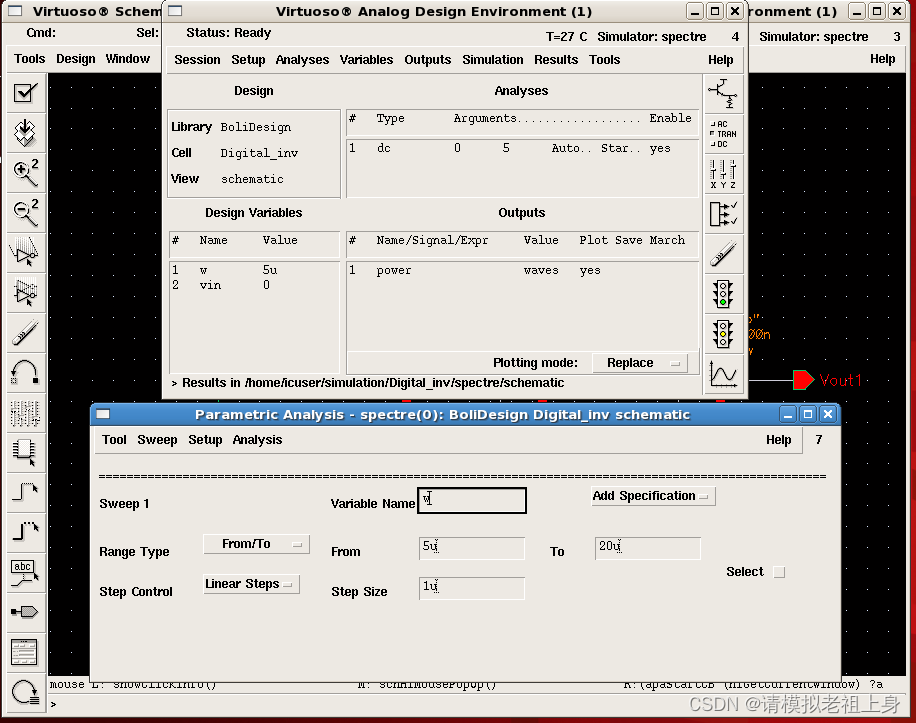

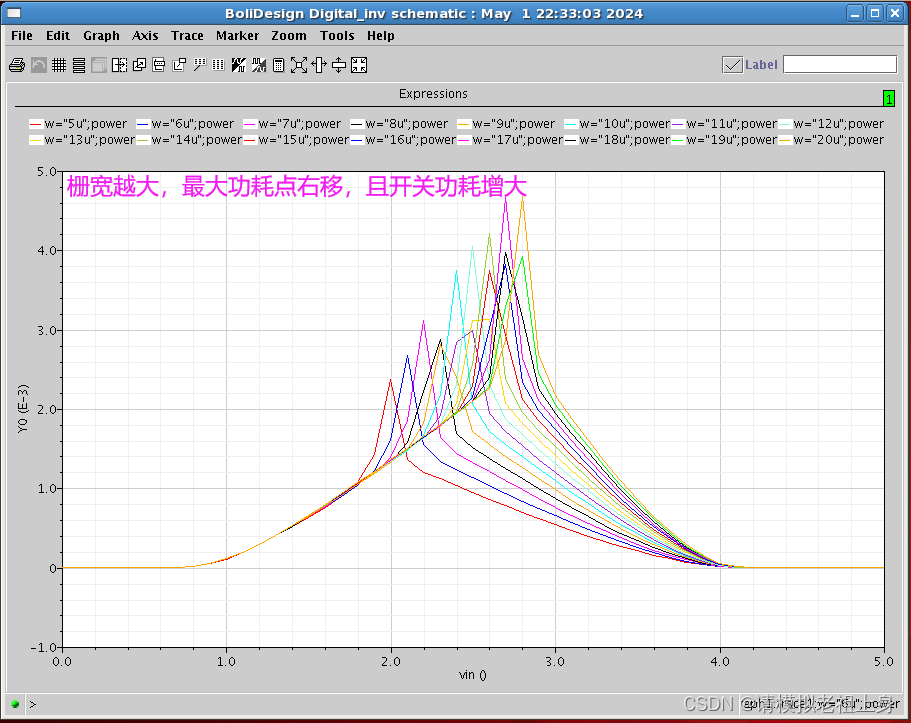

b.栅宽w对静态功耗的影响

图30C仿真重要参数一览 |

图31 仿真得不同栅宽下的静态泄露功耗 |

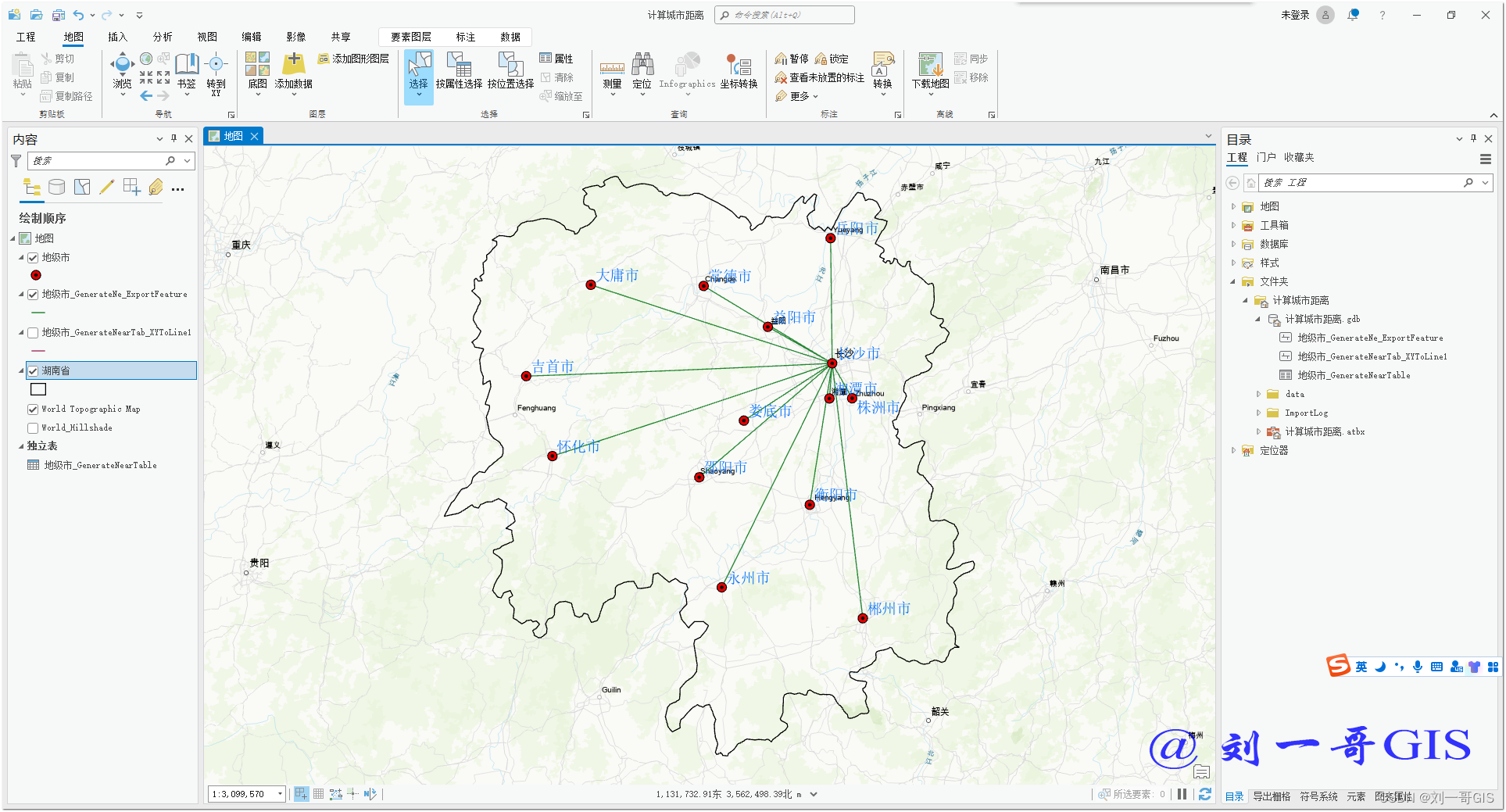

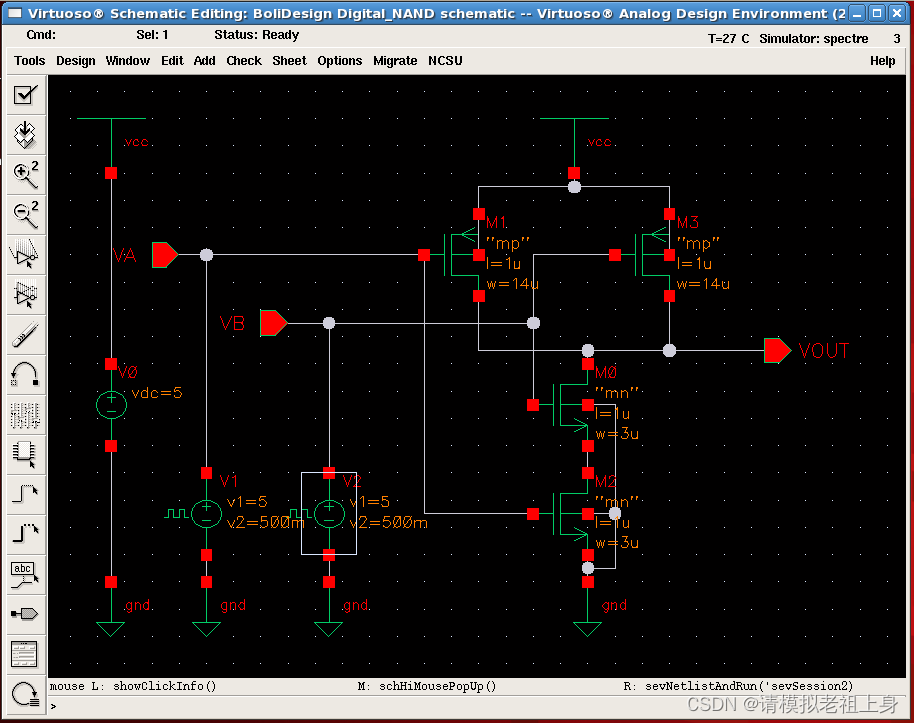

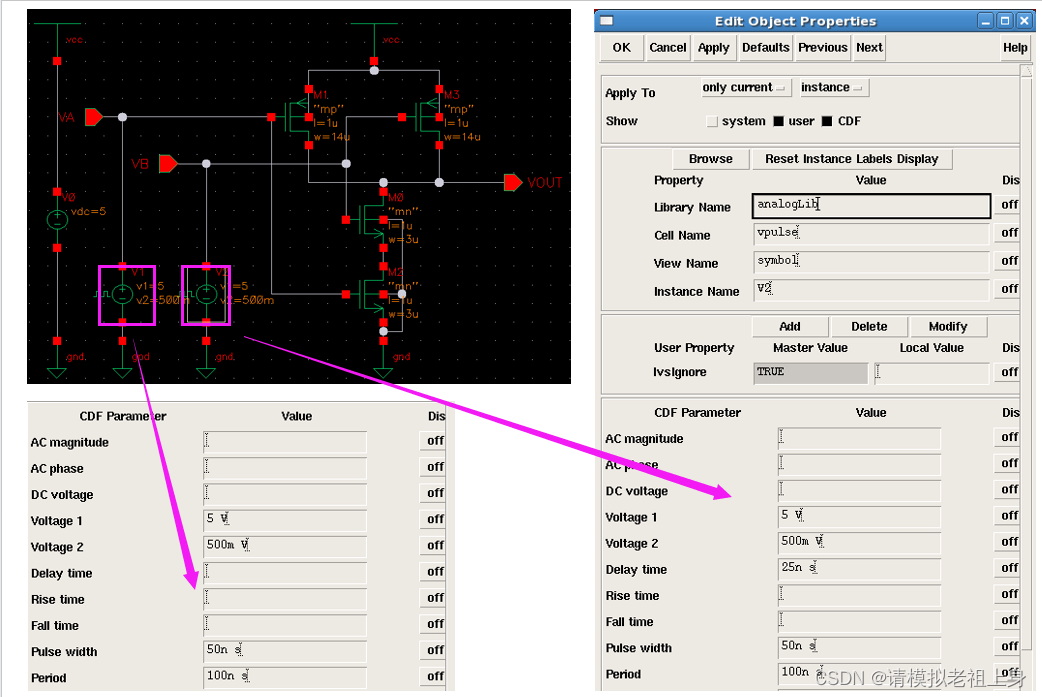

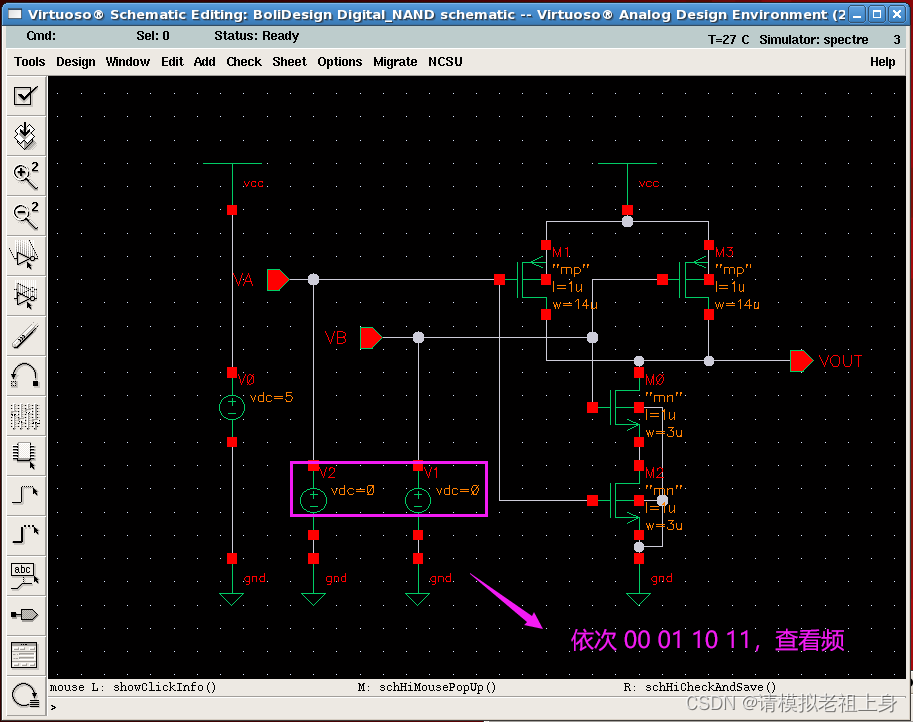

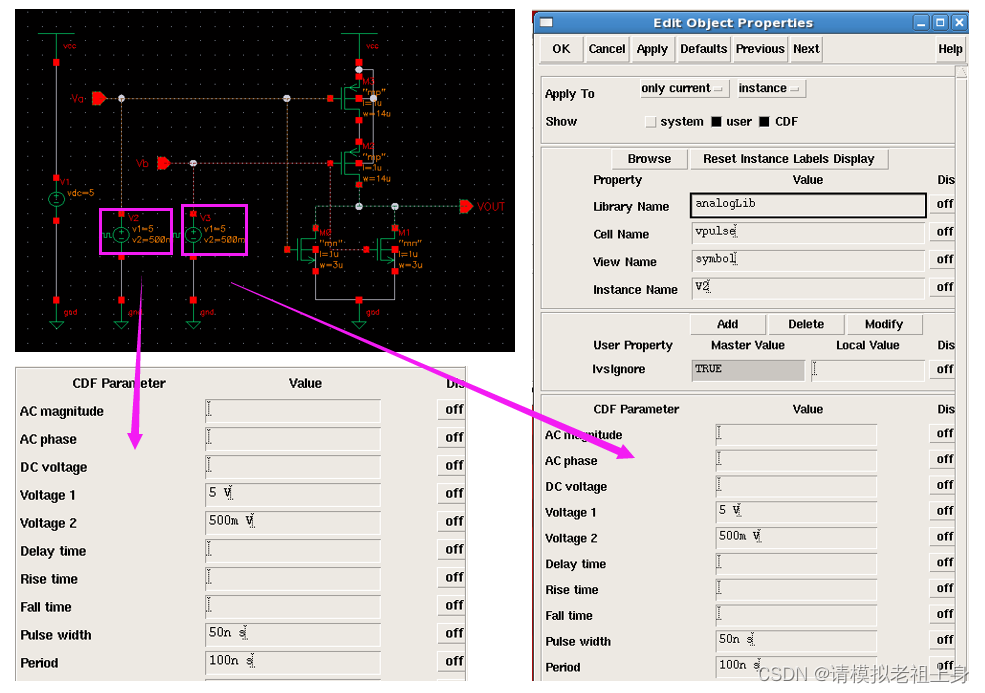

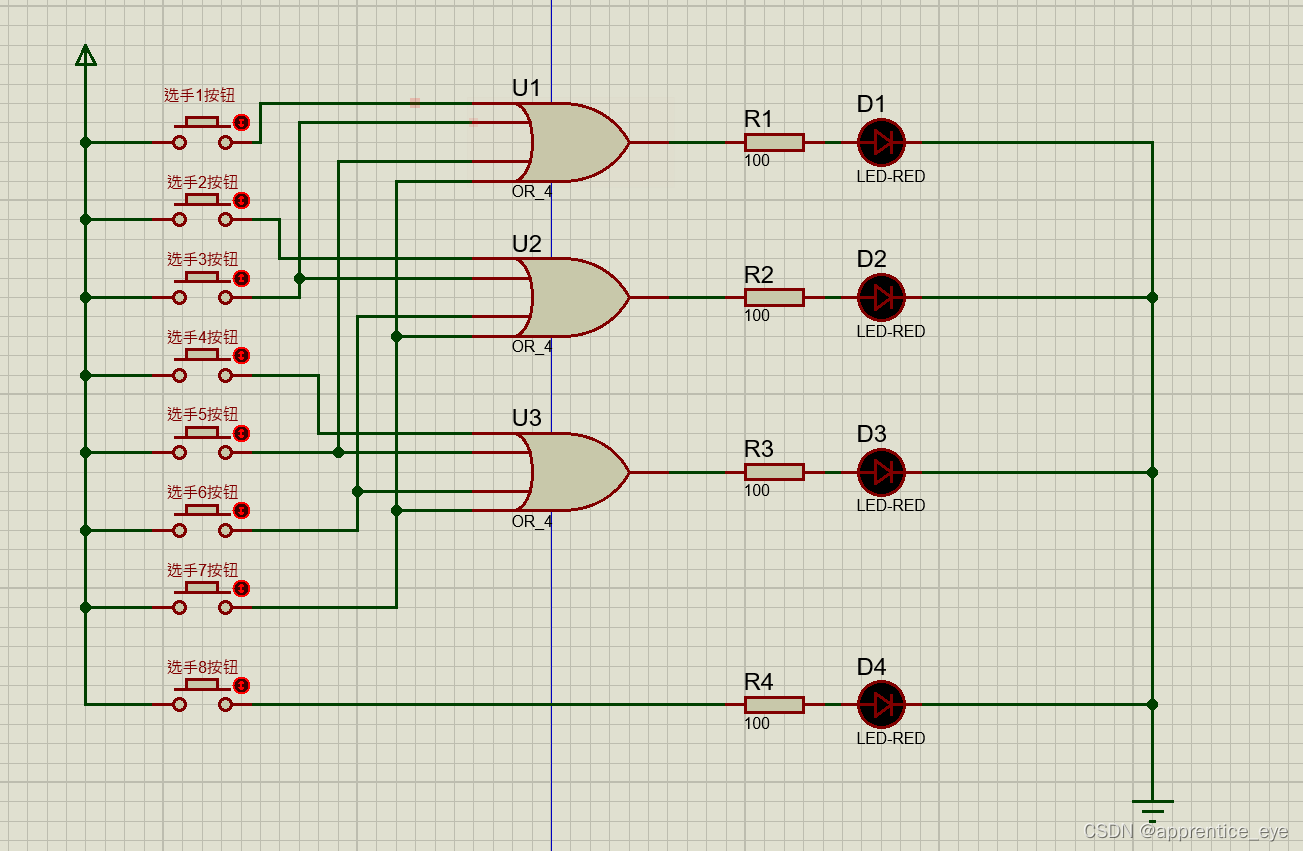

4.【实验三】与非门电路设计

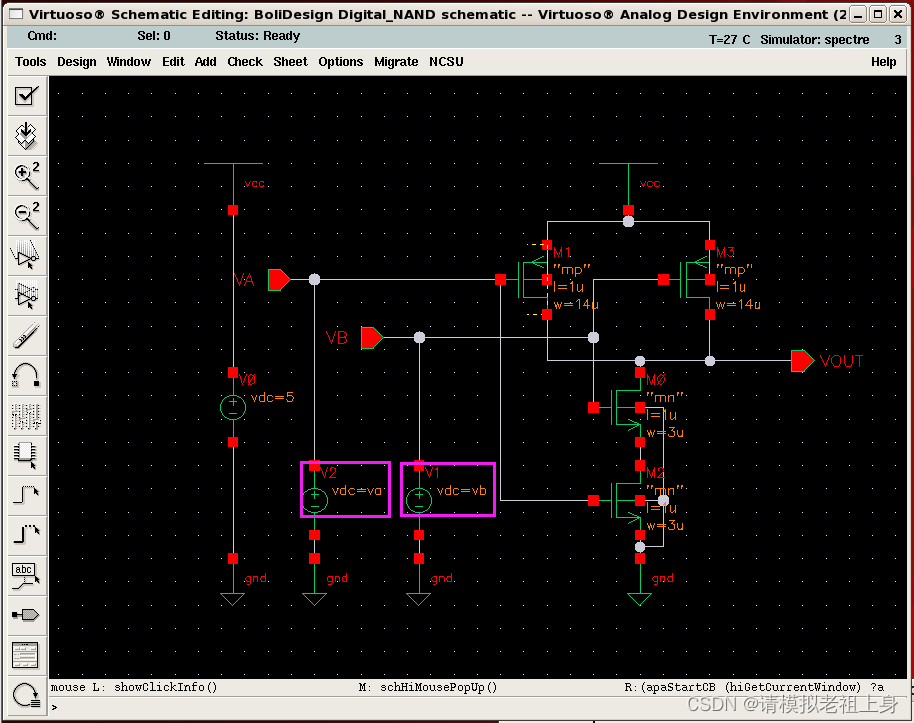

Schematic:

图32 CMOS与非门电路图

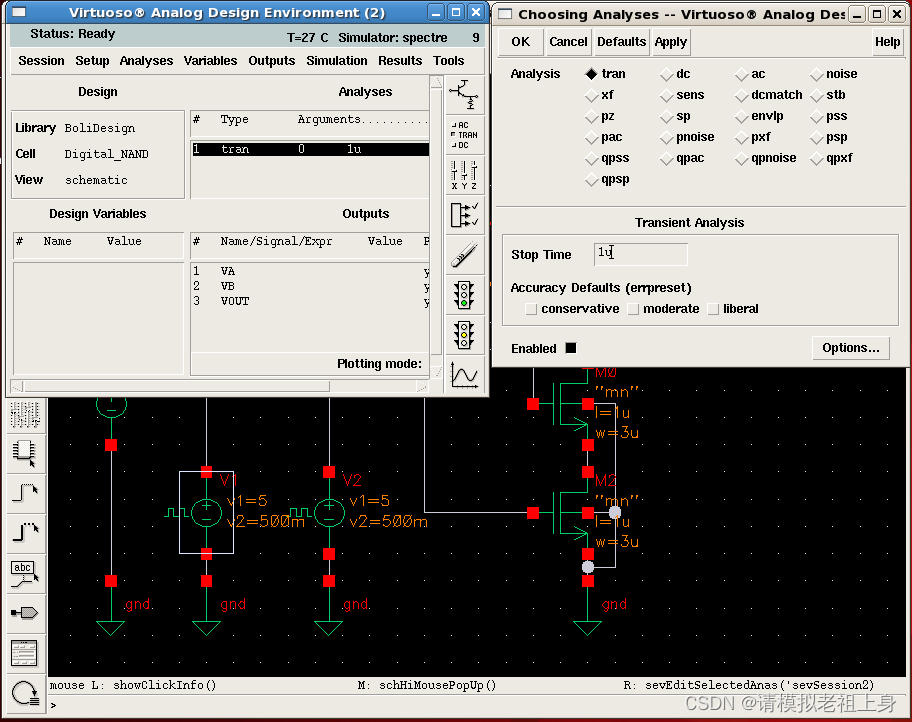

a. Trans 仿真

图33 Trans仿真信号源参数 |

图34 Trans仿真环境配置 |

图35 Trans仿真结果 |

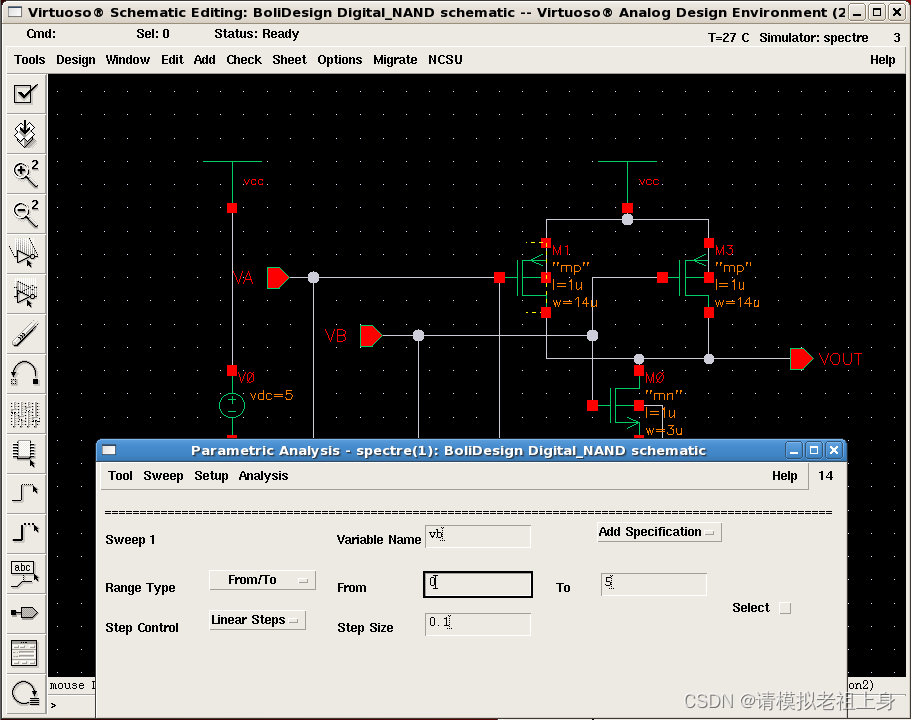

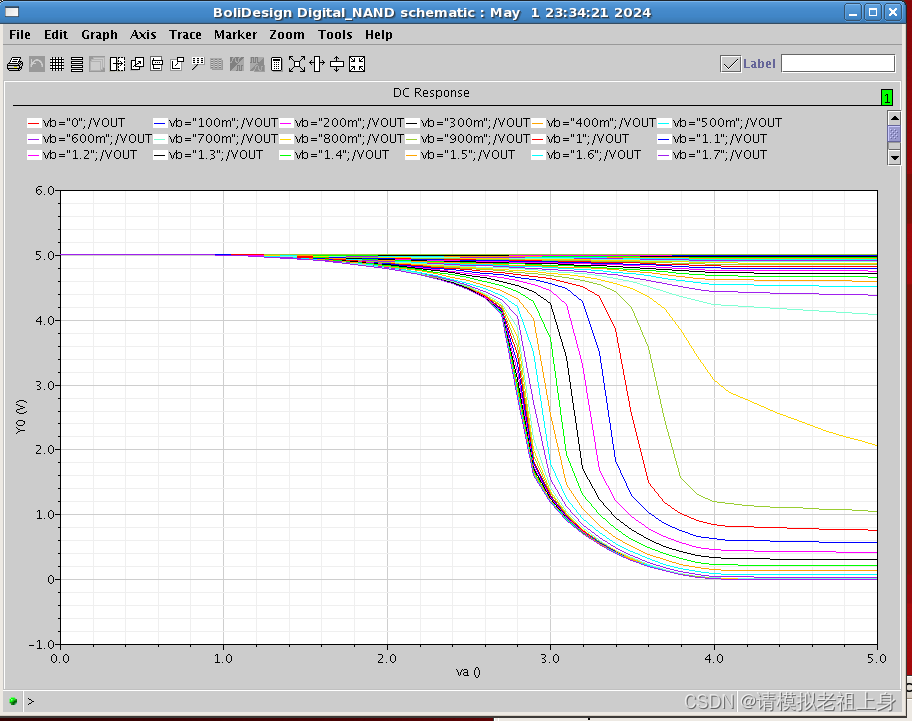

b. DC分析VTC

图36 DC仿真原理图 |

图37 DC仿真参数设置 |

图38 DC仿真参数扫描工具设置 |

图39 DC仿真结果 |

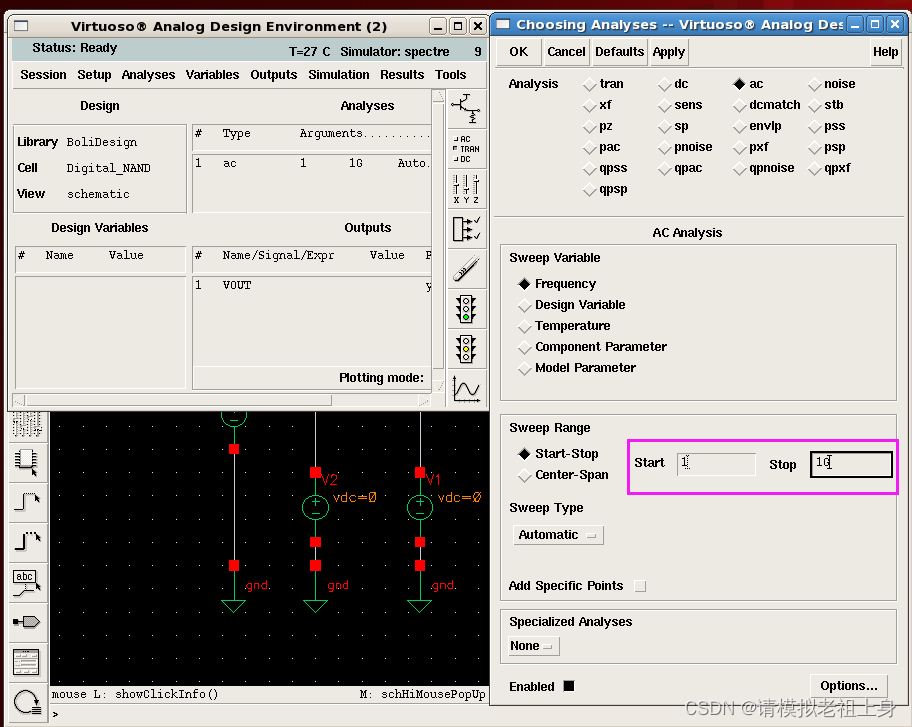

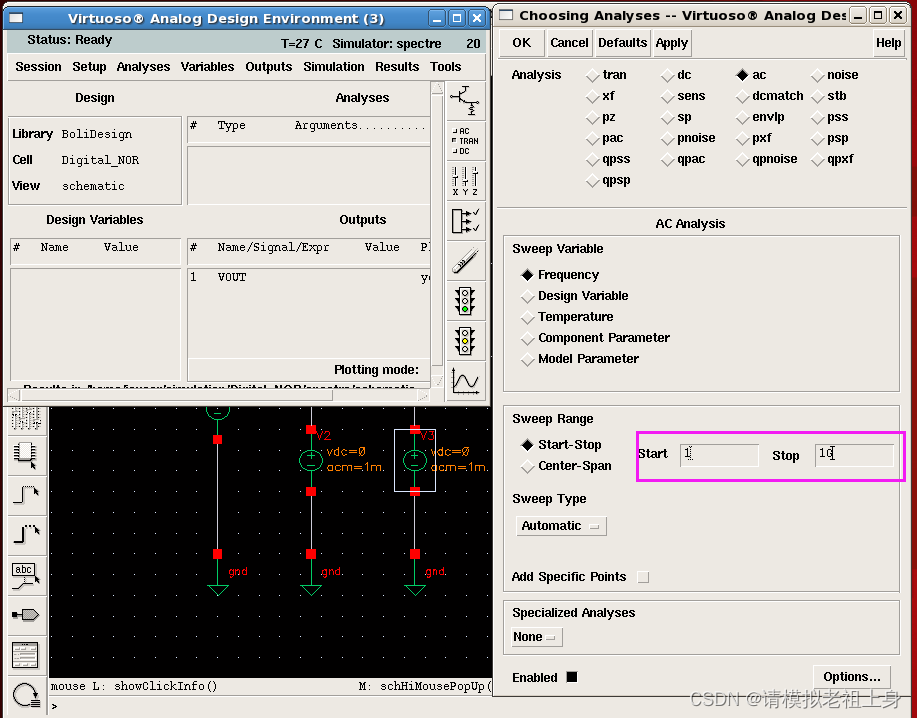

c. AC分析

图40 AC仿真原理图 |

图41 AC仿真参数设置 |

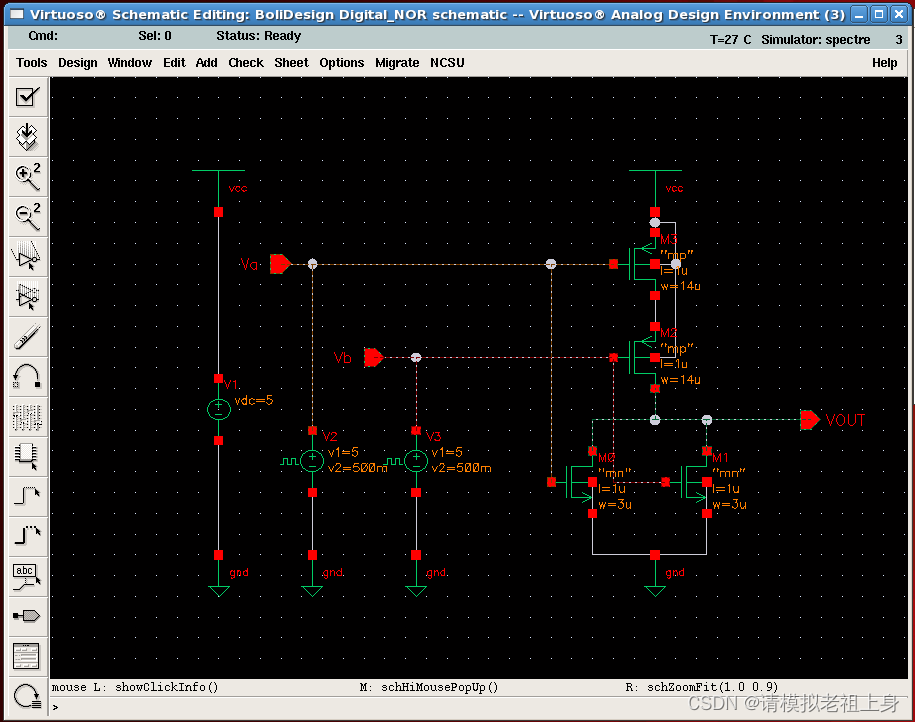

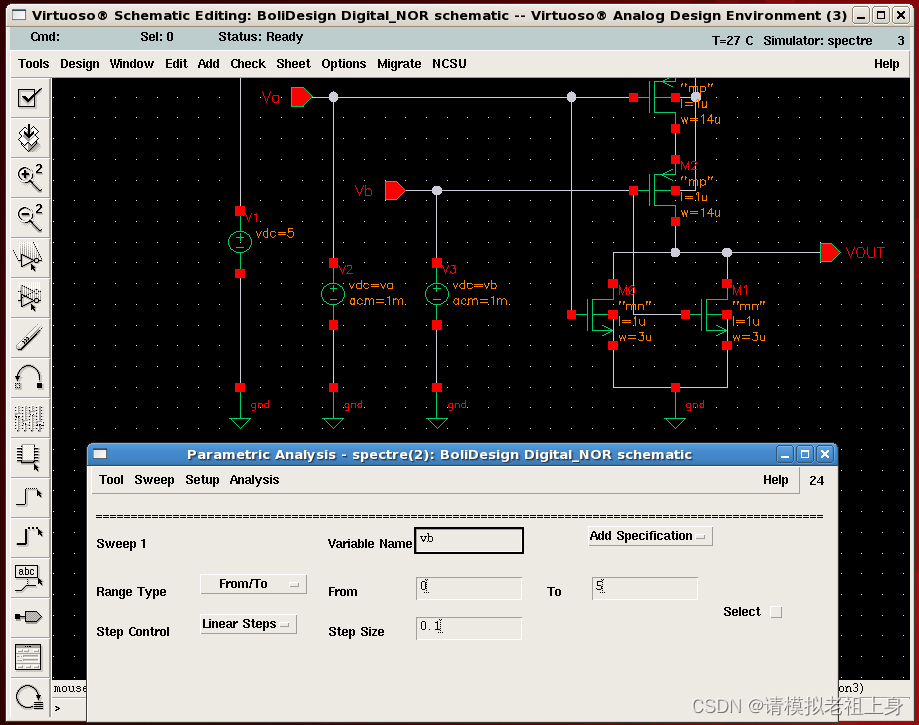

5.【实验四】或非门电路设计

Schematic:

图42 CMOS或非门电路图

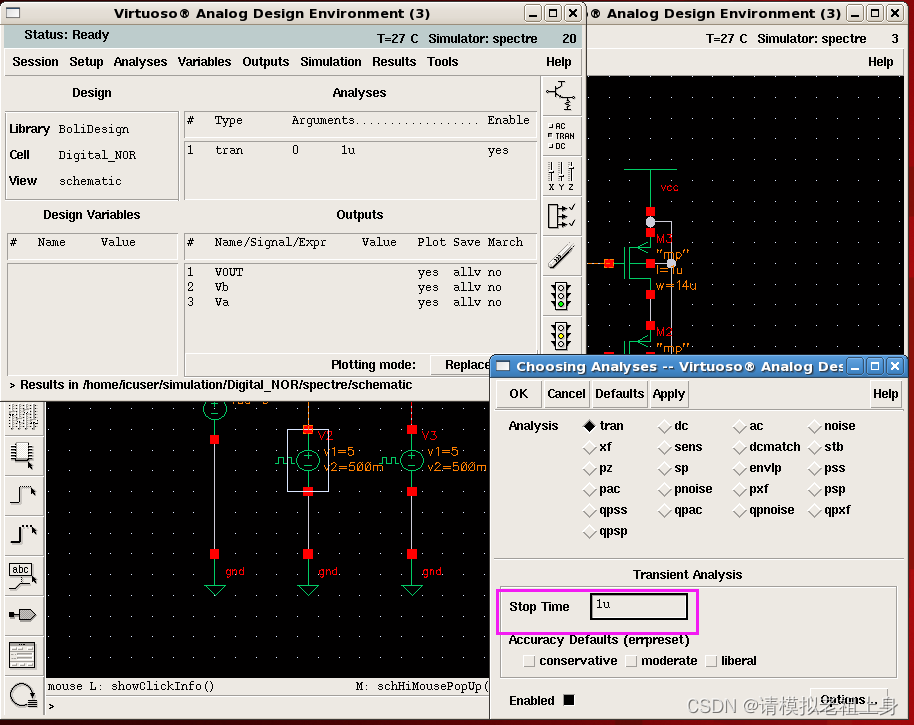

a. Trans 仿真

图43 瞬态仿真参数设置 |

图44 瞬态仿真环境配置 |

图45 瞬态仿真结果 |

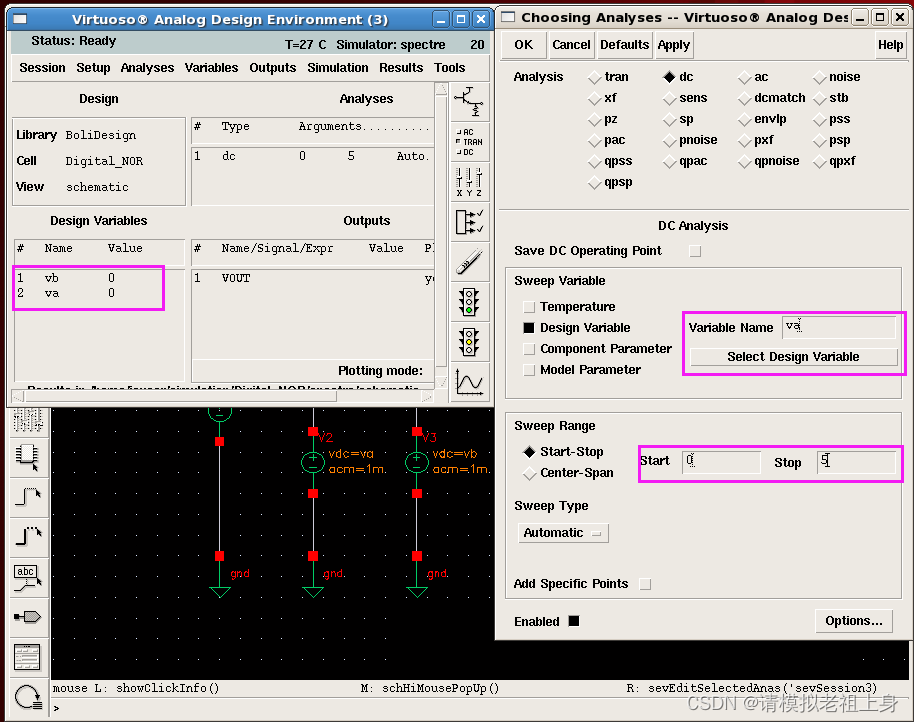

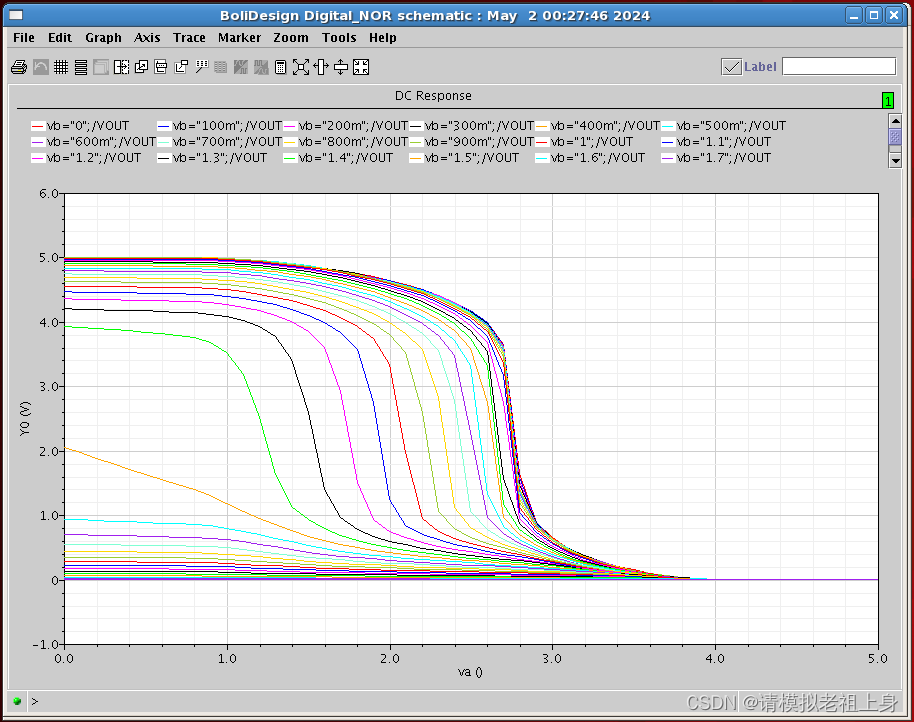

b. DC分析VTC

图46 DC仿真原理图 |

图47 DC仿真环境配置 |

图48 DC仿真参数扫描工具设置 |

图49 DC仿真结果 |

c. AC分析

图50 AC仿真原理图 |

图51 AC仿真参数设置 |

五、仿真结果及分析

1.【实验一】CMOS反相器电路设计

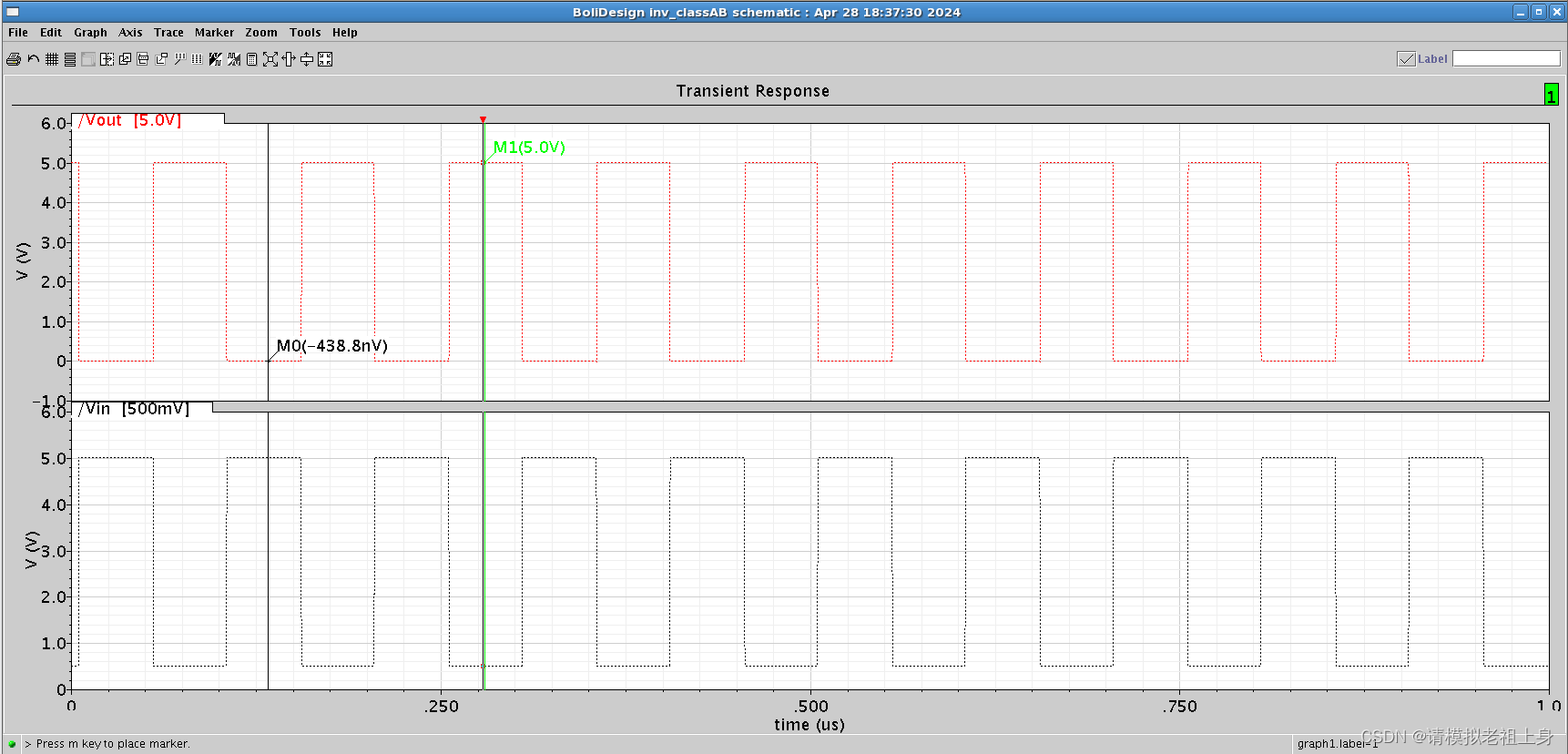

a. Trans 仿真

图52 CMOS反相器瞬态仿真结果

如图,当输入为高电平时,输出为低电平;输入为低电平时,输出为高电平,成功实现反相器的功能。

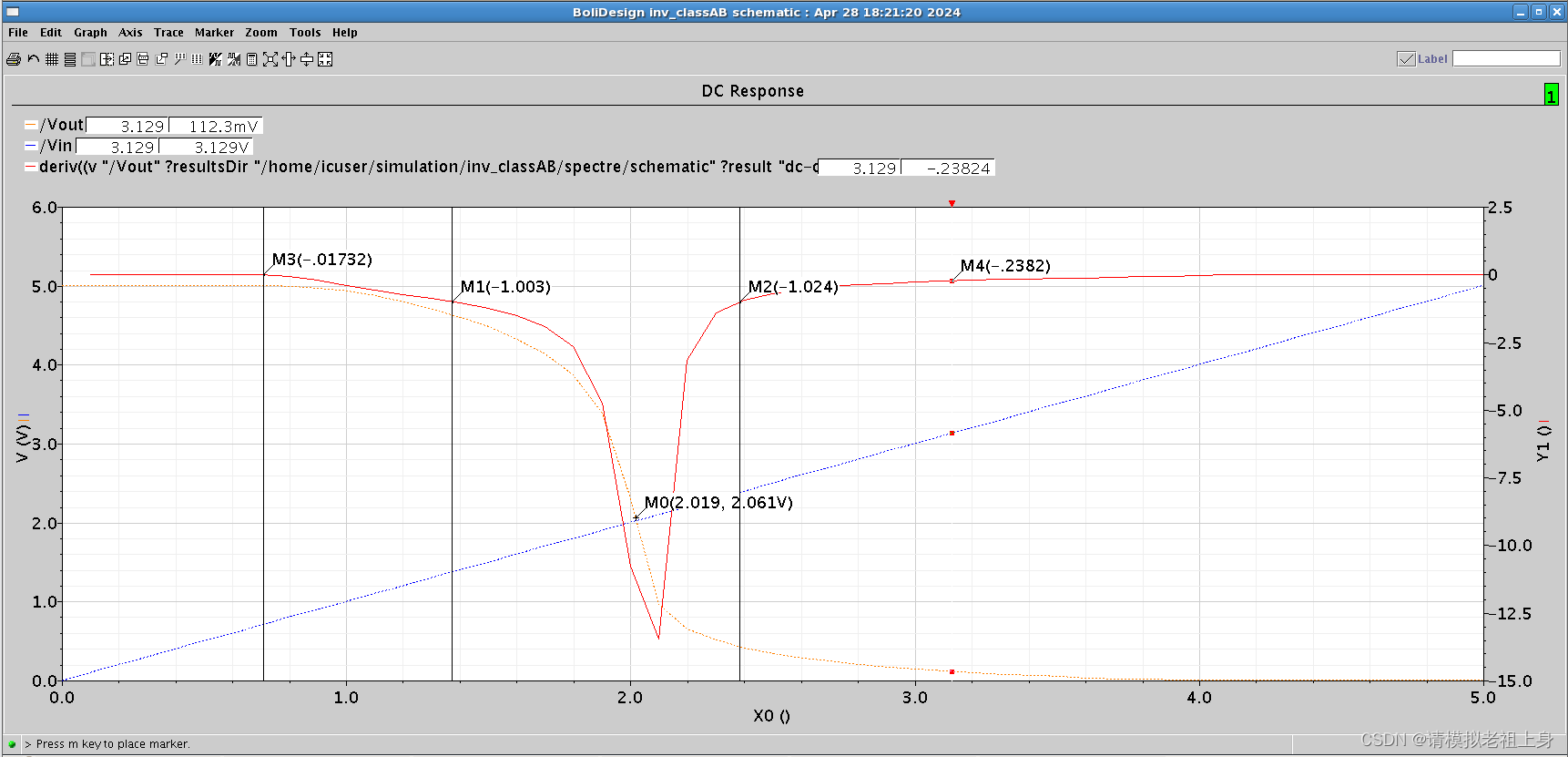

b. DC分析VTC

图53 CMOS反相器DC仿真各管的工作区

图54 CMOS反相器DC仿真结果(Vin,Vout,斜率)

如上图53可见,两个MOS管均处于饱和状态。在计算器中导出斜率曲线,当斜率为-1时,横坐标依次为Vih和Vil。如图54,Vil约为1.4V,Vih约为2.4V。Voh约为4.6V,Vol约为0.4V,则高电平噪声容限为NMh=Voh-Vih=4.6-2.4=2.2V;低电平噪声容限NML=Vil-Vol=2.4-0.4=2V。噪声容限均为正值且相对较大,说明抗干扰能力强,不易受到噪声干扰。

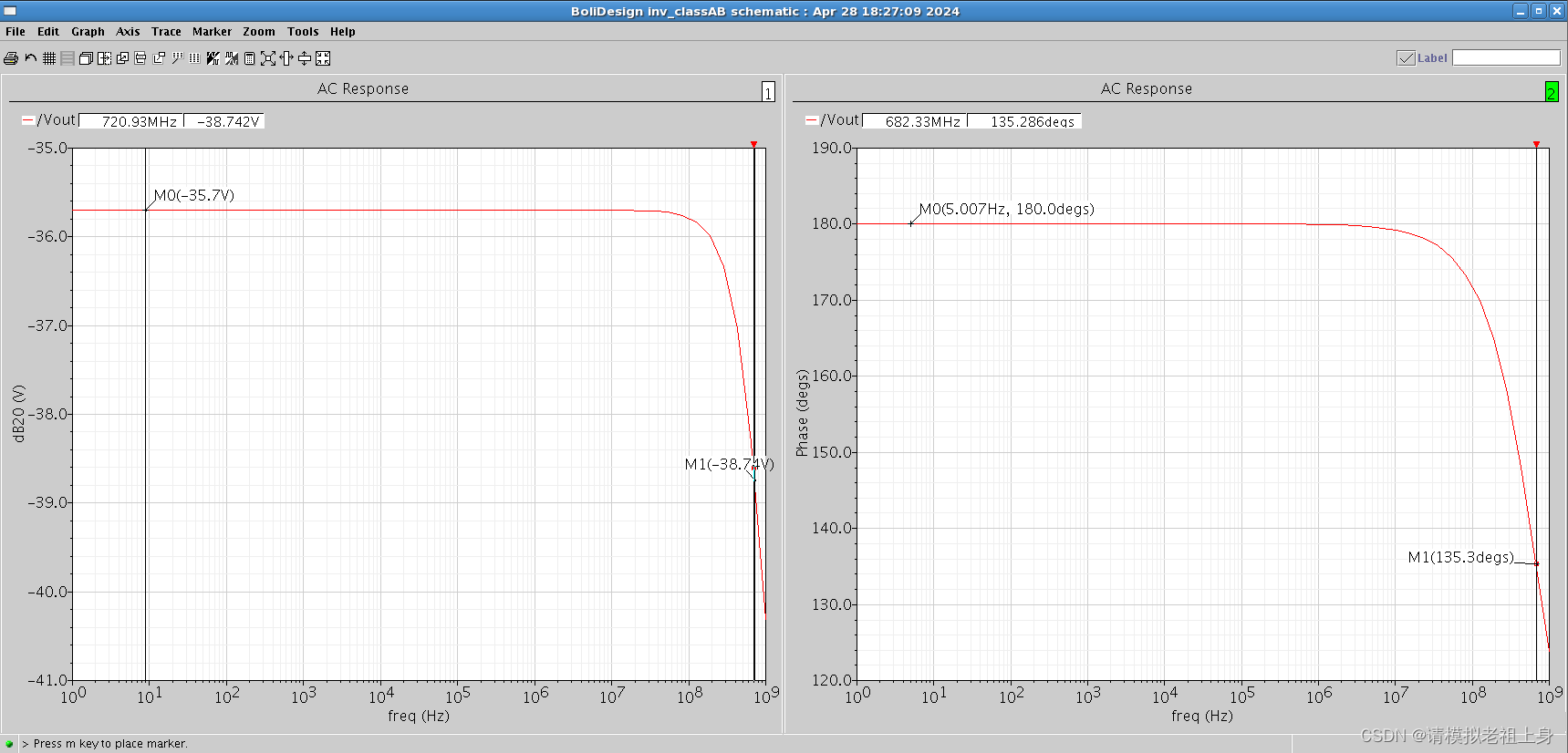

c. AC分析

图55 CMOS反相器AC仿真幅频特性曲线

图56 CMOS反相器AC仿真幅频特性曲线与相频特性曲线

如图,放大倍数大约为16.4倍,-3dB点频率为135M,此为一单极点系统,较为稳定。

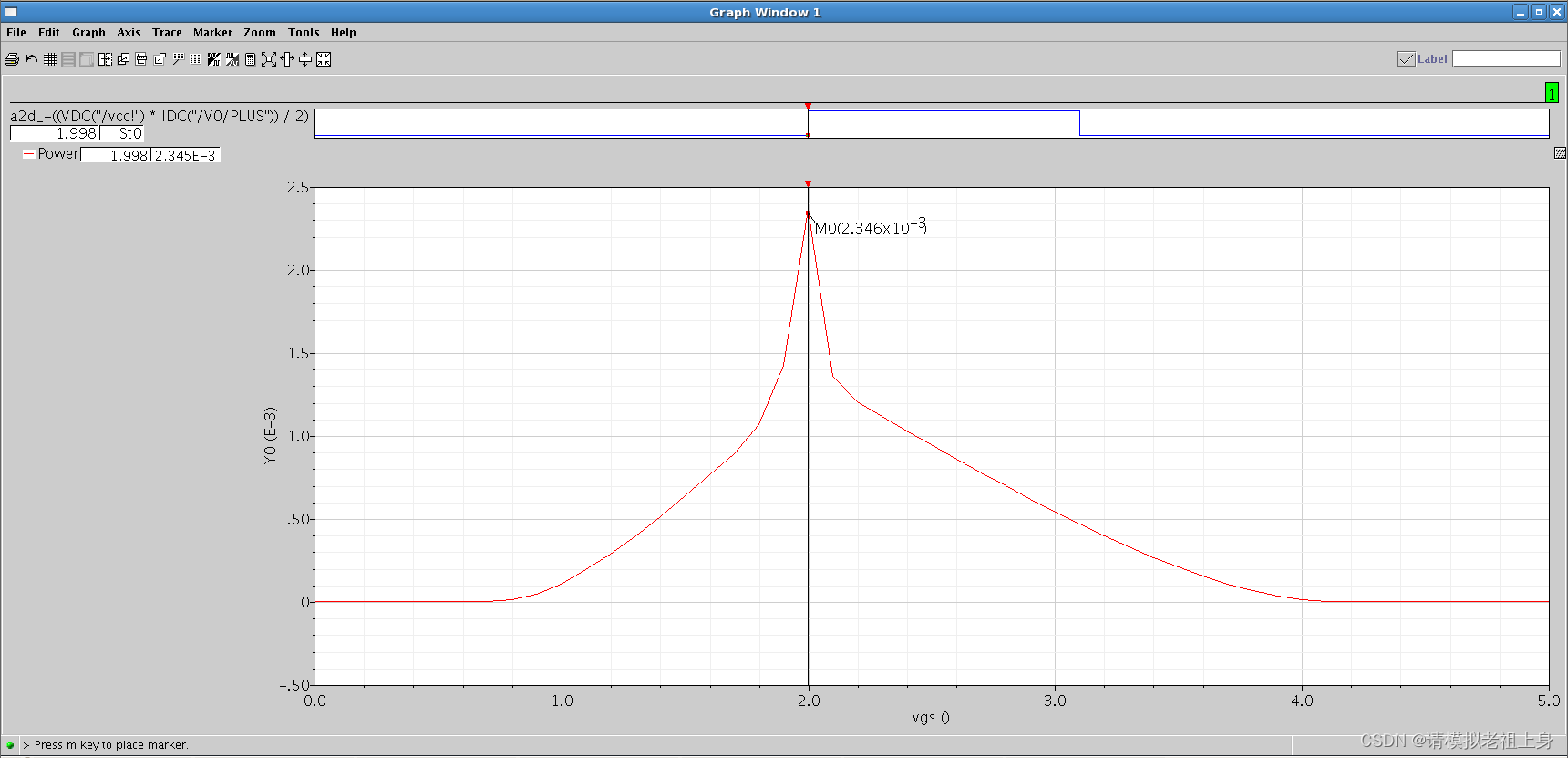

d. 静态泄露功耗

图57 CMOS反相器静态泄露功耗

当输入信号发生变化时,电路的电流会先增加后减小,当两个管子均处于饱和区时,电流达到峰值。此时输出点电压并不为零,所以存在一个很大的短路功耗,也就是此图峰值及周边区域。当只有一个管子导通,另一个截止时,电流为零,漏电极小,所以可以忽略不计,当一个饱和,一个线性时电路电流较小,电压较小,所以存在功耗,但功耗不大。

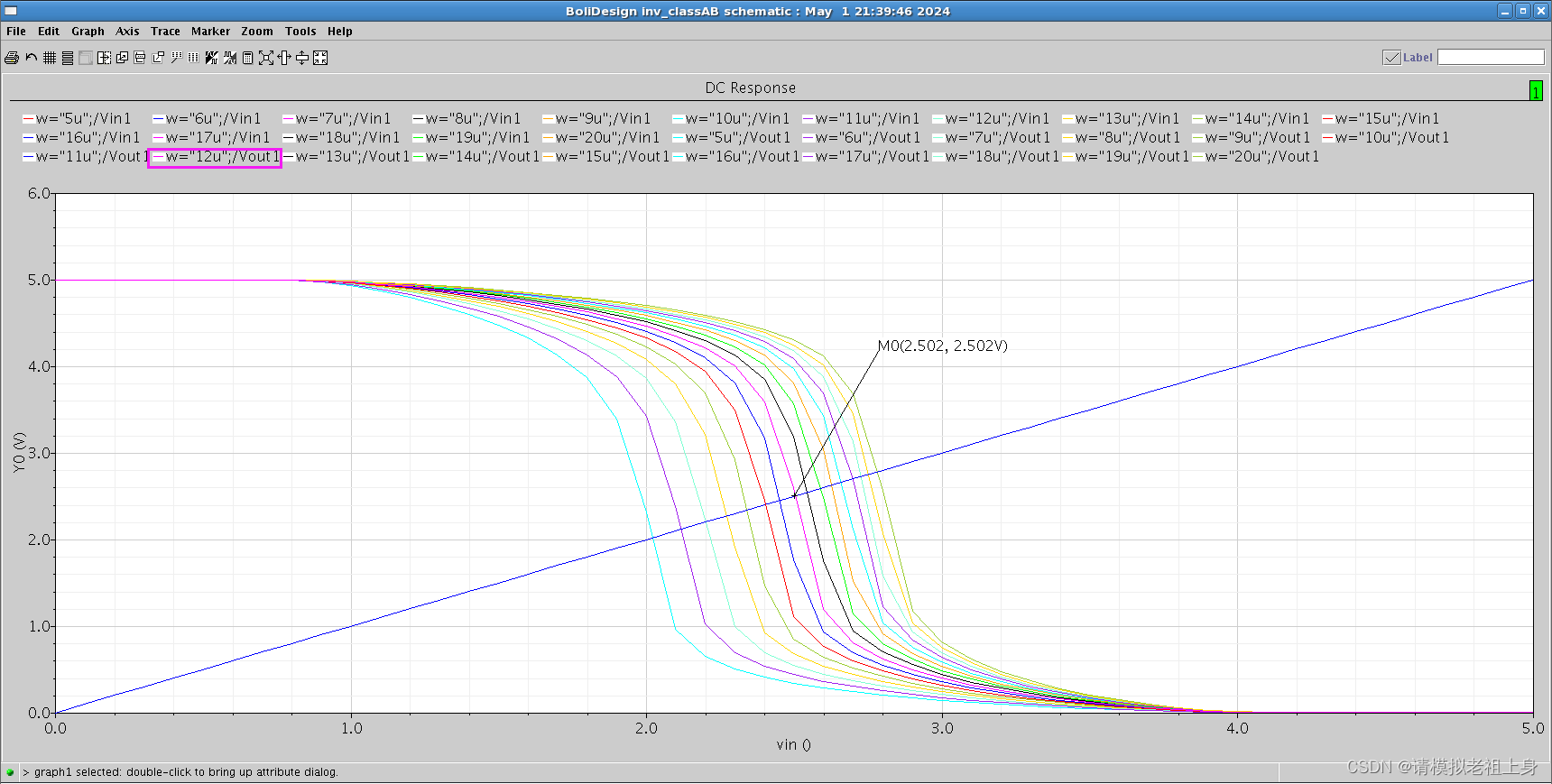

2.【实验二】改变MOS的栅宽之比,探究匹配对噪声容限的影响

a. 栅宽对噪声容限的影响

图58 栅宽对CMOS反相器DC仿真VTC曲线的影响

随着栅宽Wp的增大, 逐渐减小,曲线整体右移。当Voh,Vol不变时,Vih增大,Vil增大,NMh=Voh-Vih减小,NML=Vil-Vol增大,但是总的噪声容限是由小的一个决定,所以过大的Wp不利于CMOS反相器设计。

逐渐减小,曲线整体右移。当Voh,Vol不变时,Vih增大,Vil增大,NMh=Voh-Vih减小,NML=Vil-Vol增大,但是总的噪声容限是由小的一个决定,所以过大的Wp不利于CMOS反相器设计。

反之,随着栅宽Wp的减小, 逐渐增大,曲线整体左移。当Voh,Vol不变时,Vih减小,Vil减小,NMh=Voh-Vih增大,NML=Vil-Vol减小,但是总的噪声容限是由小的一个决定,所以过小的Wp不利于CMOS反相器设计。

逐渐增大,曲线整体左移。当Voh,Vol不变时,Vih减小,Vil减小,NMh=Voh-Vih增大,NML=Vil-Vol减小,但是总的噪声容限是由小的一个决定,所以过小的Wp不利于CMOS反相器设计。

可见,在CMOS反相器设计过程中,对电路做匹配是及其重要的!!!一般Wp:Wn大约为14:3,随着工艺变化,此比值略有波动。

b. 栅宽对静态功耗

图59 栅宽对CMOS反相器静态泄露功耗的影响

Id与W成正比,当Wp增加时,峰值电流增加,而两个管子均处于饱和区时,输出电压大致不变,所以静态泄露功耗会增加。随着栅宽Wp的增大, 逐渐减小,曲线整体右移,使得Vm右移,所以峰值功耗的点也右移!!!

逐渐减小,曲线整体右移,使得Vm右移,所以峰值功耗的点也右移!!!

3.【实验三】与非门电路设计

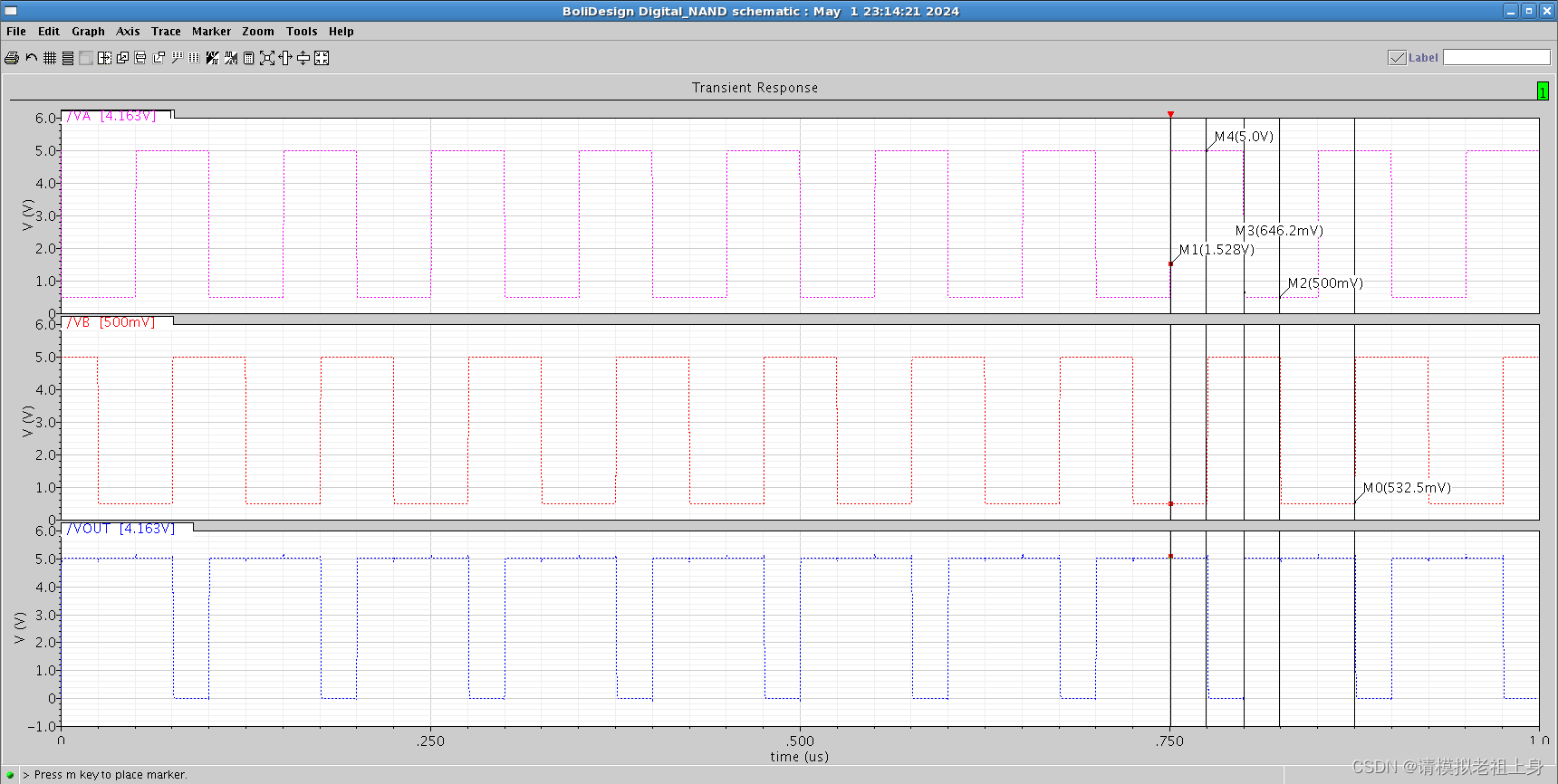

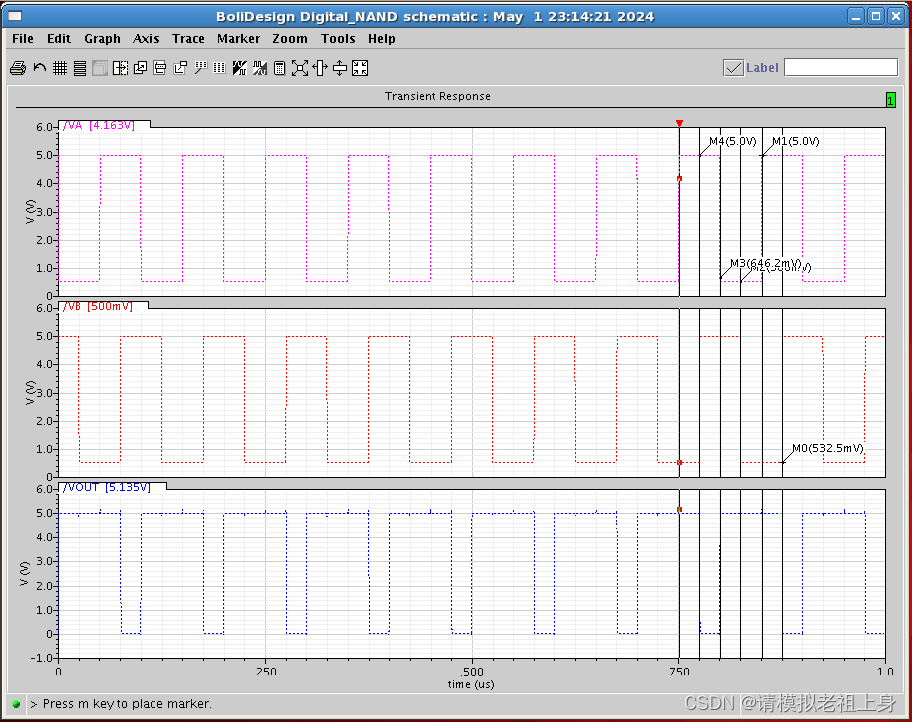

a. Trans 仿真

图60 CMOS与非门瞬态仿真结果

当输入为00时,输出为1;输入为01时,输出为1;输入为10时,输出为1;输入为11时,输出为0。可见完美实现与非逻辑,波形无失真。

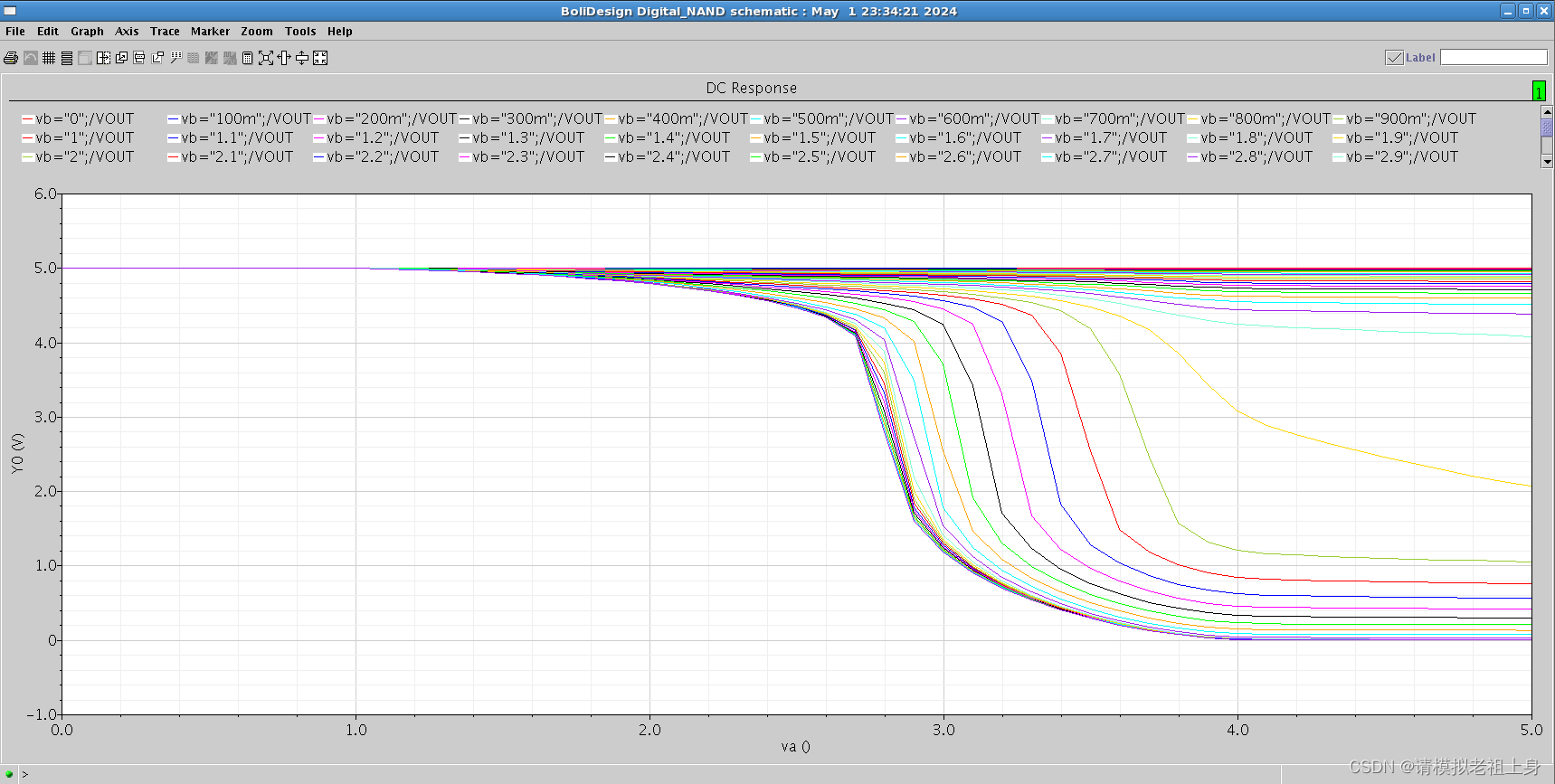

b. DC分析VTC

图61 CMOS与非门DC仿真VTC曲线结果

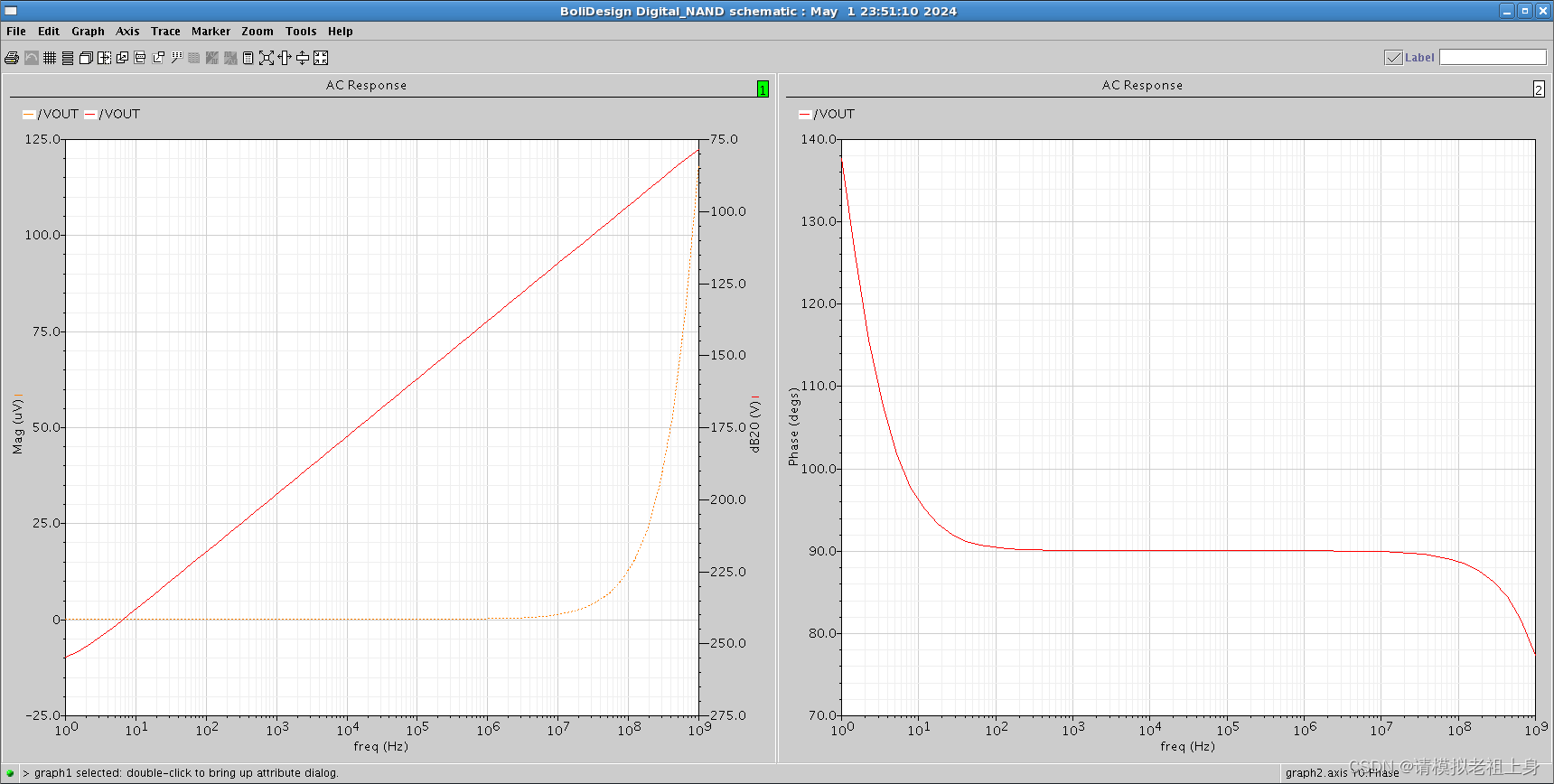

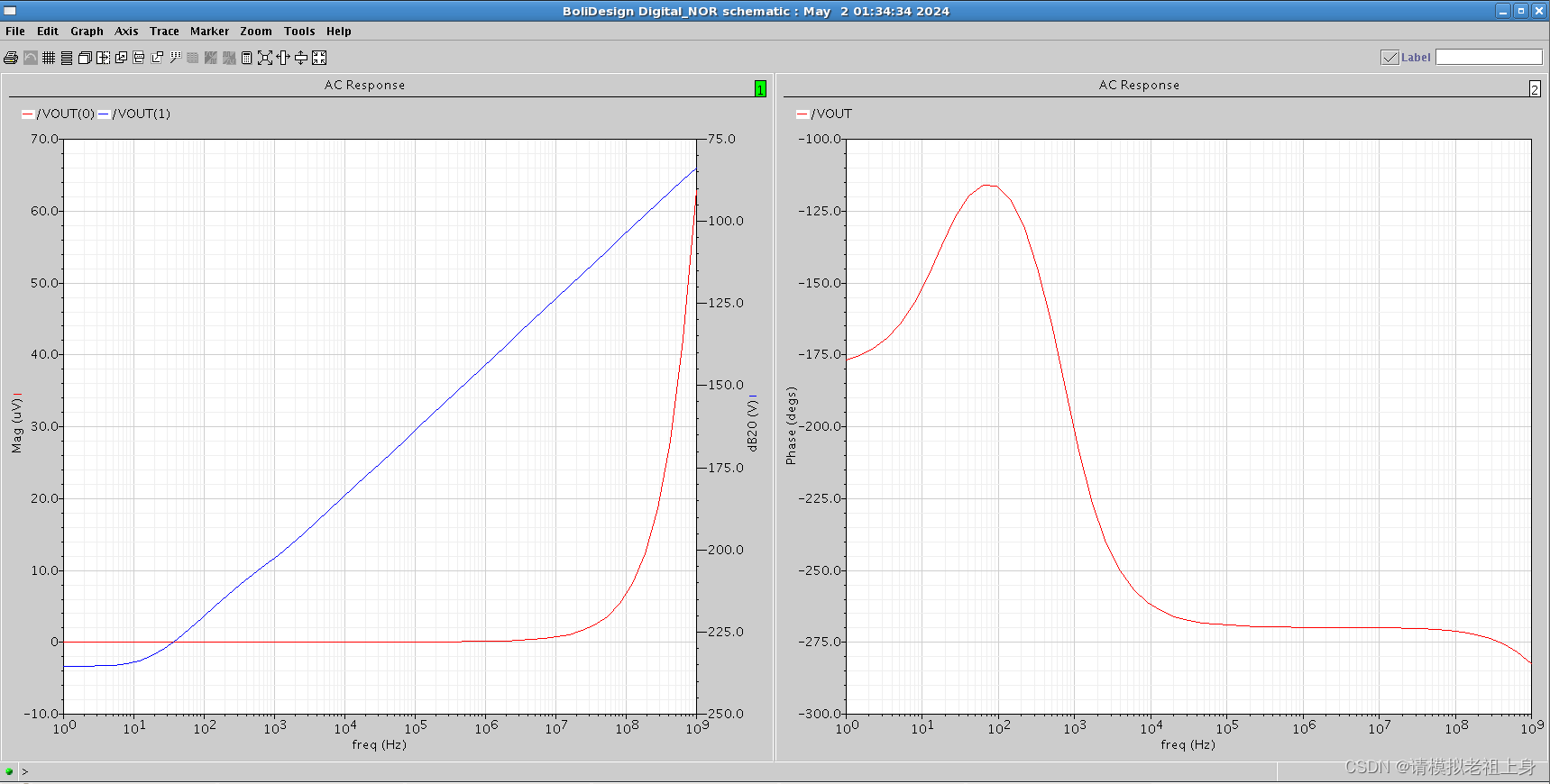

c. AC分析

Va:Vb |

幅频特性曲线与相频特性曲线 |

0:0 |

图62 CMOS与非门AC仿真的幅频特性曲线(Va=0;Vb=0) |

1:0 |

图63 CMOS与非门AC仿真的幅频特性曲线(Va=0;Vb=1) |

0:1 |

图64 CMOS与非门AC仿真的幅频特性曲线(Va=1;Vb=0) |

1:1 |

图65 CMOS与非门AC仿真的幅频特性曲线(Va=1;Vb=1) |

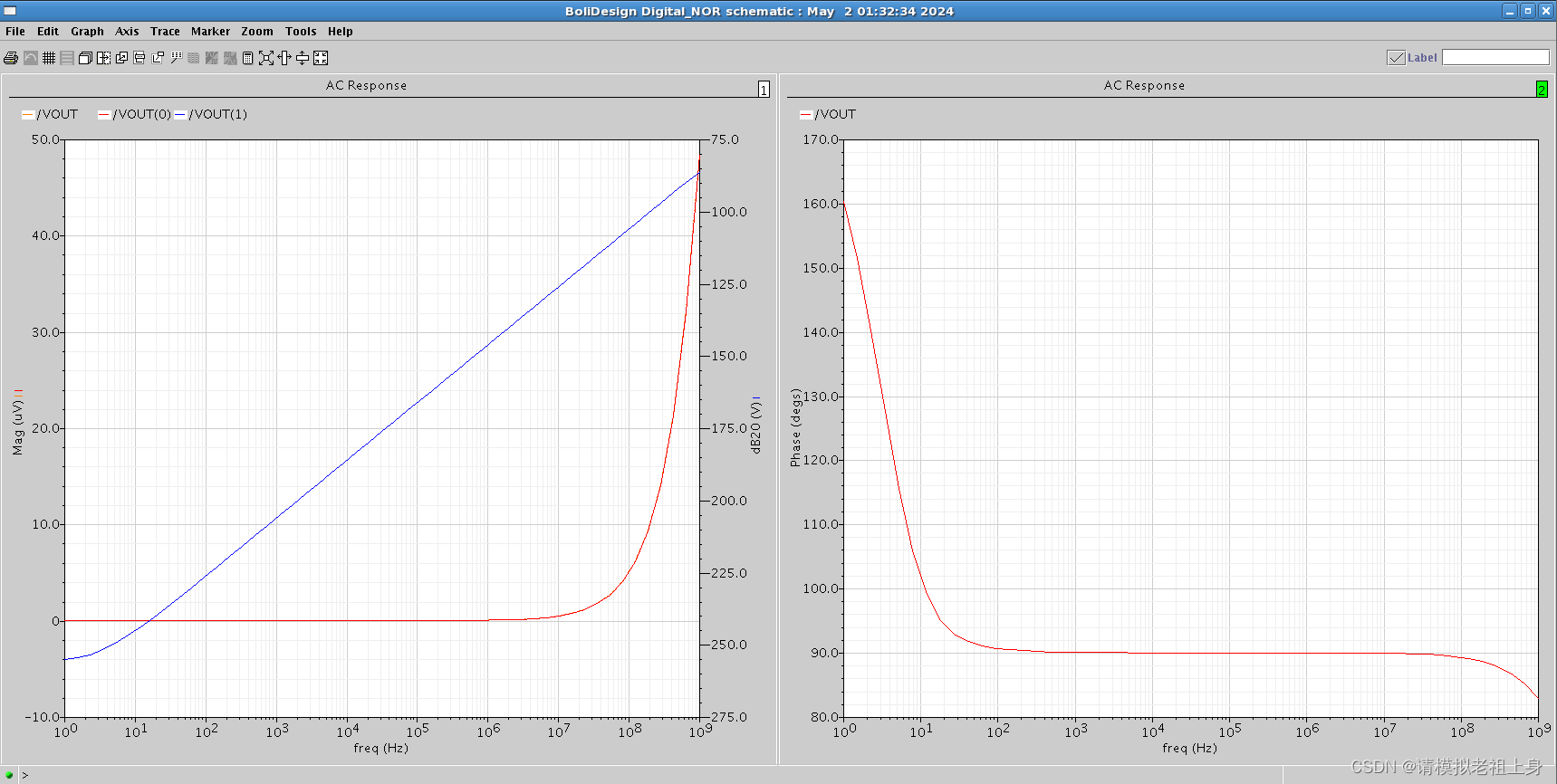

4.【实验四】或非门电路设计

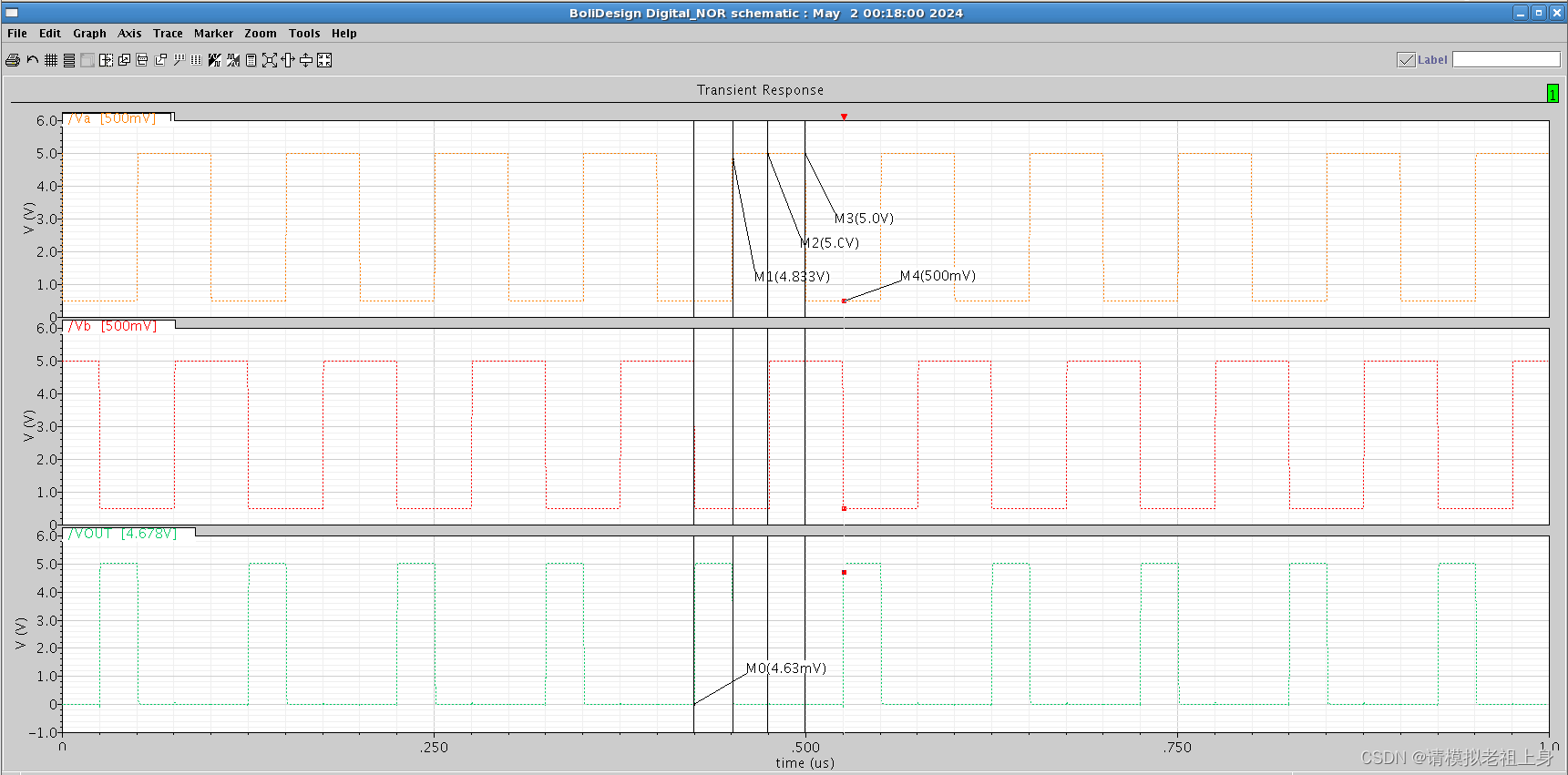

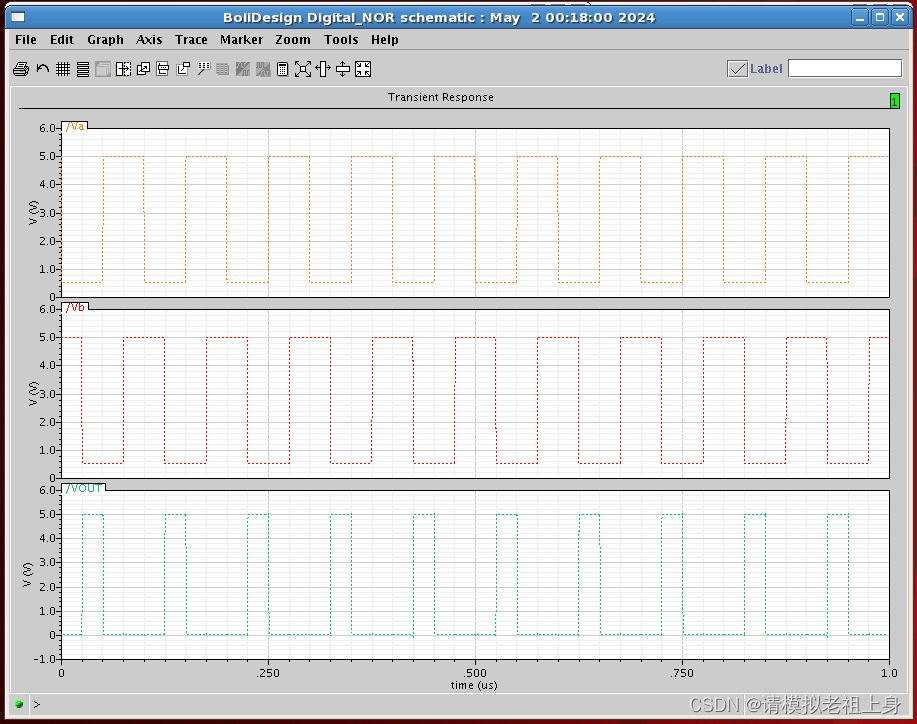

a. Trans 仿真

图66 CMOS或非门瞬态仿真结果

当输入为00时,输出为1;输入为01时,输出为0;输入为10时,输出为0;输入为11时,输出为0。可见完美实现与非逻辑,波形无失真。

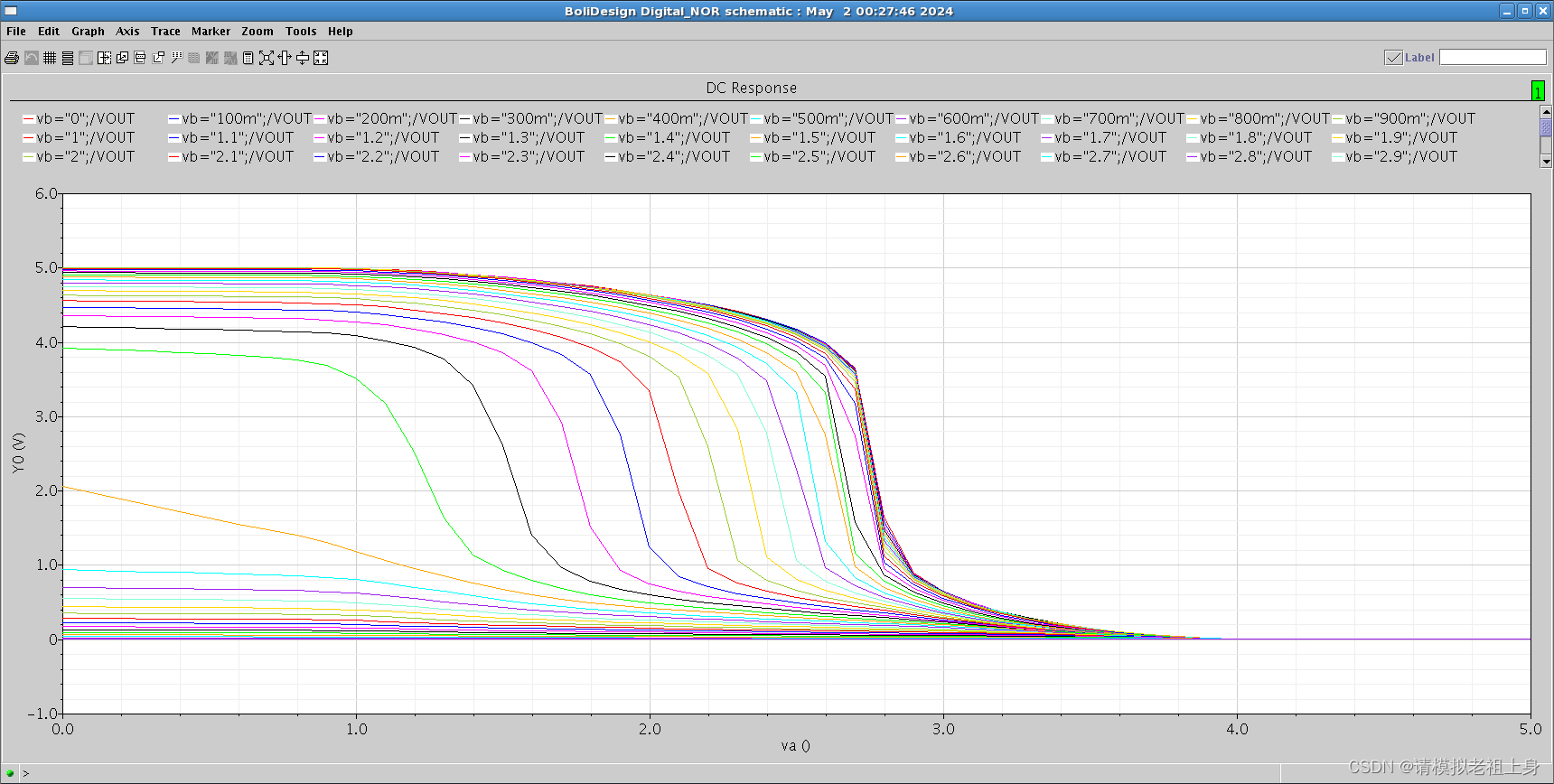

b. DC分析VTC

图67 CMOS或非门DC仿真VTC曲线

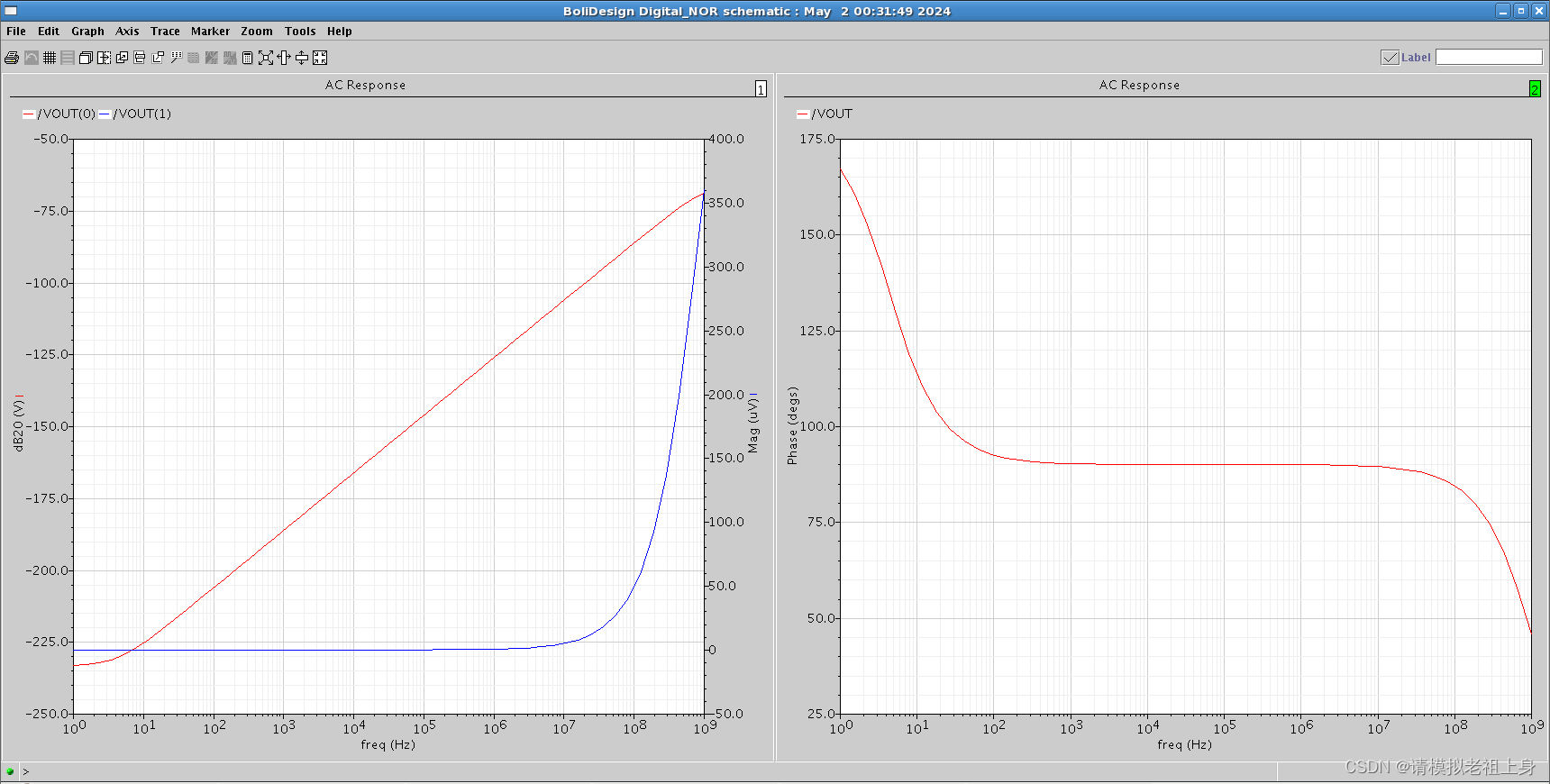

c. AC分析

Va:Vb |

幅频特性曲线与相频特性曲线 |

0:0 |

图68 CMOS与非门AC仿真的幅频特性曲线(Va=0;Vb=0) |

0:1 |

图69 CMOS与非门AC仿真的幅频特性曲线(Va=0;Vb=1) |

1:0 |

图70 CMOS与非门AC仿真的幅频特性曲线(Va=1;Vb=0) |

1:1 |

图71 CMOS与非门AC仿真的幅频特性曲线(Va=1;Vb=1) |

六、心得体会

本次实验是CAD的第四次实验,相较于前三次实验,我对IC5141的使用已经没有很大的问题了。本次实验课主要是用模拟的分析方法分析数字电路,我所遇到的主要问题是当存在多个影响因素时,如何设计实验验证得到正确的结论。还有一些学习方法论之类的总结,在这里书以成文:

- 原理串联,PPT总结

图72 PPT对或非门电路各个参数的总结

- 对于数字电路多输入端口的情况,由于输入只有高和低,导致介于中间的输入状态往往不做考虑,所以设计实验是最好还是单独控制输入,做表格分析。相较前一种,对每个工作段进行参数扫描的方式,往往导致丢失主要研究对像,跑出很多中间段,不利于分析与总结。

- 深刻感受到模拟仿真和数字验证的差距,Verilog验证的效率要高得多,通过这种模拟的方式主要还是加深对电路理解。

非常感谢王老师的讲授,希望自己可以在模拟的世界走的更远。

![[SWPUCTF 2021 新生赛]PseudoProtocols、[SWPUCTF 2022 新生赛]ez_ez_php](https://img-blog.csdnimg.cn/direct/ef96cc66bfd644c1b48f13bed2700c18.png)