什么是PDK?

PDK( Process Design Kit ),工程设计数据包,是芯片厂家foundary提供给IC设计公司的有关制造工艺的模型和EDA工具支持。是连接IC制造公司,IC设计公司的桥梁。

PDK包含内容:

- 器件模型

- SPICE模型

- 模型 与 测量误差数据

- 设计规则

- 版图层次定义

- 几何图形规则

- ESD / Latch-up 防护规则

- 天线效应规则

- 电流密度 规则

- 应力保护规则

- 版图工艺库(文本/DFII)

- 版图层次定义

- 层次显示定义文件(display.drf)

- GDSII格式转换映射文件(MAP)

- 抽象结构单元版图(Symbolic Cell)

- 固定结构器件版图

- Pcell

- 版图检查工具支持

- 设计规则检查:几何图形规则检查、天线效应规则检查、ESD / Latch-up 规则检查、电流密度检查

- 网表检查:ERC、LVS

- 寄生参数提取:LPE

- 标准单元库

- 单元行为库(.v)

- 时序参数库(tlf)

- 线负载模型(wire load model)

- Memory Compiler

- IP库

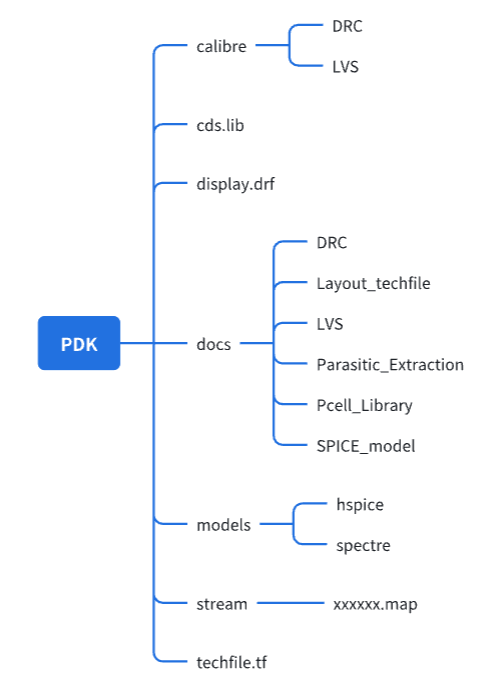

virtuoso安装包含的目录文件结构:

文件 |

类型 |

描述 |

calibre |

目录 |

包含calibre所需的DRC LVS ANT的command file |

cds.lib |

文件 |

定义了基本库和该制程的元件库的所在位置.用来调用,保存库的文件。 |

diaplay.drf |

文件 |

定义了techfile中各层的显示样式 |

docs |

目录 |

该PDK的使用文档 |

models |

目录 |

包含了该制程元件的用于仿真的模型文件 |

xxx 40nn |

目录 |

各个厂商的工艺库 |

stream |

目录 |

map文件 |

techfile.tf |

文件 |

设计规则文件 |

.cdsinit |

文件 | 主要负责一些加载项的设置,帮助读取的脚本。load "xxxxxxx.il" |

| layMap文件 | 文件 | 导出,导入GDS映射文件,定义了每层layer对应的GDSII码 |

| .cdsenv | 文件 | 主要负责一些环境变量或参数设置 |

各个文件的内容层次结构:

PDK(L R C)--> cell --> block --> chip

- PDK(描述 电感L、电容C、电阻R、MOS管)

- 电阻电感电容等组成一个个cell

- 一个个cell组成block

- 一个个block组成 top

- 一个个top组成 chip

1.工艺库

工艺库,也叫基础库,是工艺厂提供的电路,版图设计基础信息集合,

包含电路设计需要的SPICE器件模型

仿真数据模型model,

器件模数格式CDF

版图设计需要的PCELL基础单元器件版图

实际上所有的器件模型信息都在工艺库里

CDF(Component Description Format,组件模数格式) &callback:

器件的属性描述文件,定义了器件的类型、名称、参数,以及参数调用关系函数集callback、器件模型、器件的各种视图格式等等

Pcell(Parameterized cell,参数化单元):

描述晶体管(或其他器件)的可能定制方法供设计师在EDA工具中使用

2. IP库(==top)

工艺厂已经成型的,具有特定功能的电路叫IP

IC设计公司如果需要IP,需要花钱购买

3. 数字标准单元库

工艺厂提供的已经设计好的数字标准单元电路和版图,可以提高IC设计公司效率。

数字版图的自动布局布线对于模拟版图来说,有些地方需要我们自己画数字单元,来满足模拟电路的可靠性设计

4. 设计规则文件

规则文件:我们在版图上必须遵守的规则,按照符合工艺厂最低标准要求总结出的文件

设计规则文件:

版图层次的定义

几何图形规则等物理上定义

同时包含,天线效应

电流密度规则

ESD

Latch up等电学特性可靠性设计要求

主要包括:

Design rule:设计规则文件,主要用于查找,grid,层次定义和层次画法和间距

Electrical Specifications:电学特性文件,给出的是讲具体的工艺参数及其结果抽象出的点穴参数,是电路与系统设计、模拟的依据。Layout主要用来查找电阻值、过电流能力等

5. 设计规则检测文件

DRC rule:

检查版图的物理特性是否符合design rule要求。DRC rule是根据design rule编写的

LVS rule:

电路图与版图一致性检查(LVS),

方法是从版图中提取数据转换为网表,和电路转化的网表进行数据对比。

将不一样的地方通过工具显示出来,方便layout改动

Ant rule:

用于检查天线效应是否满足设计要求,是可靠性设计中的一

LEP:

用于提取后仿真版图数据。对已设计的版图提取各种器件、它们的连接关系以及各种寄生电容和电阻,将提取出的器件以及连接关系和寄生参数等作为电路模拟的输入数据,再次进行电路模拟仿真,以估计计生参量对电路性能的影响