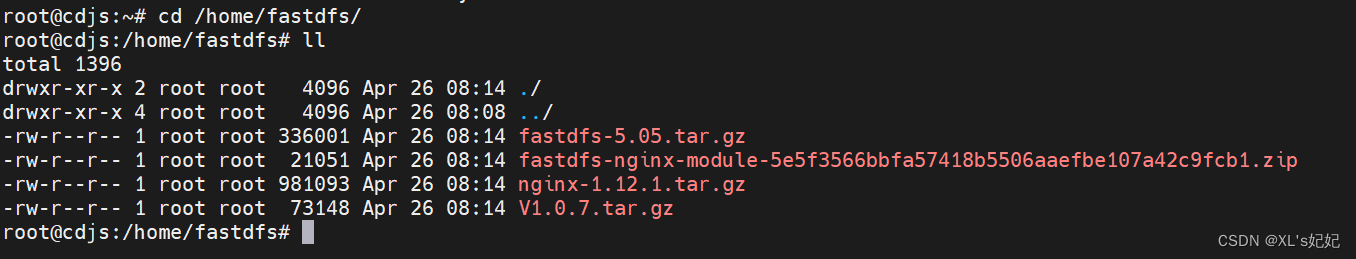

1.反相器

module inv(A,Y);//A,Y是我的端口

input A;//定义属性

output Y;

assign Y = ~A;//定义输入输出关系

endmodule//testbench of inv

`timescale 1ns/10ps//1ns是时间单位,10ps为精度

module inv_tb;

reg a;

wire y;

inv inv(.A(a),.Y(y));

initial begin

a <= 0;//reg型变量用"<="

#10 a <= 1;

#10 a<=0;

#10 a<=1;

#10 $stop;

end

endmodule

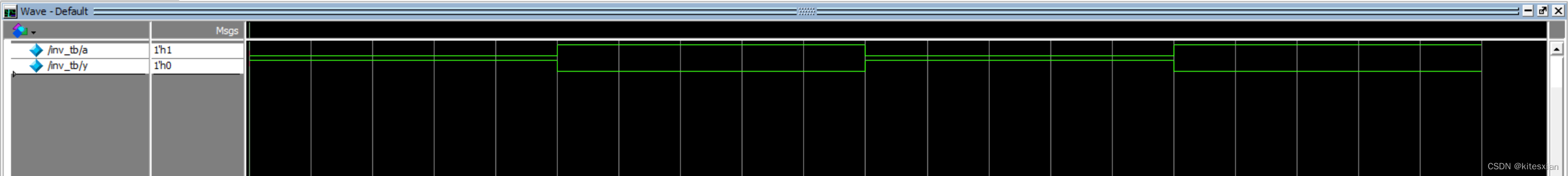

2.八位反相器

module inv(A,Y);

input[7:0] A;

output[7:0] Y;

assign Y=~A;

endmodule//testbench of inv

`timescale 1ns/10ps//1ns是时间单位,10ps为精度

module inv_tb;

reg[7:0] a;

wire[7:0] y;

inv inv(.A(a),.Y(y));

initial begin

a <= 0;

#10 a <= 8'b01011011;

#10 a<= 8'b01010100;

#10 a<= 8'b10111111;

#10 $stop;

end

endmodule

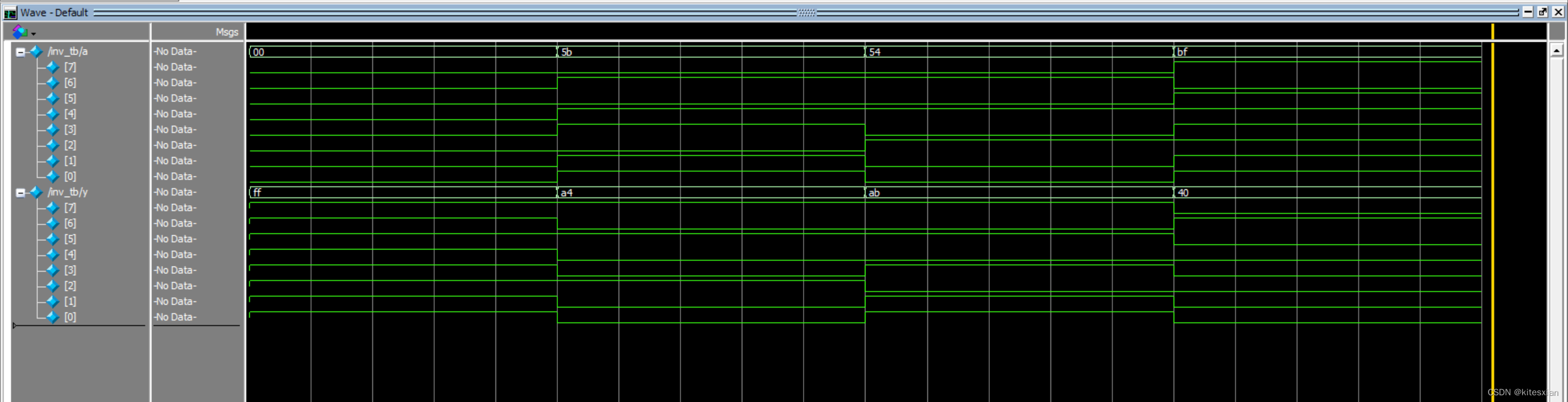

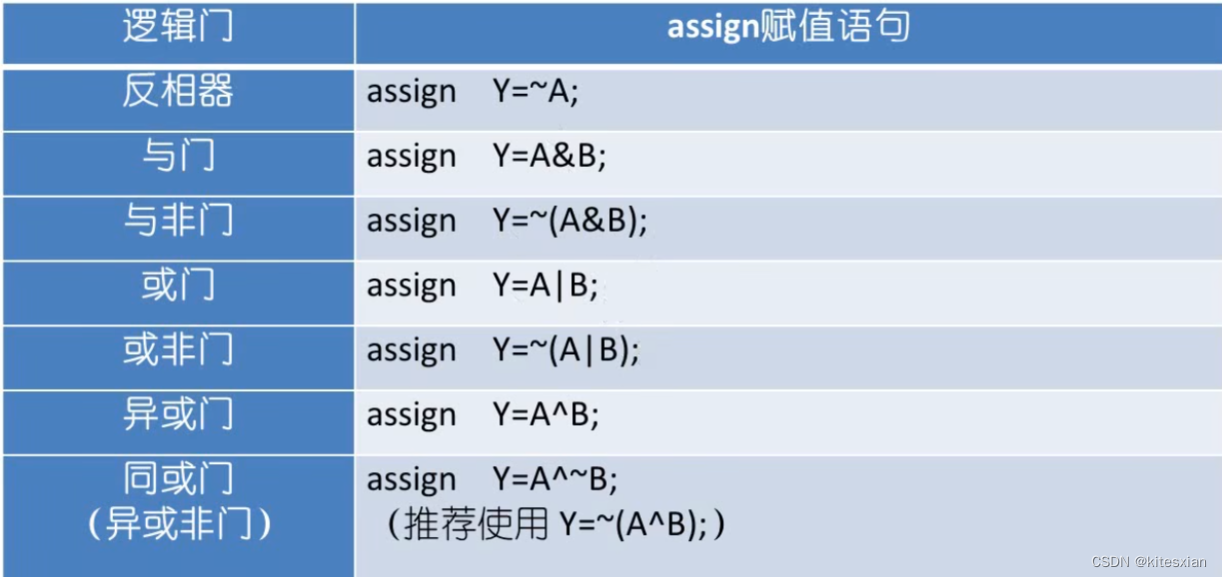

3.与非门

module nand_gate(A,B,Y);

input A,B;

output Y;

assign Y=~(A&B);

endmodule//testbench

`timescale 1ns/10ps//1ns是时间单位,10ps为精度

module nand_gate_tb;

reg a,b;

wire y;

nand_gate nand_gate(.A(a),.B(b),.Y(y));

initial begin

a <= 0;

b <= 0;

#10

a <= 1;

b <= 0;

#10

a <= 0;

b <= 1;

#10

a <= 1;

b <= 1;

#10 $stop;

end

endmodule

其实,4位的与非门你也应该会写了

其实,4位的与非门你也应该会写了

同样的,其他的逻辑门你也可以实现;

参考视频:精准空降

![[C++初阶]类和对象(三)](https://img-blog.csdnimg.cn/direct/e28ac8b254e7404cb10f81e9c00cbc15.png)