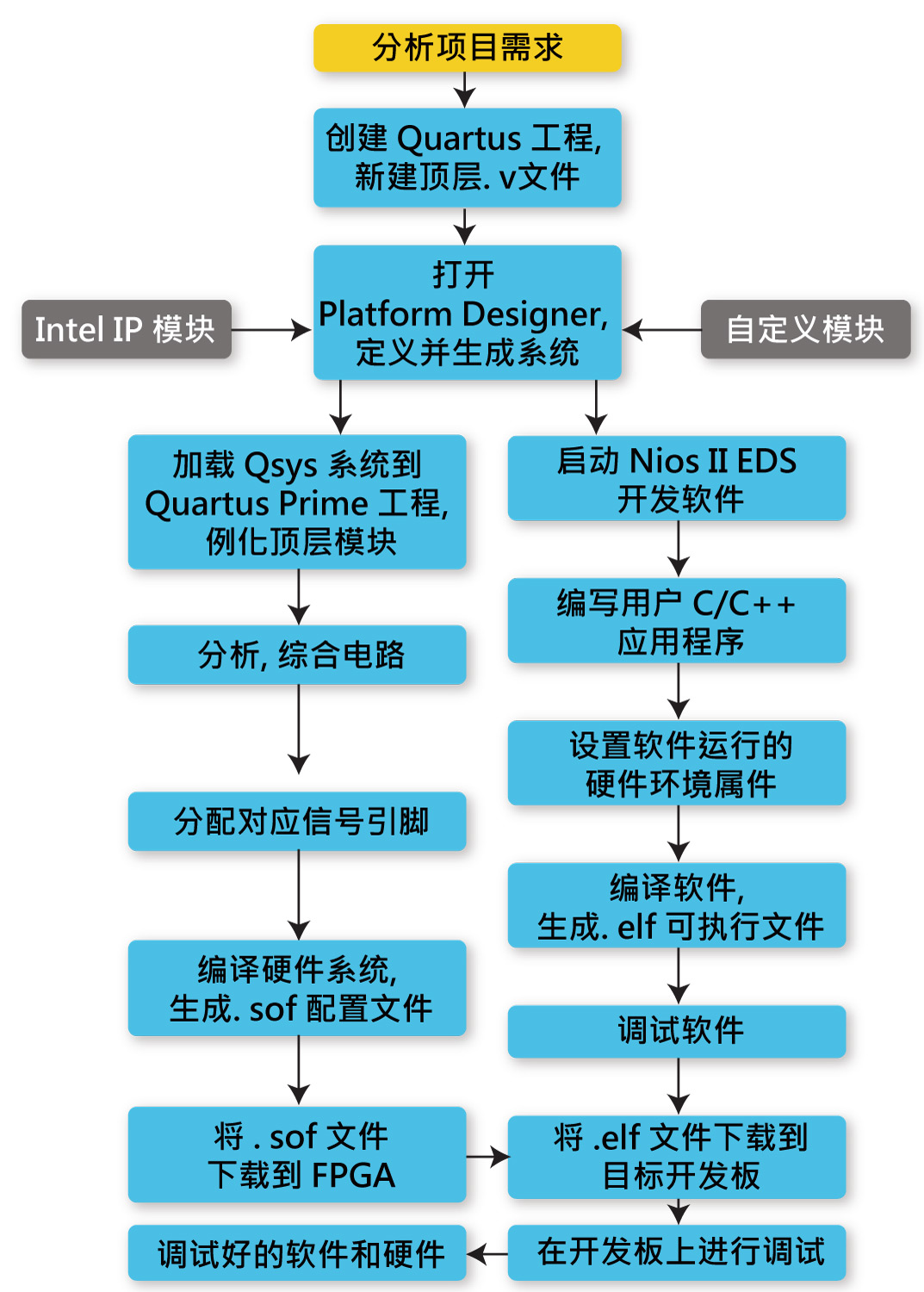

Q:上一期介绍完基本设计流程和实验原理,接着我们完成系统硬件设计部分,包括Platform Designer系统及Quartus工程。

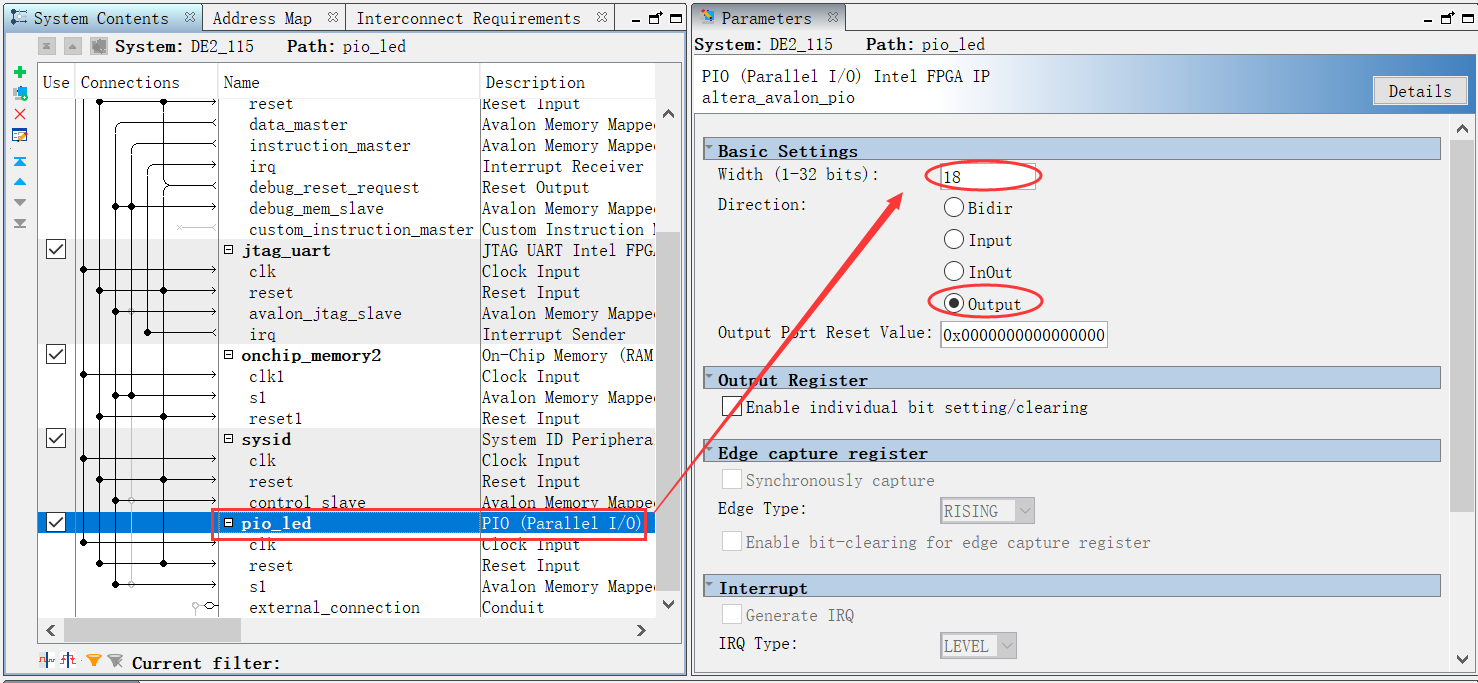

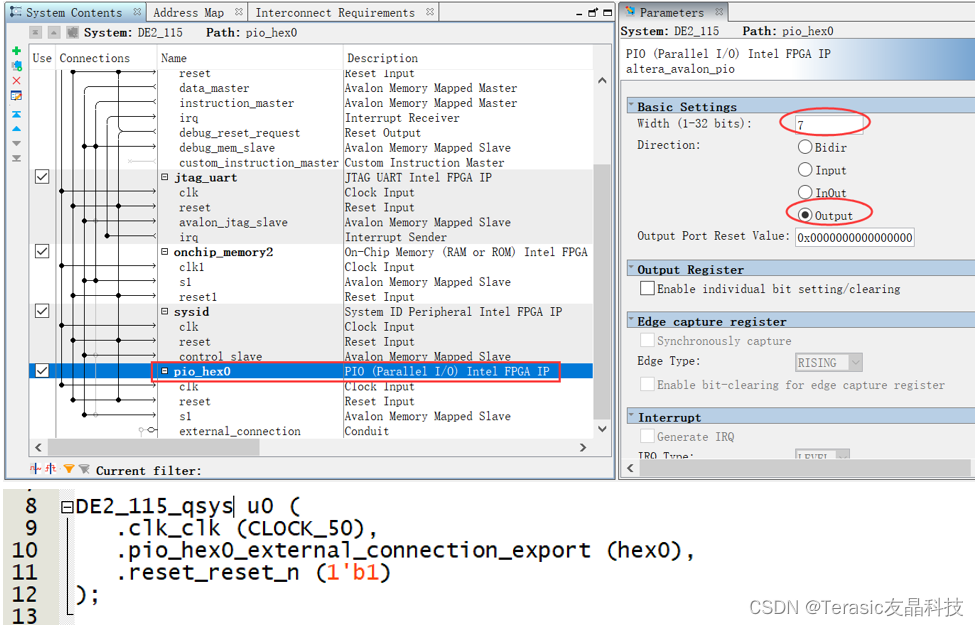

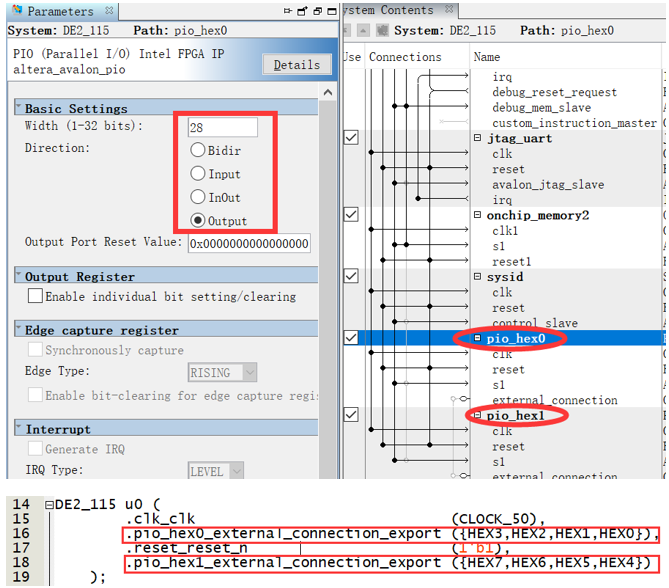

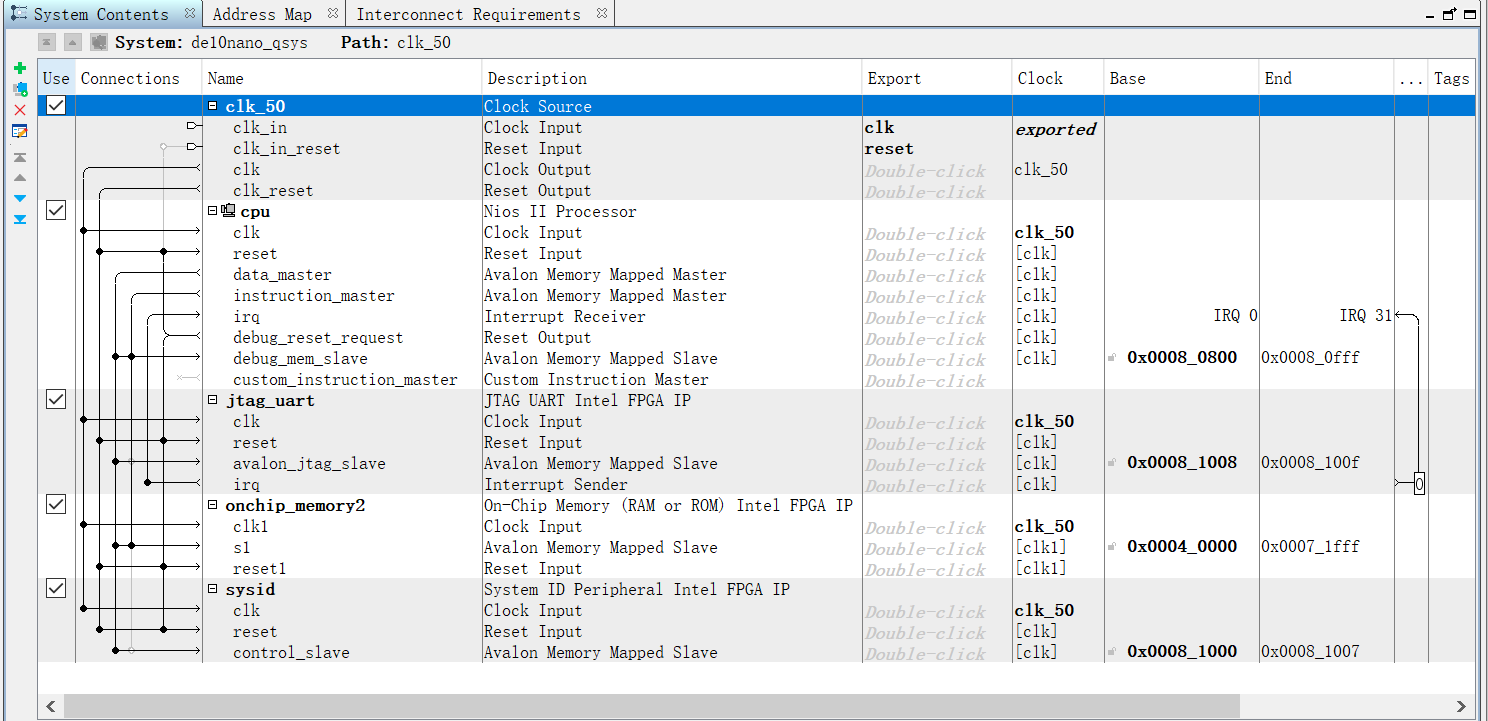

A:依次搜索并添加Nios II Processor、JTAG UART、On-Chip Memory和System ID IP组件,连接各组件并Assign Base Address后的Platform Designer系统如下图所示,本次实验各IP组件相关参数设置为:

Clock Source:保持系统默认的时钟频率不变为50MHz,也是DE2-115开发板的板载外部时钟;

Nios II Processor:将Vectors选项下的Reset vector memory和Exception vector memory均设定为onchip_memory2.s1;

JTAG UART:保持系统默认设置不变;

On-Chip Memory:将Total memory size修改为204800 bytes,Data Width为32不变;

System ID:将Parameters设置为0x00de2115。

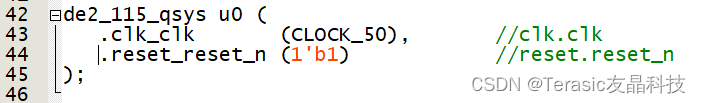

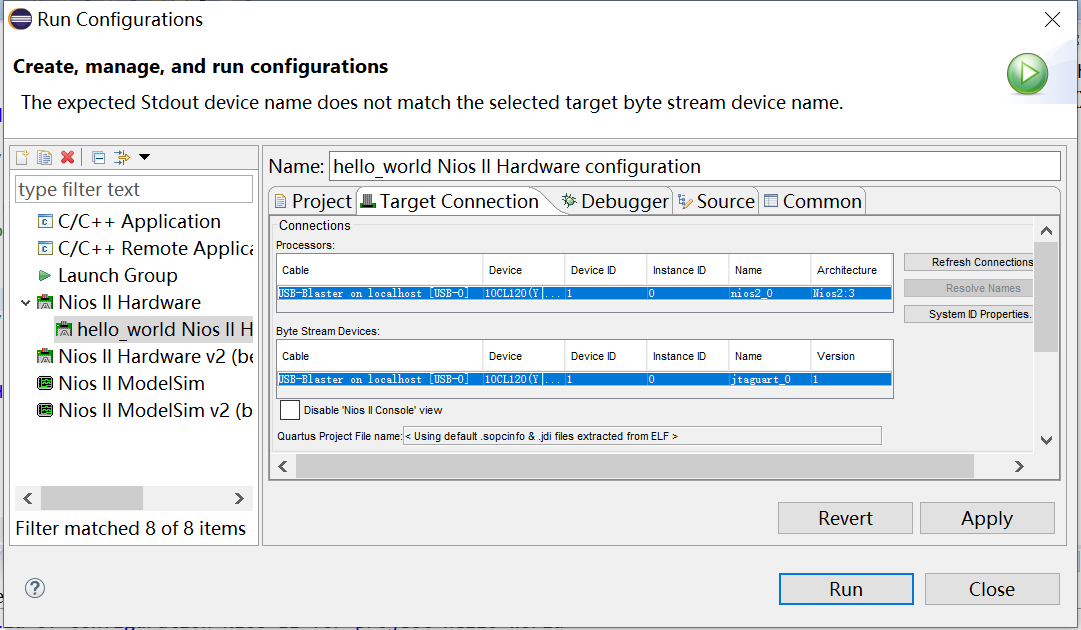

点击Generate HDL生成系统后,将.qsys文件添加到Quartus工程中并在顶层.v文件中例化系统。最后编译Quartus工程生成.sof配置文件,完成Nios II Hello_World 工程的硬件设计部分。