本文仍然介绍Clocking Wizard的配置项,这些配置项不再包括输入时钟和输出时钟的具体信息,主要介绍其他时钟管理特性,如参数覆盖、扩频(Spread Spectrum)和抖动优化(Jitter Optimization)等。

1 原始参数覆盖

器件和组件的某些特定参数覆盖会在MMCM Settings中显示出来。

1.1 覆盖计算参数

Clocking Wizard会为时钟组件的参数选择最优设置。可以根据自己的需求覆盖掉上述任何计算出的参数。如果选择了Allow Override Mode,原始参数会被覆盖掉,将使用新计算出的值作为参数。

在时钟设计过程中,原始参数覆盖是一个强大的功能,它允许用户根据具体的应用需求、硬件限制或优化目标来手动调整参数。虽然Clocking Wizard通常会提供合理的默认设置,但在某些情况下,可能需要手动调整以达到最佳性能或满足特定的时序要求。

当允许覆盖模式时,用户需要谨慎操作,确保所覆盖的参数值是合理的,并且不会导致时序违规或其他设计问题。此外,更改原始参数可能会影响功耗、性能和稳定性,因此需要进行全面的测试以确保设计的正确性。

上图中列出的参数与原始的物理时钟相关,而不是源代码中创建的逻辑时钟。例如,要修改为最高优先级CLK_OUT1计算出的设置,实际上需要修改MMCM或PLL的CLKOUT0参数,而不是CLKOUT1参数。

1.2 MMCM 计数器级联

CLKOUT6 分频器(计数器)可以与 CLKOUT4 分频器级联。这提供了大于 128 的输出分频能力。CLKOUT6 计数器将信号输送到 CLKOUT4 分频器的输入端。级联分频器的输出与其他所有输出分频器之间存在静态相位偏移。

只有在选择了Allow Override Mode的情况下,才能使用计数器级联功能,即CLKOUT4_CASCADE选项才能被选择。

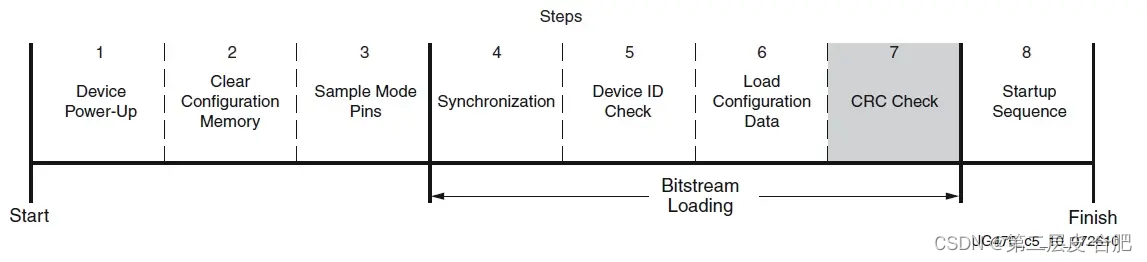

只有在选择了Allow Override Mode的情况下,才能选择 STARTUP_WAIT 选项,该选项与 Configuration CLK_Cycle 选项配合使用,以等待时钟管理器锁定后再完成启动序列。

CLKFBOUT_USE_FINE_PS 是 CLKFBOUT 计数器的一个变种,它启用了 CLKFBOUT 的精细相位偏移。选择动态相位偏移选项来使用 CLKFBOUT 的精细相位偏移。

2 端口重命名(Port Renaming)

端口重命名的信息会被整合到生成的源代码和XDC文件中,以帮助用户或开发者更好地理解和使用这些时钟。

3 Summary(摘要)

摘要选项页提供了Clocking Wizard输出时钟与组件输出时钟之间连接的信息。下图中下面的表中的“Source”列指定了组件的输出引脚。它说明时钟是直接由组件生成的还是使用BUFGCE_DIV派生出来的。

3.1 输入时钟摘要

在集成开发环境(IDE)的第一个选项卡中输入的信息会显示为输入时钟的摘要。包括输入时钟频率、时钟源和抖动。

3.2 输出时钟摘要

显示输出时钟的派生时序信息。如果所选的组件具有振荡器,则会提供压控振荡器(VCO)的频率作为参考。如果启用了secondary输入时钟,则可以选择这个时钟用于计算派生值。当启用扩频(Spread Spectrum)时,会提供实际的调制频率作为参考。Tspread 是实际的扩频值,如“配置输出时钟”中所计算的那样。

4 Clock Monitor(时钟监控)

如果在Clocking Options选项中选择了Enable Clock Monitoring,在Clocking Wizard中就会出现Clock Monitor选项页。

时钟监控功能是Clocking Wizard IP核的一部分,用于监控给定系统中的时钟,以检测时钟丢失或超出范围错误。在Zynq或Zynq UltraScale设备中,被监控的时钟可以是处理系统(PS)时钟或可编程逻辑(PL)时钟。在FPGA中,被监控的时钟可以是任意时钟,被监控的信息包括:

• Clock Stop(时钟停止):时钟信号呈平坦线,无变化。

• Clock Glitch(时钟抖动):时钟的占空比发生变化。

• Overrun(超频):时钟的跳变次数高于预期。

• Underrun(欠频):时钟的跳变次数低于预期。

注意:超频和欠频统称为超出范围错误。

该IP提供了可扩展逻辑,用于监控四个时钟。

• Reference Clock Frequency(参考时钟频率):参考时钟频率决定了要监控的时钟的频率。

• Channel Clock Frequency(通道时钟频率):根据参考时钟的值选择要监控的时钟的频率。

• Tolerance(容差):根据编程设置监控时钟所需的精度。

注意:仅接受容差的整数值。

• Enable_PLL/MMCM (0-1):启用此选项将监控输入到MMCM/PLL的时钟。

注意:如果在IDE中启用了Enable_PLL/MMCM选项,请确保主/辅时钟频率不超过300 MHz。用户无法请求超过300 MHz的用户时钟频率(USER_CLK_FREQ_0/1/2/3)。

5 输出时钟的抖动(Jitter)和相位误差(Phase Error)

在Clocking Wizard中,可以查询任何输出时钟抖动和相位误差。这些参数对于评估时钟源的稳定性和性能至关重要。

例如,有一个名为clk_wiz_0的组件,如果想要获取clk_out1的抖动和相位误差,可以在Tcl Console中输入以下命令:

get_property CONFIG.CLKOUT1_JITTER [get_ips clk_wiz_0]

get_property CONFIG.CLKOUT1_PHASE_ERROR [get_ips clk_wiz_0]

注意:get_ips clk_wiz_0:用于获取名为clk_wiz_0的IP实例。

![[Flutter3] 记录Dio的简单封装(一)](https://img-blog.csdnimg.cn/direct/4f8bb96b4dc94cd589e40293226cfbce.png)