一、有限状态机基本结构

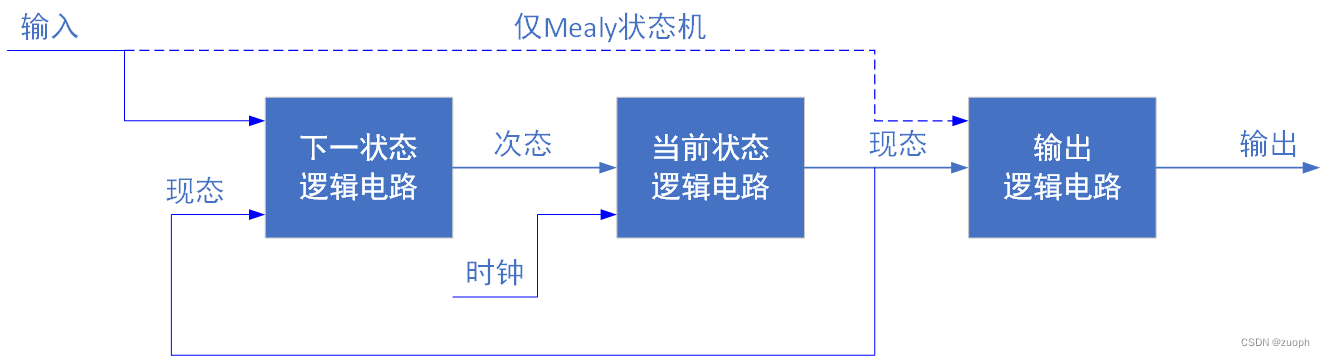

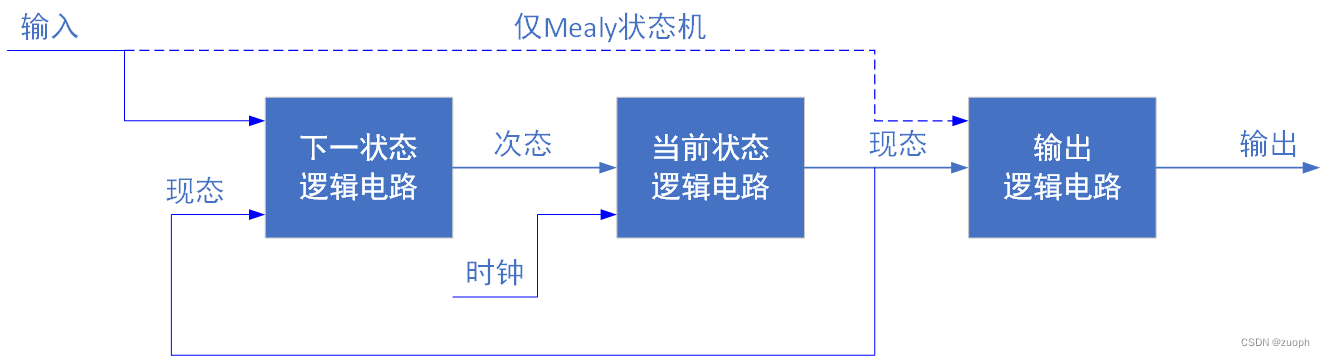

本文主要介绍使用verilog编写有限状态机FSM(finite state machine),它主要由三部分组成,下一状态逻辑电路,当前状态时序逻辑电路和输出逻辑电路。

有限状态机框图如下图所示:

根据电路输出是否与输入有关,有限状态机分为两种,一种是Mealy状态机,它的输出不仅与当前状态相关,还与电路输入相关;另一种是Moore状态机,它的输出只与当前状态相关。

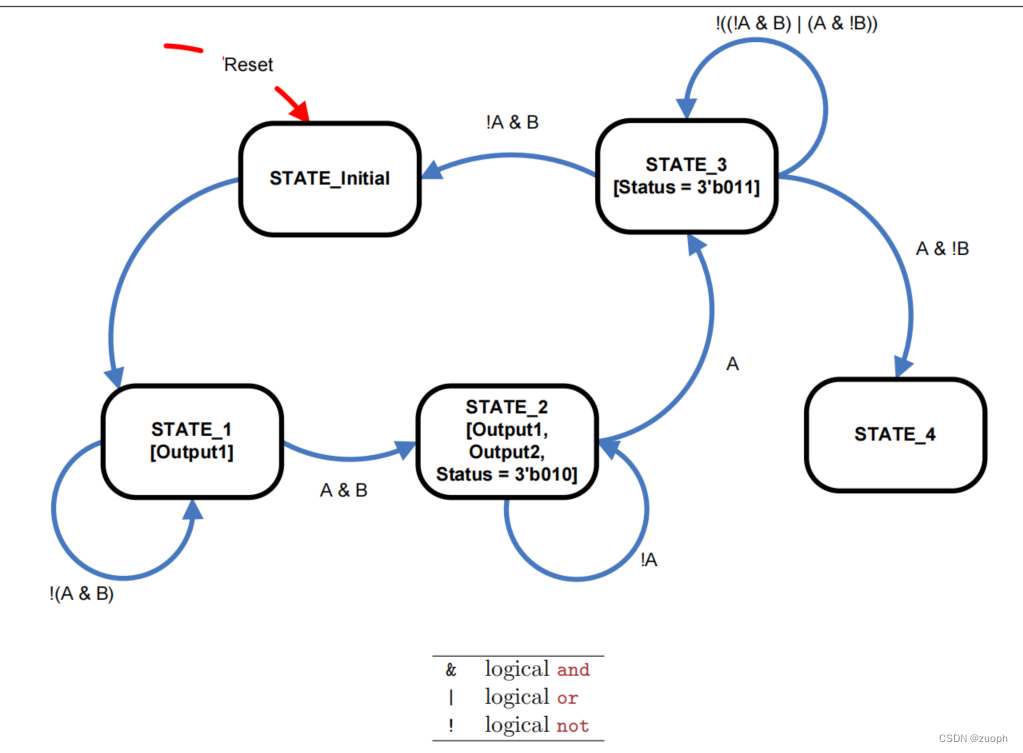

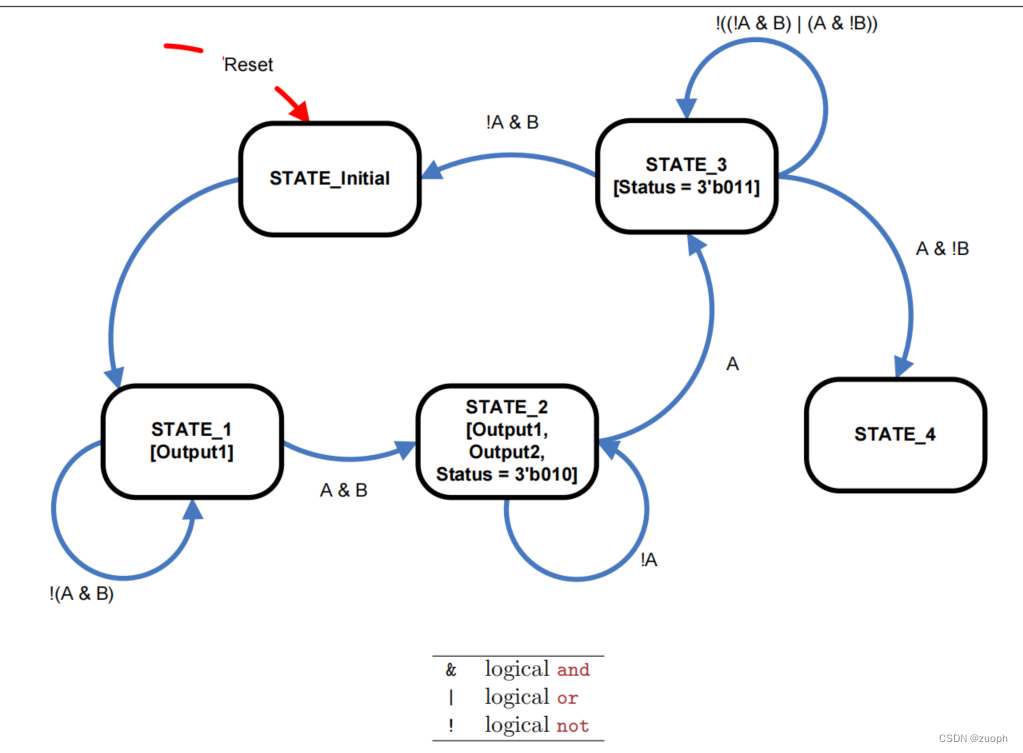

二、verilog写一个基础有限状态机(moore型状态机)

状态转移图如下所示。一共有5个状态,我们需要用verilog实现上述状态机。

第一步要做的是创建一个状态编码用于记录