【一】二极管

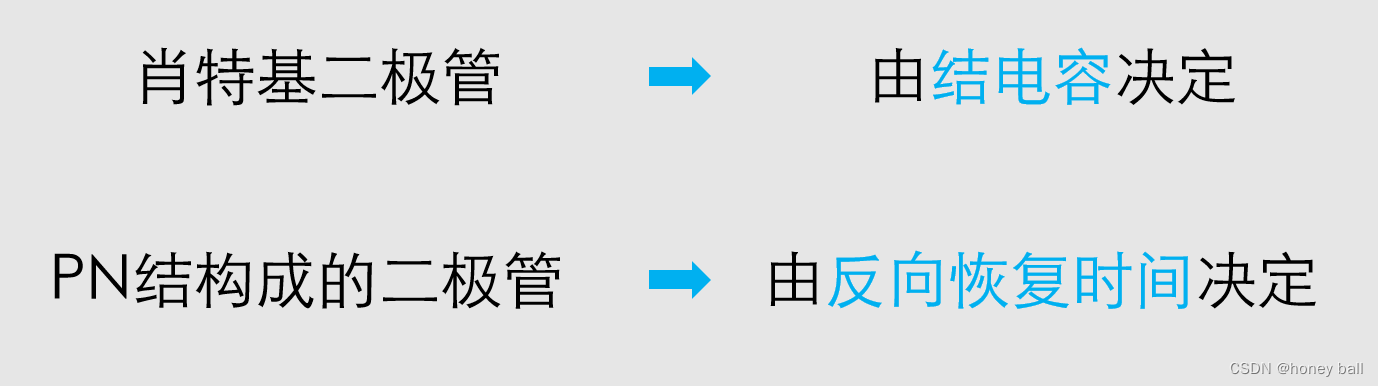

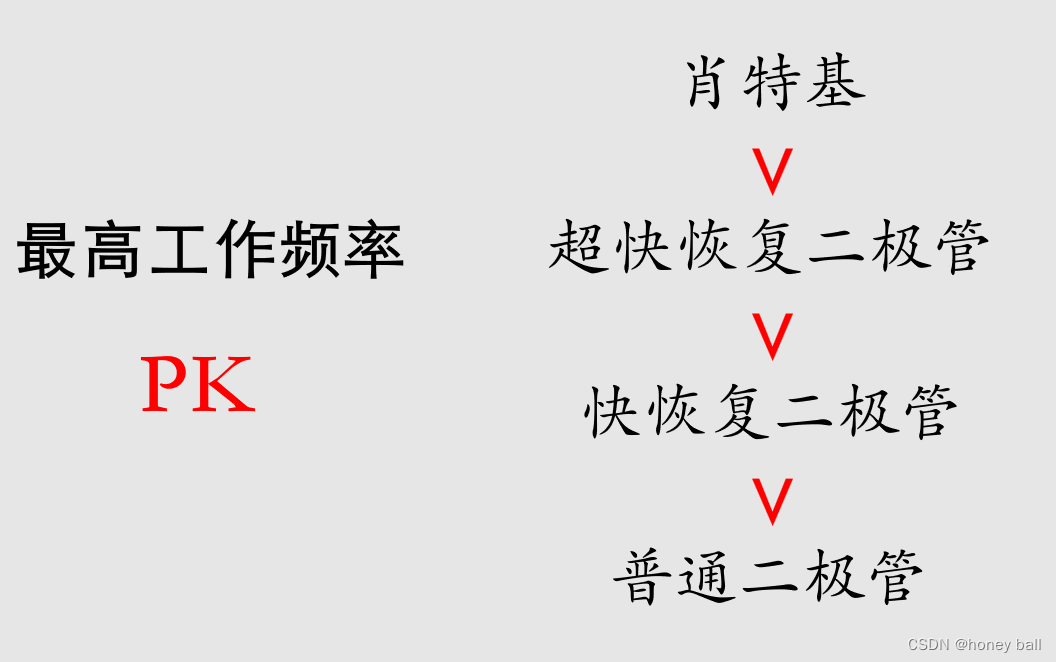

最高工作频率:

定义:二极管的最高工作频率,即二极管在电路中能够正常工作的最高频率。常见的硅二极管的最高工作频率通常在几十MHz到几百MHz之间。在高频下,二极管可能无法有效地阻止反向电流,但也不会完全变成导线。

最高工作频率的决定因素:

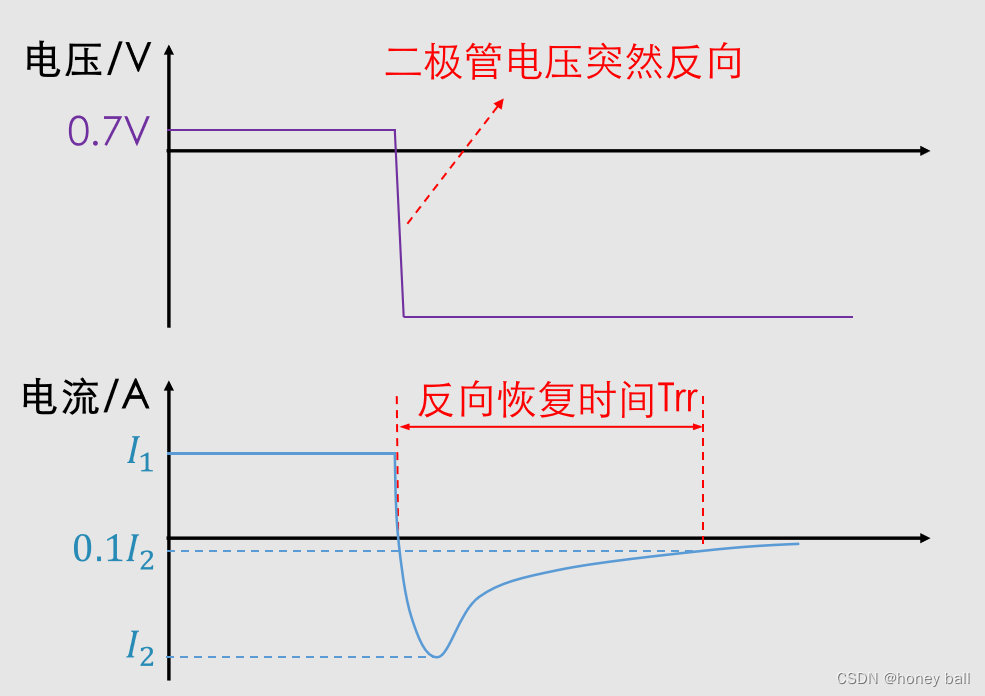

反向恢复时间:

二极管的(反向恢复时间)是衡量其从导通状态切换到截止状态时性能的一个重要参数。它指的是二极管从正向导通状态切换到反向截止状态时,反向电流下降到其最大值的一定比例(通常10%)所需的时间。这个时间反映了二极管内部存储电荷的清除速度,是衡量二极管开关性能的关键指标。

///

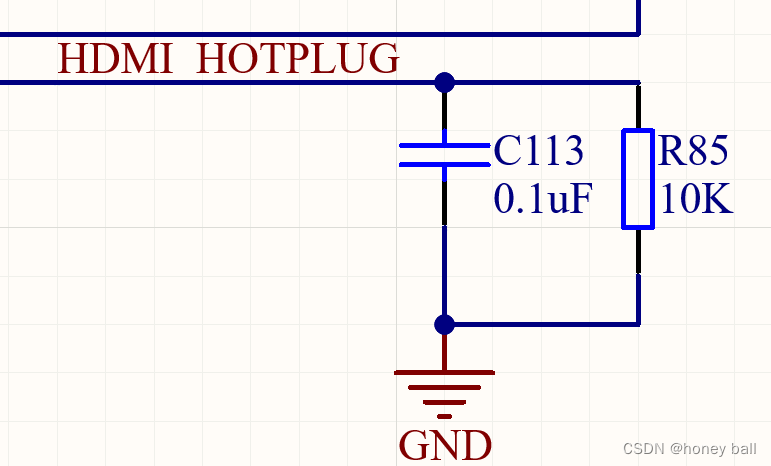

RC并联的滤波是低通滤波。这种滤波方式利用了电容和电阻的特性来滤除信号中的杂波和噪声。在RC并联电路中,电容和电阻并联连接,形成一个低通滤波器。当输入信号中存在高频噪声时,电容器可以通过存储电荷的方式来滤去这些高频成分,从而达到滤波的效果。与此同时,电阻器的作用是限制电容器的充电电流,使其充电和放电的速度得以控制,从而保证电路的稳定性和可靠性。因此,RC并联电路能够保留低频信号,而滤除高频噪声。

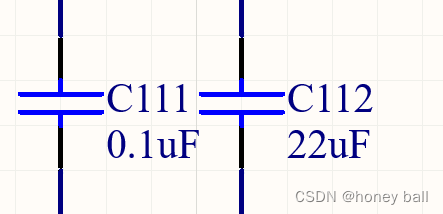

0.1uf电容通常与较大点的电容一起使用进行滤波。波器的设计是为了滤除电源或其他信号中的高频干扰信号,保持输出的稳定性和纯净性。

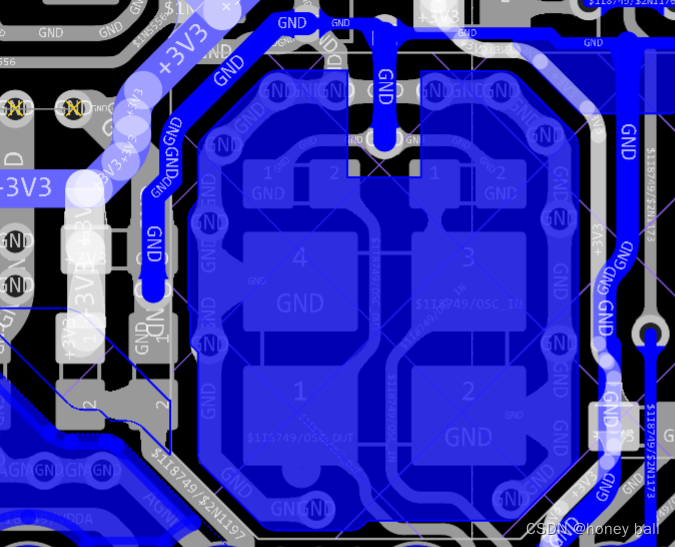

对晶振做包地处理:(环绕打孔连线,背面铺铜)

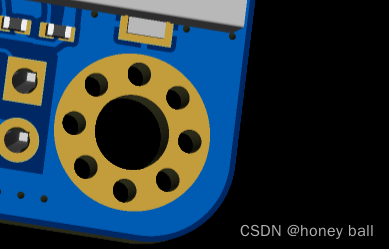

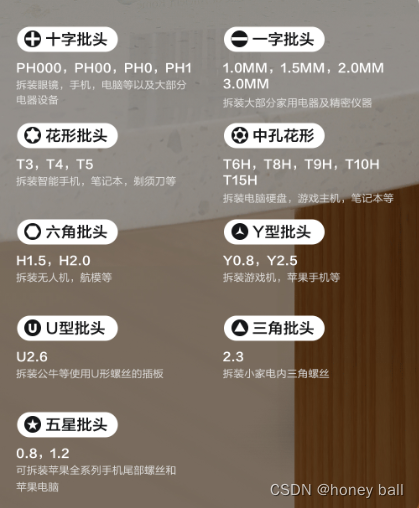

m3_梅花螺丝孔 封装:m3 125x300

、

、

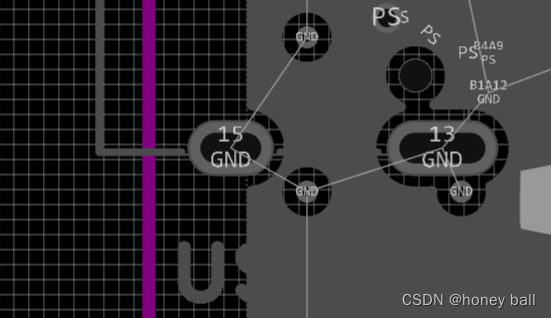

元件的GND引脚是无需连线的,只需要扇孔之后铺铜属性为GND即可连接。板子大面积GND打孔使减短回流路径。

这种方形的叫做方形焊盘,方便焊线。

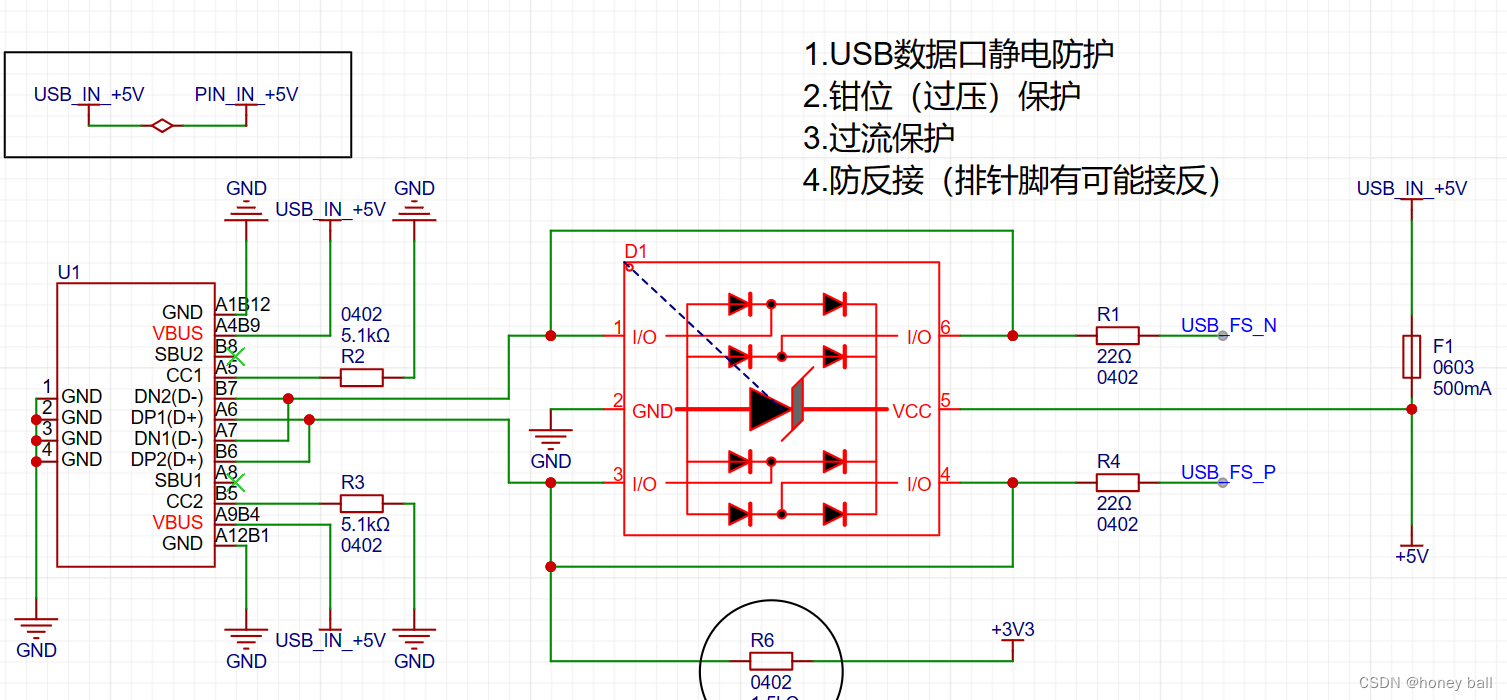

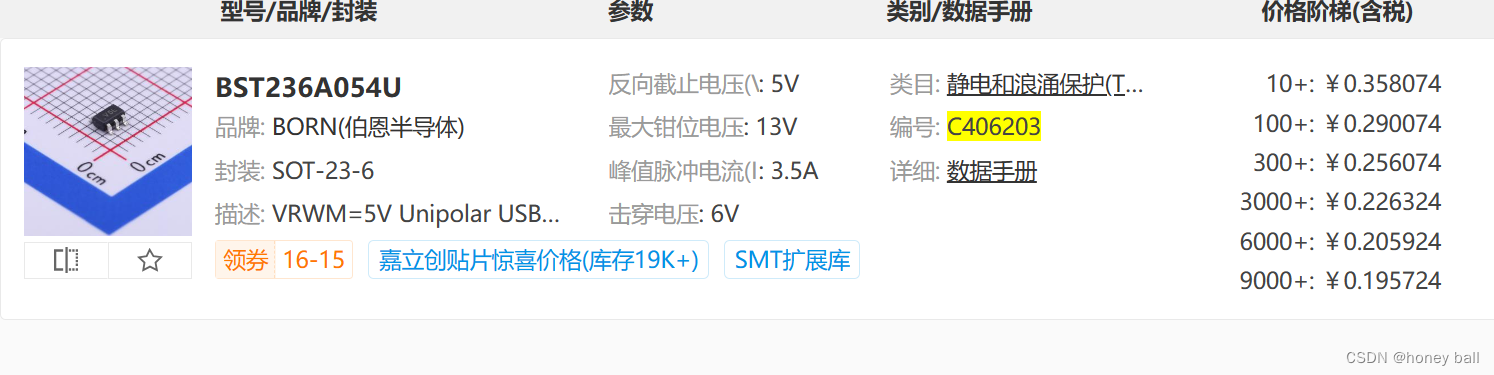

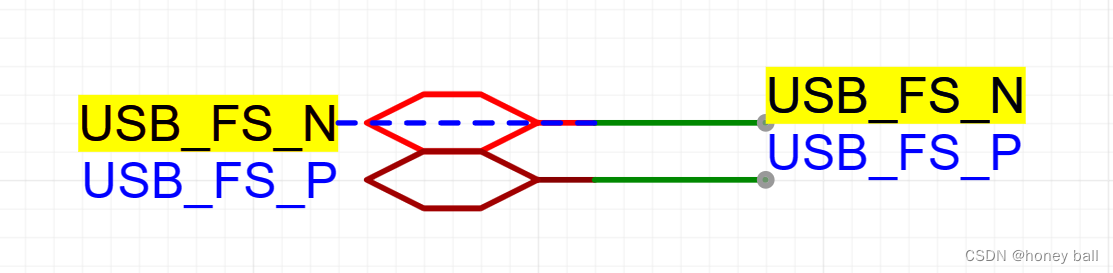

低成本,集成化的USB防护方案:

网络端口有两个用途:

1、图页内网络的相互连接

2、复用图块/层次图的连接

建议减少使用第一个用途,网络端口常用于层次图连接。

设计完板子后注意添加泪滴:

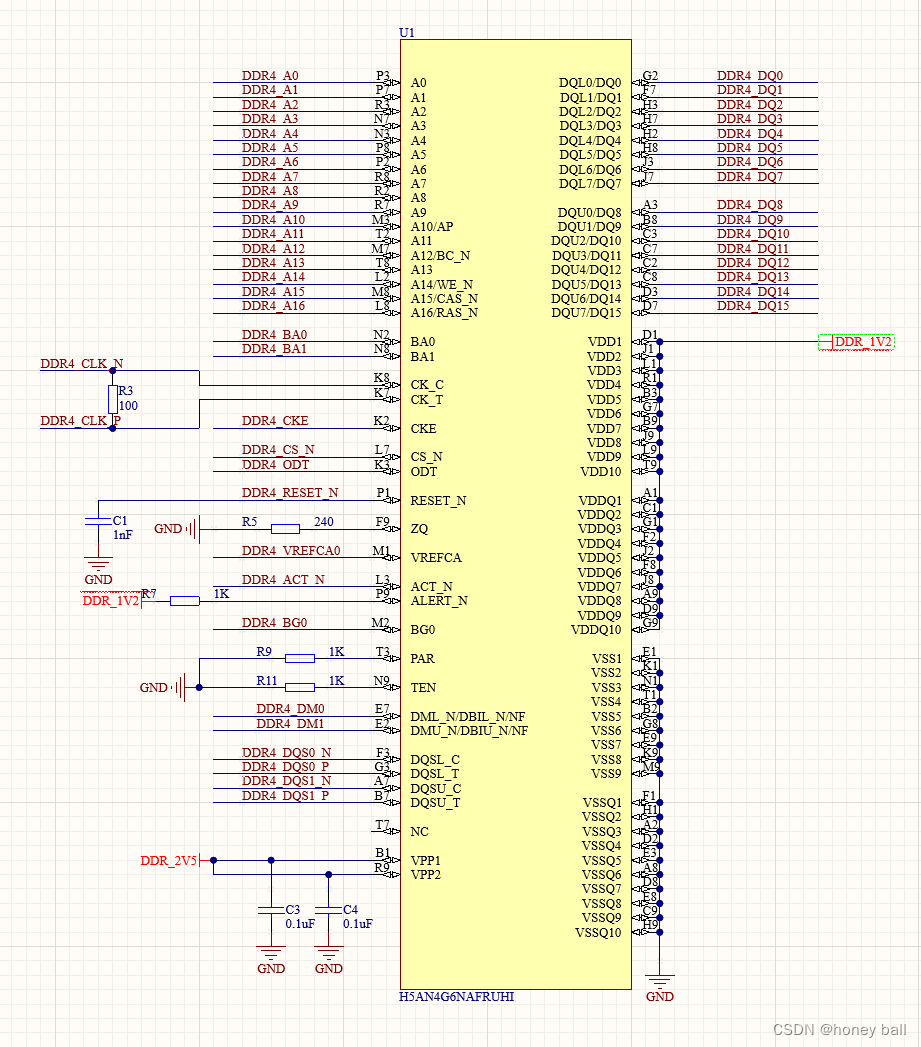

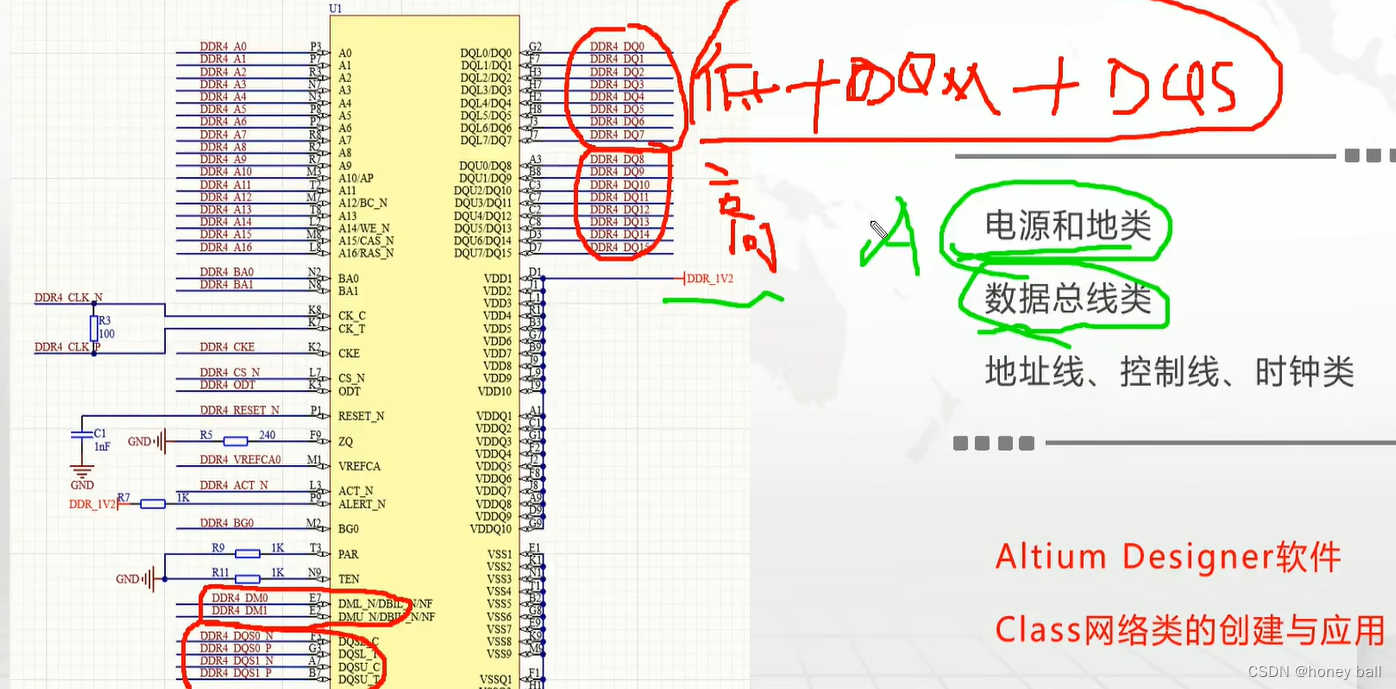

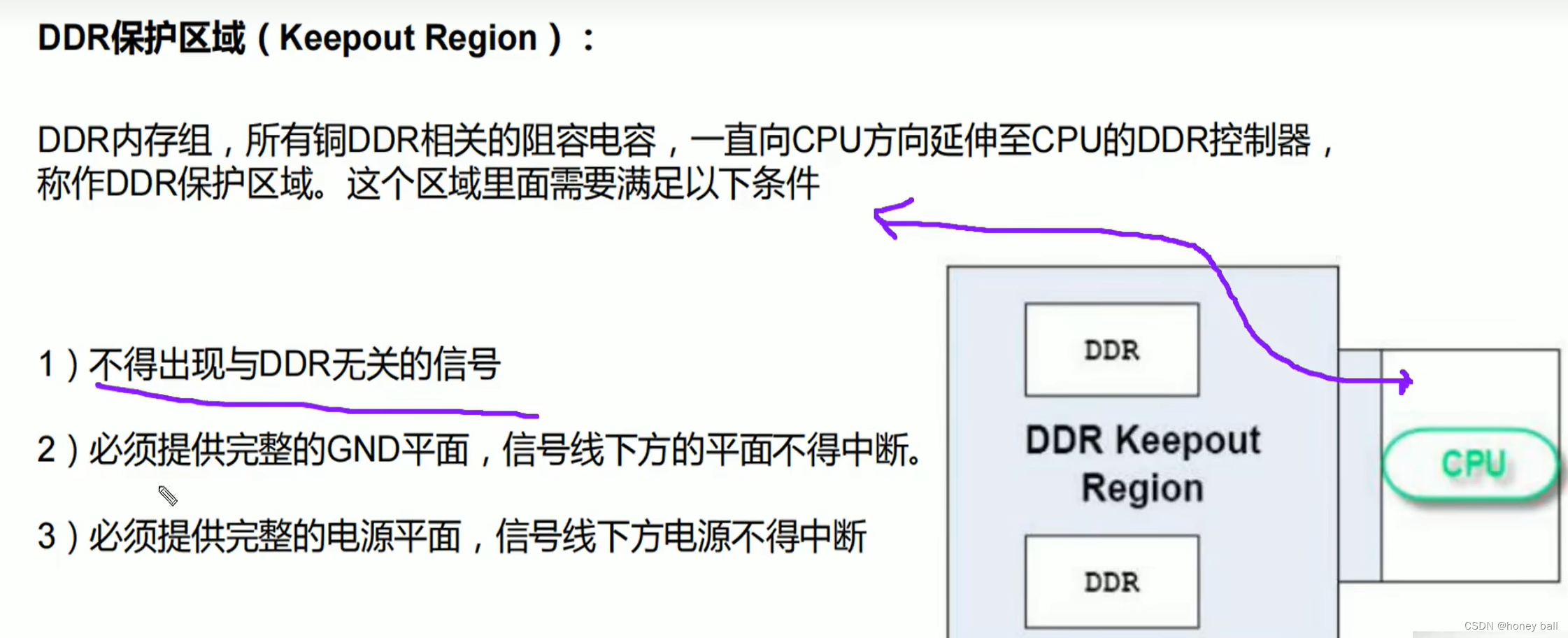

DDR:

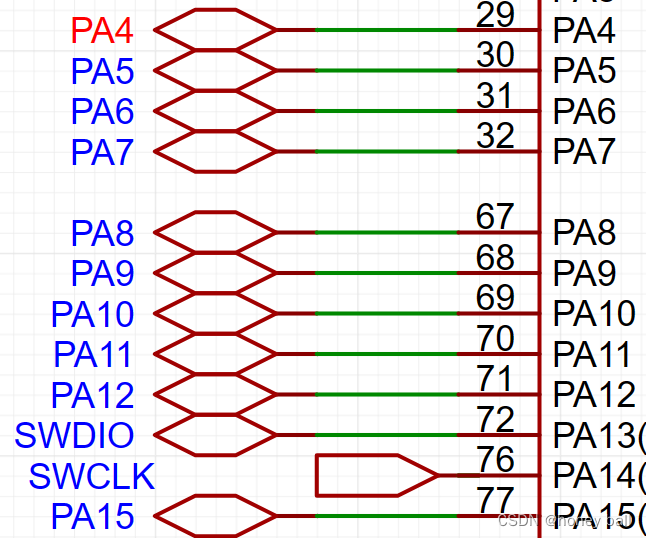

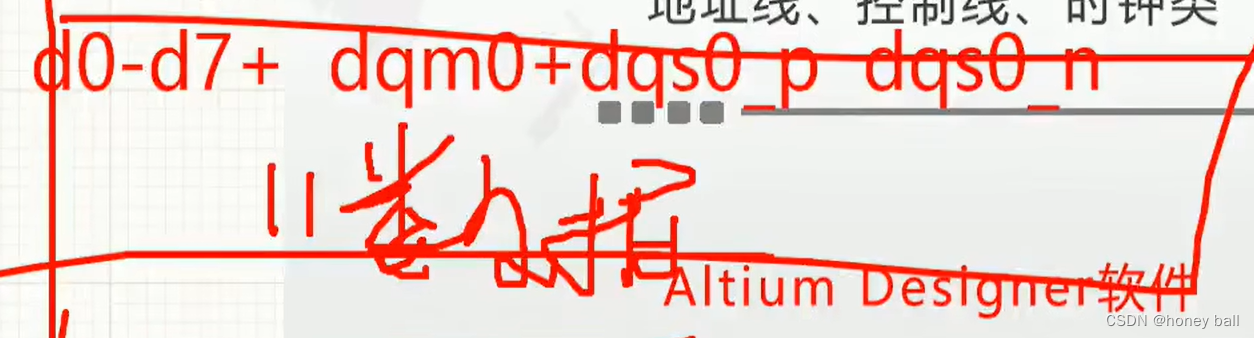

主要信号引脚包括DQ[0---8]低八位+DQ[9---16]高八位+DM数据掩码+DQS数据锁存信号(是两对差分线,低八位对应DQS0,高八位对应DQS1)

低八位的一组数据(低八位8PIN+数据掩码1PIN+数据锁存信号2PIN),高八位同样如此。

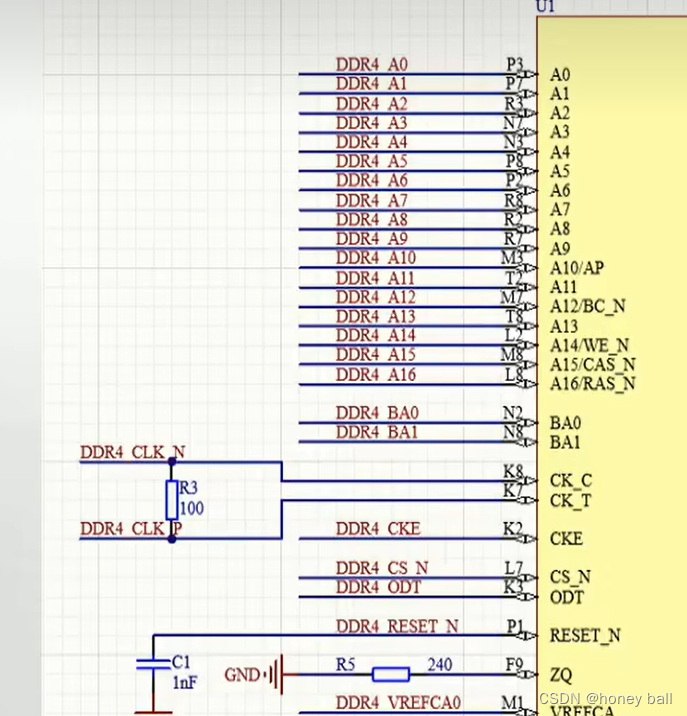

DDR的地址线,时钟线,片选线:

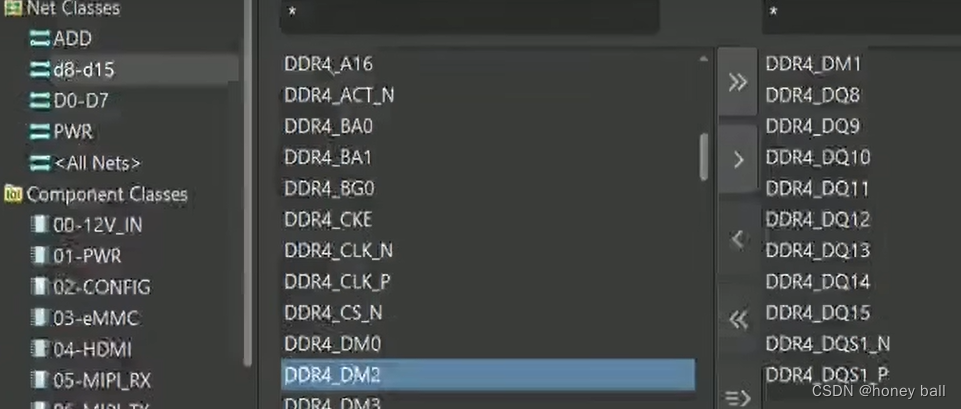

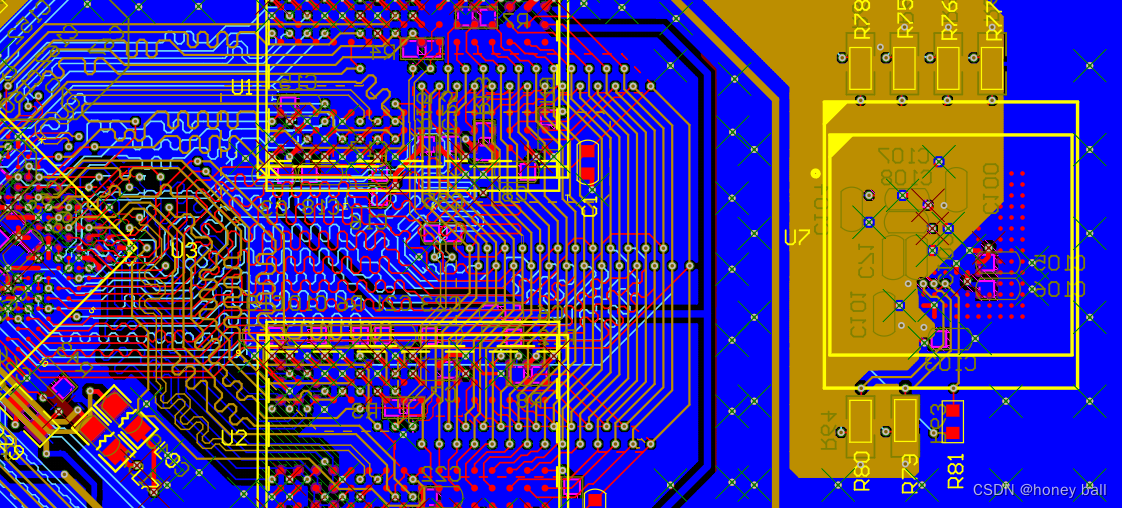

对DDR布线的时候,创建低八位组,高八位组,电源组:

D0-D7为一组低八位,共计11个引脚:

高八位一组:

控制信号,地址线一组,电源放在整个PCB的PWR组中:

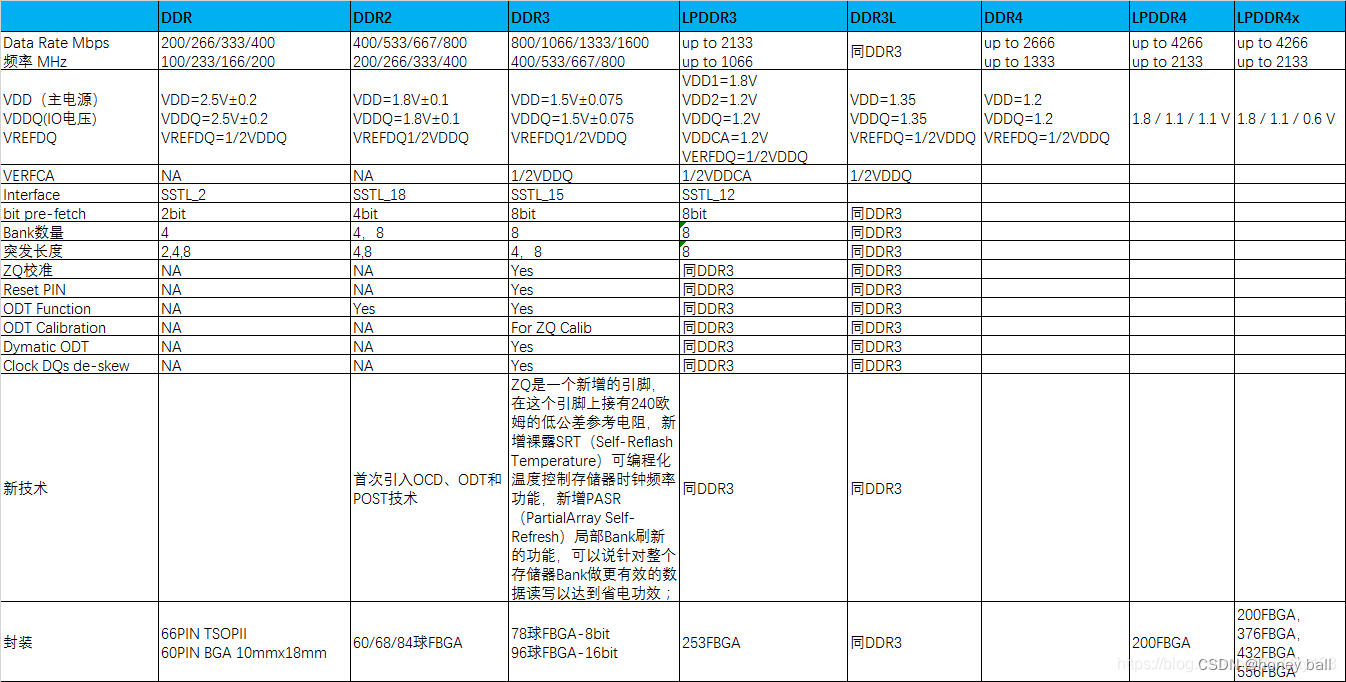

不同DDR的区别对照表:

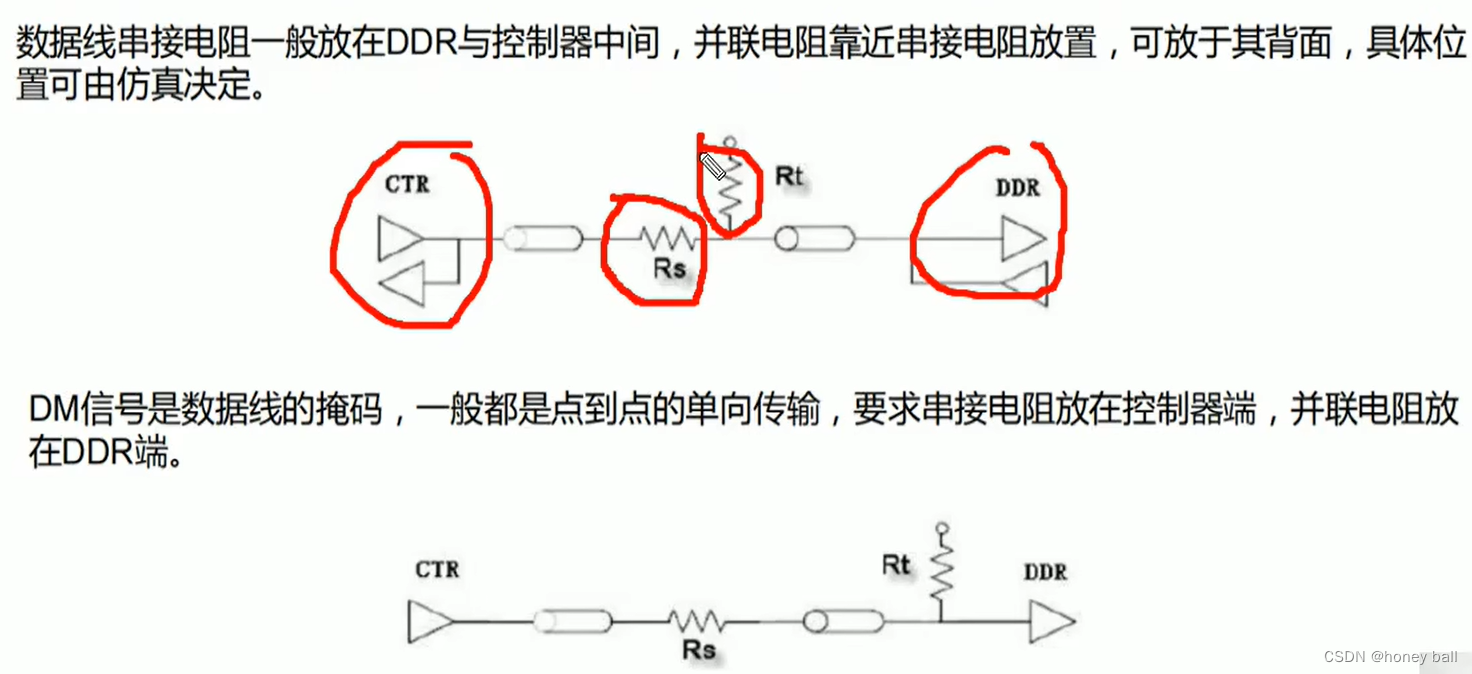

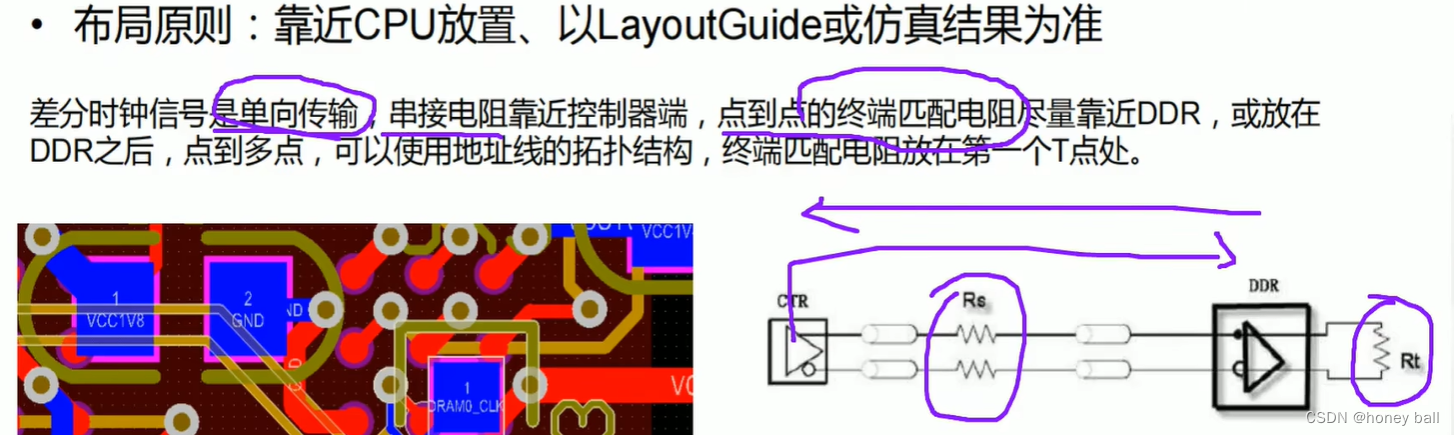

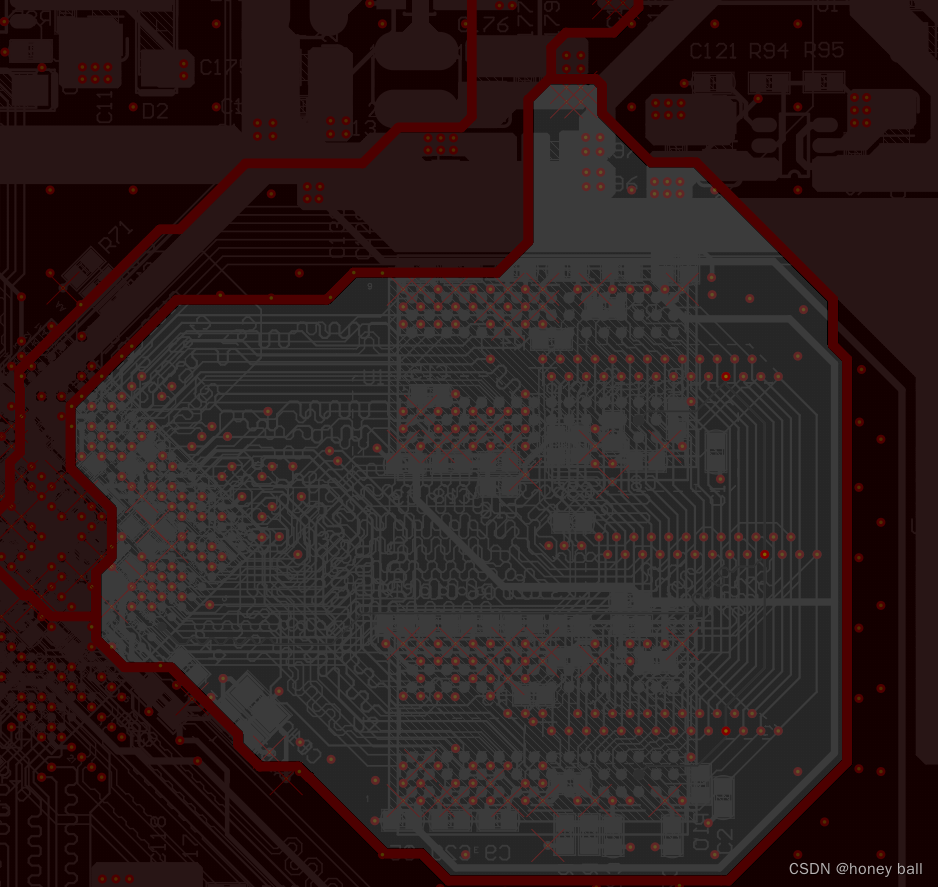

DDR串组,并组位置摆放:

DDR下方完整的电源平面:

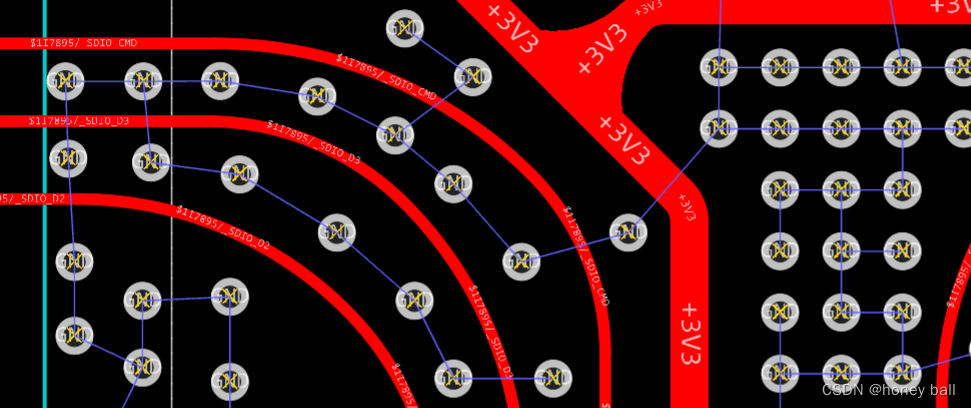

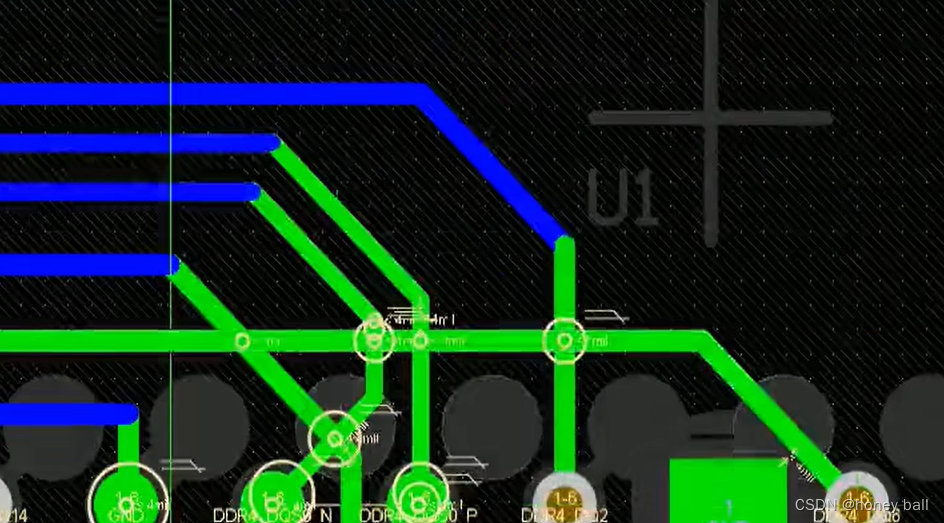

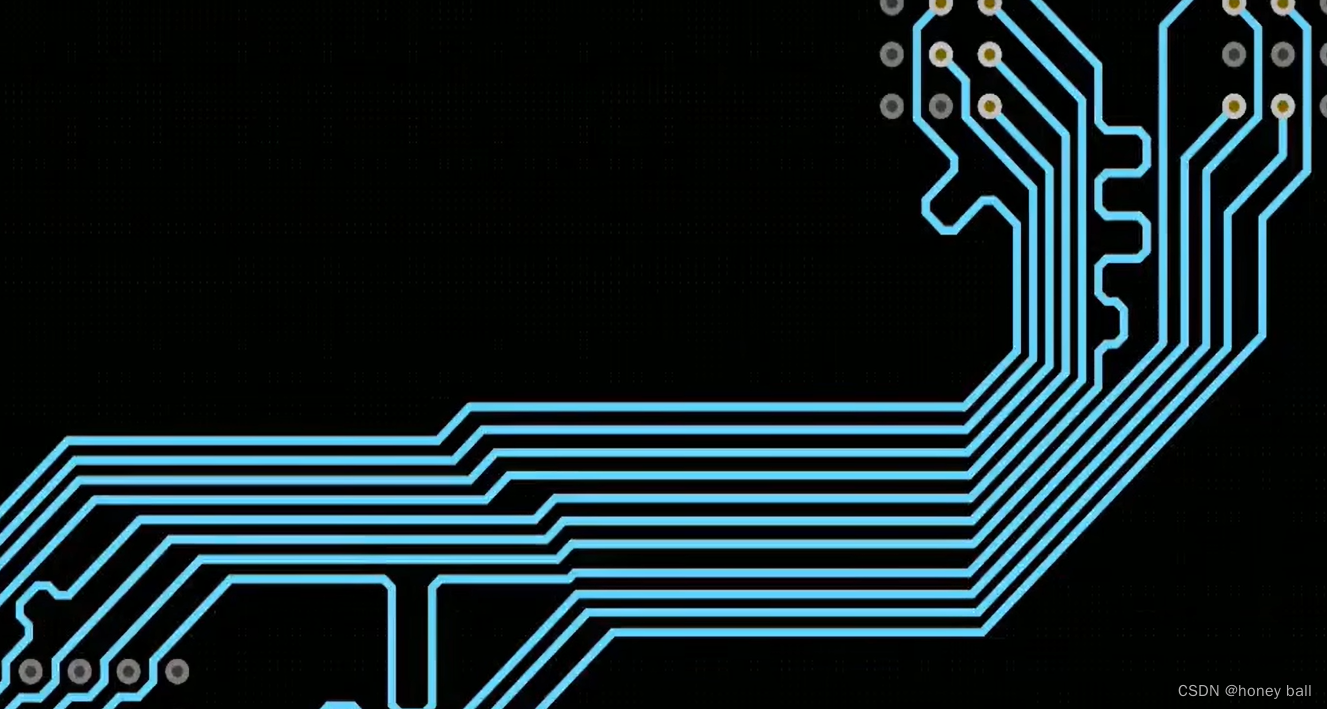

蛇形走线的作用为通过让每个导线尽可能等长,减缓不同导线之间的传输延迟。

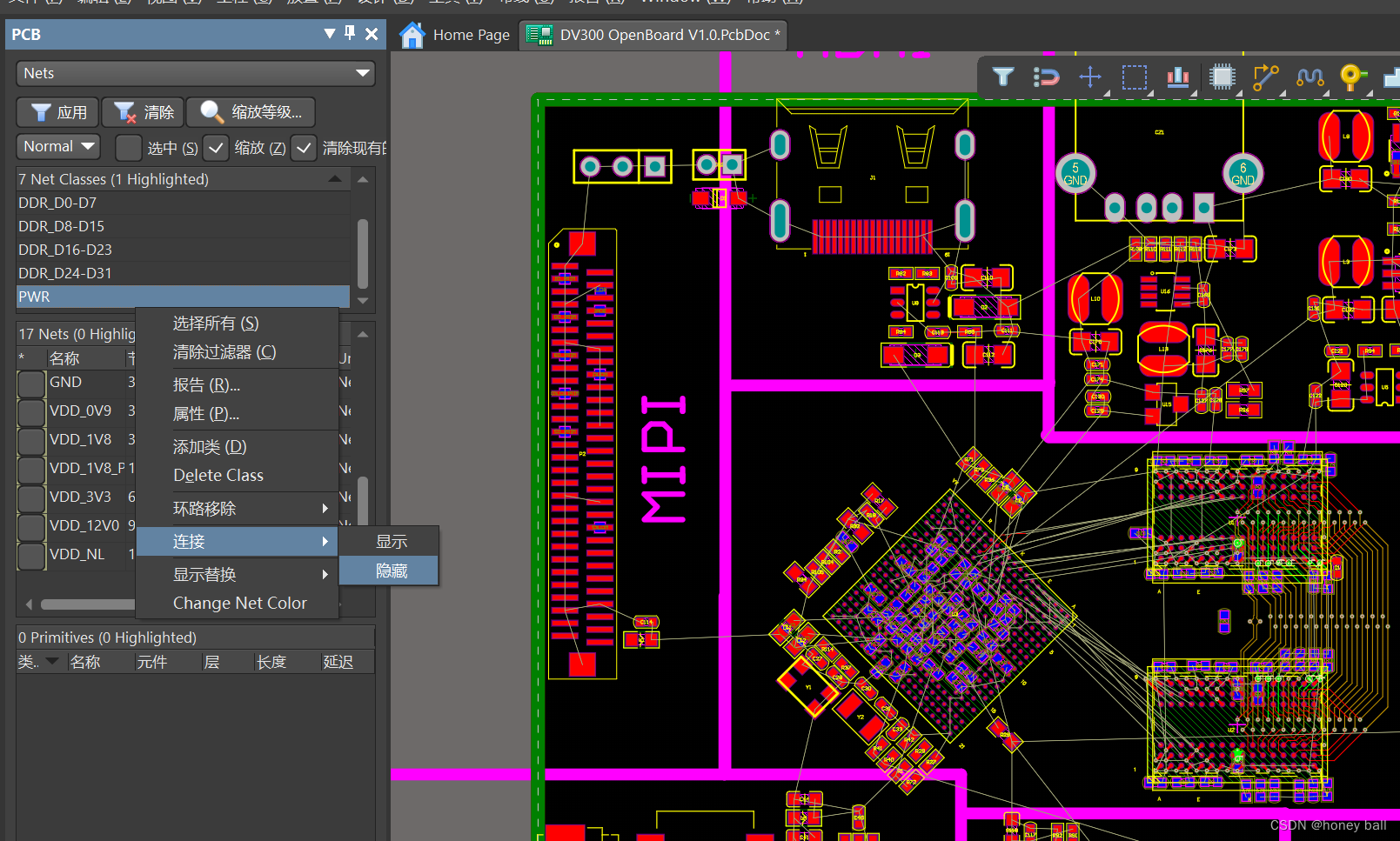

单独显示一个分组的连接引导线:

显示与隐藏一个器件的连接引导线:

当BGA器件扇出之后,外侧从表层拉线,内侧的引脚从其他信号层走线较为方便,有位置可以拉线。若线仍出不来,则进行合孔,移孔操作。

如果出现这种不可避免的导线交叉情况,则在导线初始部分即调整位置,换而言之是将BGA元件的交叉部分的线的过孔调整下位置,将每个线走顺。F:直观先连上,连线完一组后理顺线的位置,可以调整初始的过孔和末端的过孔的位置从而把线理顺。

/

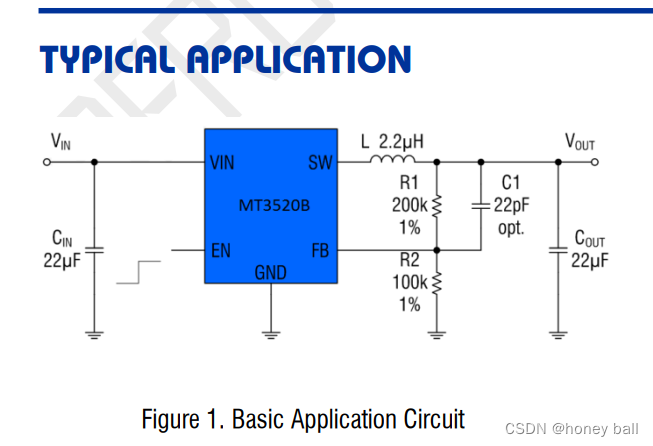

在DCDC电路中,电感选型通常不直接考虑Q值的原因:Q值代表了电感器的品质因数,它描述了电感器在谐振频率下的性能。然而,在DCDC电路中,电感器主要作为储能元件使用,其性能主要受到电感量、内阻(DCR)、额定电流、自谐振频率等因素的影响。在DCDC电路中,电感器的主要作用是平滑电流和滤波。其性能的好坏更多地体现在能否有效地存储和释放能量,以及能否有效地抑制纹波。这些性能主要受到电感器的电感量、内阻和饱和电流等参数的影响,而与Q值关系不大。

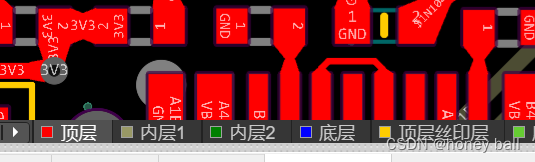

BGA走线的时候按照功能“一把走线”,为了给信号线更多的走线平面,内层1和内层2全部采用信号层。从BGA拉出后再向功能区拉线。

有些作者在每层都进行了铺铜 处理:原因是整个板子没有设计GND层,为了给信号拉线提供更多的板层。

蛇形等长走线,有什么作用:

补偿“同一组相关"信号线中延时较小的部分,这些部分通常是没有或比其它信号少通过另外的逻辑处理;最典型的就是时钟线,通常它不需经过任何其它逻辑处理,因而其延时会小于其它相关信号。在哪里用到蛇形等长走线:

(1)内存走线、DDR类、数据、地址、控制、时钟、USB等;要求高的视频、音频信号。

如果蛇形走线在电脑板中出现,其主要起到一个滤波电感的作用,提高电路的抗干扰能力,电脑主机板中的蛇形走线,主要用在一些时钟信号中,如CIClk,AGPClk,它的作用有两点:1、阻抗匹配2、滤波电感。对一些重要信号,如INTEL HUB架构中的HUBLink,一共13根,跑233MHz,要求必须严格等长,以消除时滞造成的隐患,绕线是唯一的解决办法。一般来讲,蛇形走线的线距>=2倍的线宽。PCI板上的蛇行线就是为了适应PCI 33MHzClock的线长要求。若在一般普通PCB板中,是一个分布参数的 LC滤波器,还可作为收音机天线的电感线圈,短而窄的蛇形走线可做保险丝等等.

(2)I2C无需等长布线,虽然I2C信号与内存一样都是有相对时序要求,但由于信号频率较低,此时导线长度引起的延时不足以影响正常时序,所以无需等长

//

高速板中每一层都需要正面铺铜处理:

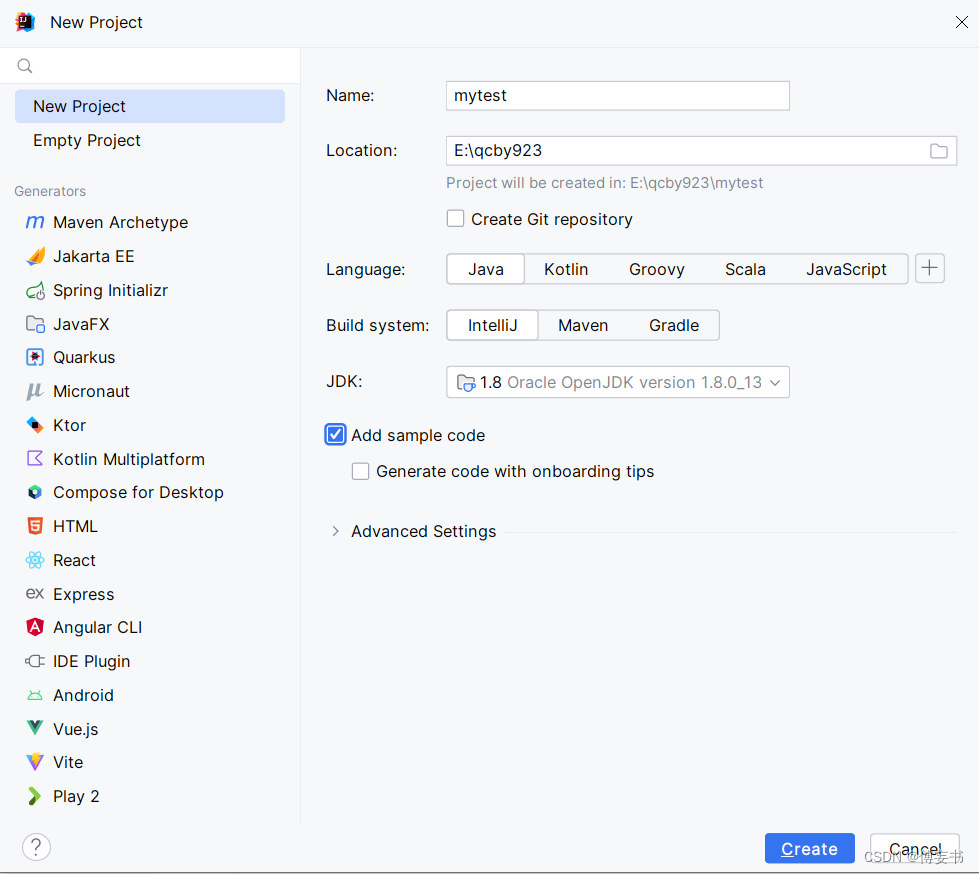

ActiveRoute:

布总线的时候很好用,尤其是画的板子还有DDR或SDRAM等高速存储器时,每一根线都要做等长处理,而且有时一组数据总线就有32根线,自己一条一条拉属实很费时间,用PCB ActiveRoute的话分分钟上百条线都给你自动连好,可以设置布线轨迹,还可以帮你做等长处理。

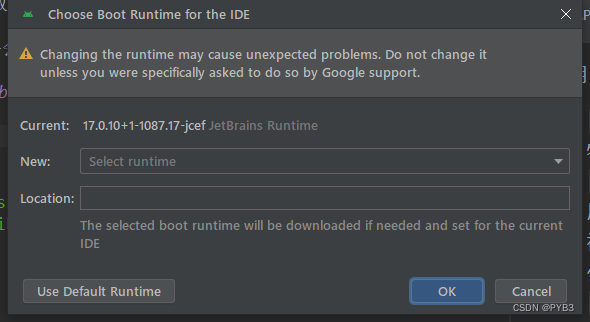

Altium Designer 找不到PCB ActiveRoute:

极其方便,非常方便!

下面的链接的第二种方法只针对正版授权的软件,可以试验下破解之后再用第二种方法。

Altium Designer 找不到PCB ActiveRoute_ad active route走线后不见-CSDN博客

一把数据线等长处理自动拉好:线走的漂不漂亮与规则设置有关。

设置好分组后电源线一把关闭或显示,非常方便。