在 FPGA 中,时钟分频是经常用到的。本节实现 2 分频、 3 分频、 4 分频和 8 分频的 Verilog 实现,以及仿真调试。

仿真步骤不是必须的,但是仿真可以发现很多我们设计的错误或者隐患问题,进而对设计进行调整。

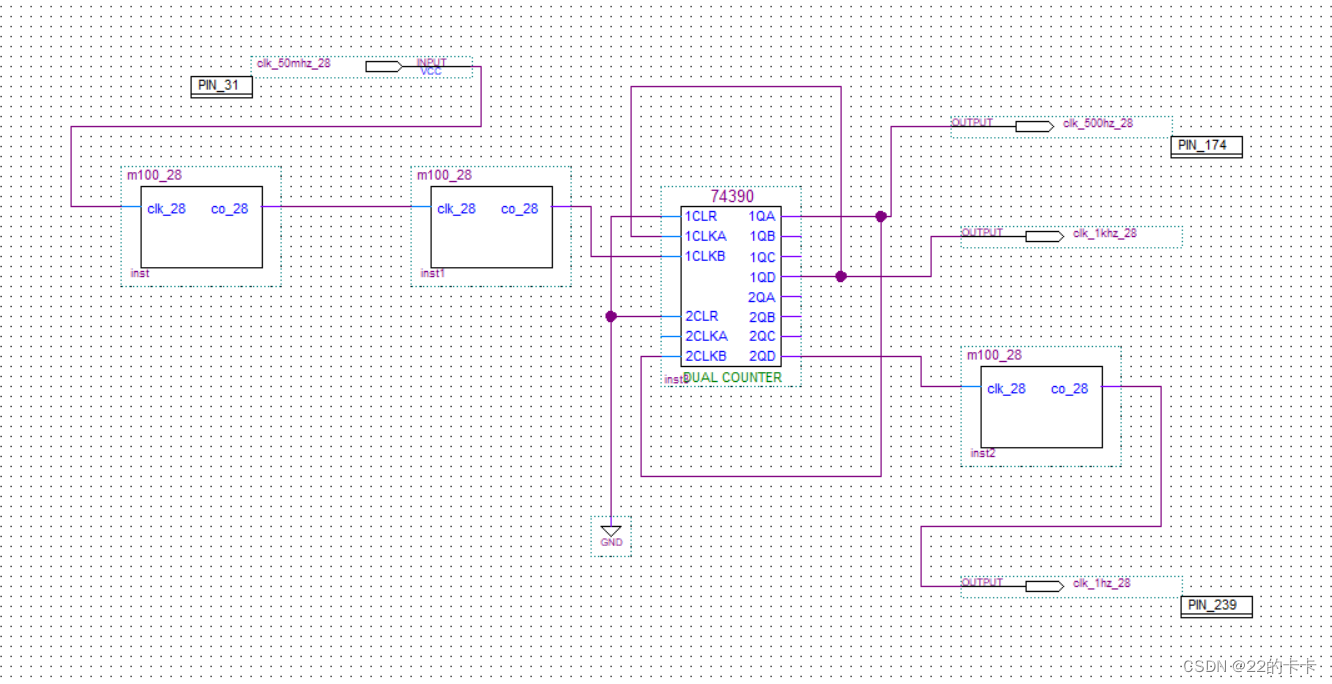

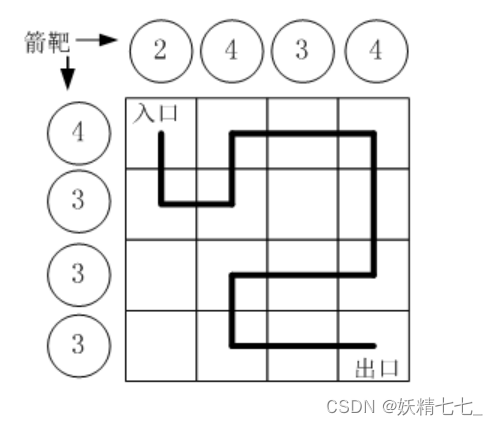

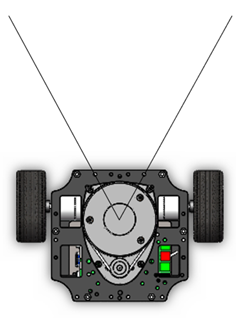

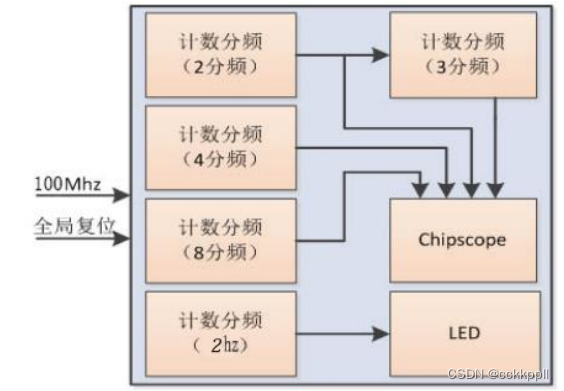

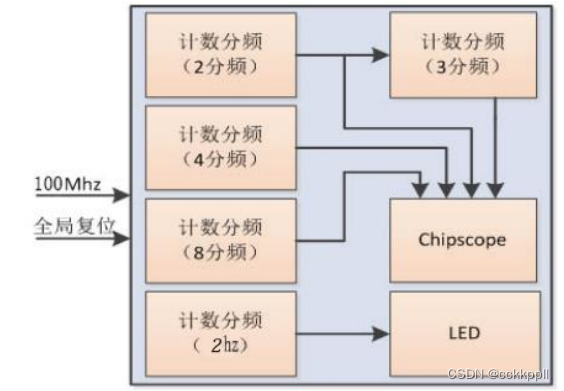

FPGA 输入全局时钟 100MHZ ,定义合适的分频计数器,得到对应的时钟。通过 chipscope 来抓取 2 分频、 3 分 频、4 分频和 8 分频结果,通过板子上的 LED 灯,来显示 2HZ 的时钟。设计总体框图如下所示

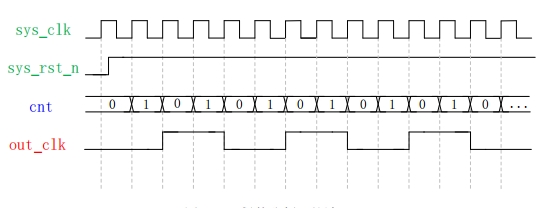

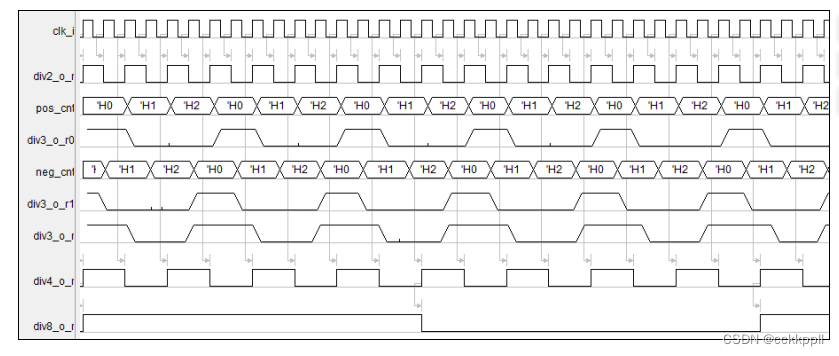

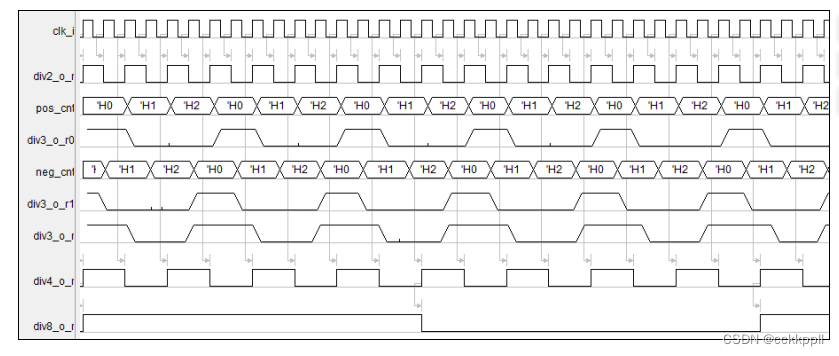

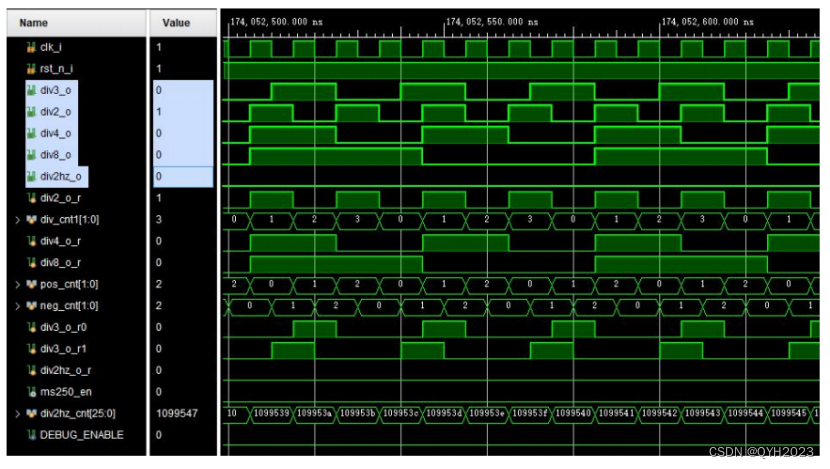

① 定义寄存器 div2_o_r ,检测输入时钟上升沿,每次上升沿寄存器 div2_o_r 反转一次,实现 2 分频。

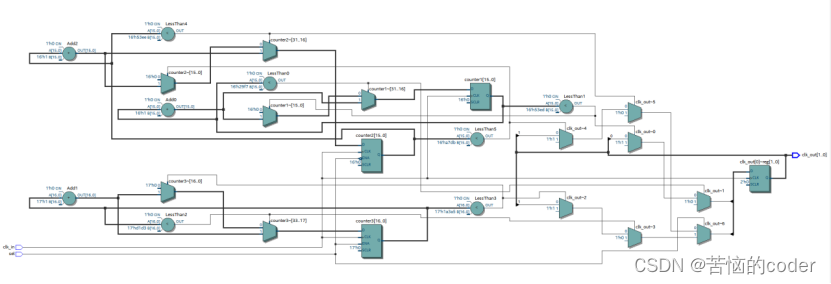

② 定义寄存器 pos_cnt[1:0] , neg[1:0] ,分别检测 div2_o_r 的上升沿和下降沿,检测到上升沿和下降沿时,两

个寄存器分别累加。计数到 2’d2 时,寄存器清零。另定义两个 div3_o_r0 和 div3_o_r1 ,当两个计数器小于 2’d1

时 ,div3_o_r0 和 div3_o_r1 均赋值为 1 ,其他情况赋值为 0 。由 div3_o_r0 和 div3_o_r1 组合逻辑相或即为 div2_o_r 进

一步进行 3 分频所得的结果。

③ 定义位宽为 2 的寄存器 div_cnt[1:0] ,检测输入时钟上升沿, div_cnt==2’b00 或 2’b01 , 4 分频输出寄存器

div4_o_r 反转, div_cnt==2’b00 时 ,8 分频输出寄存器 div8_o_r 反转。

④ 由于输入时钟 100MHZ ,为得到 2HZ 的时钟,需要定义计数器至少 100000000/1=100000000 。在此定义一

个 26 位位宽的 div2hz_cnt 计数器。检测输入时钟上升沿, div2hz_cnt==26’d24_999999 或 div2hz_cnt==26’d49_999999

时, 2HZ 输出寄存器 div2hz_o_r 反转。

![[米联客-安<span style='color:red;'>路</span>飞龙DR1-FPSOC] <span style='color:red;'>FPGA</span>基础篇连载-08 <span style='color:red;'>FPGA</span><span style='color:red;'>多</span><span style='color:red;'>路</span><span style='color:red;'>分</span><span style='color:red;'>频</span><span style='color:red;'>器</span><span style='color:red;'>实验</span>](https://i-blog.csdnimg.cn/direct/88692f3d3b0e4713ad7202444664e2bf.png)