介绍

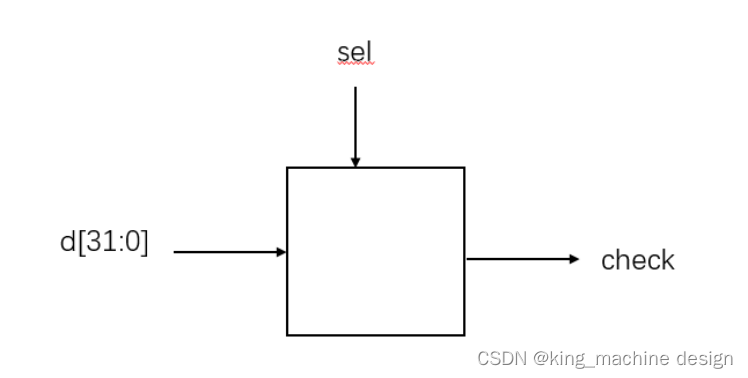

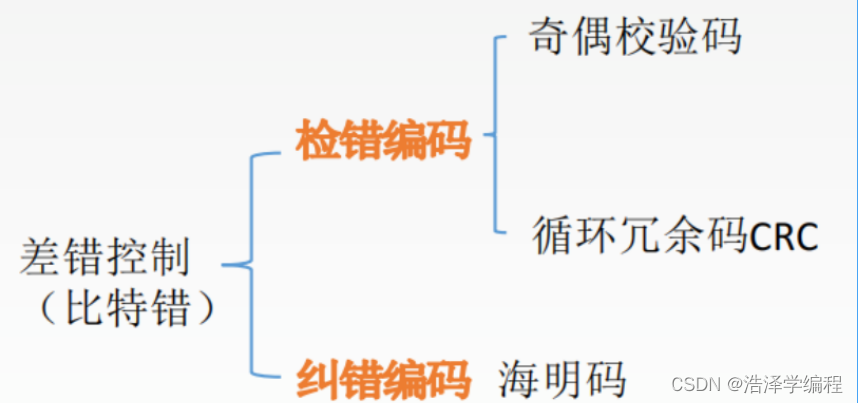

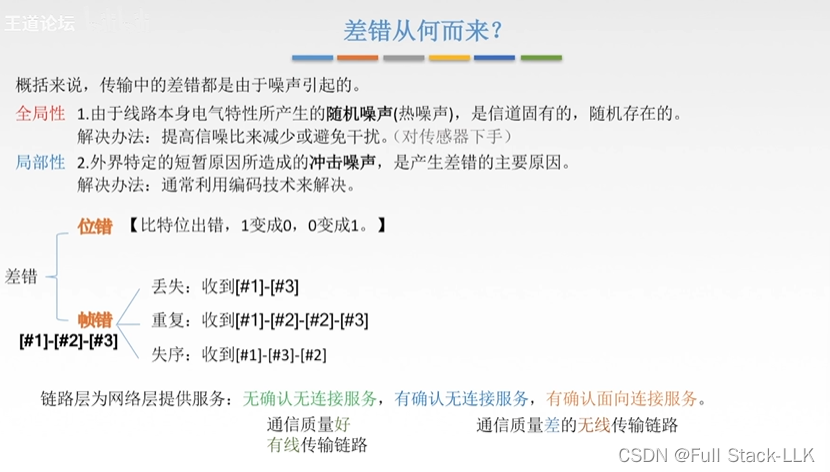

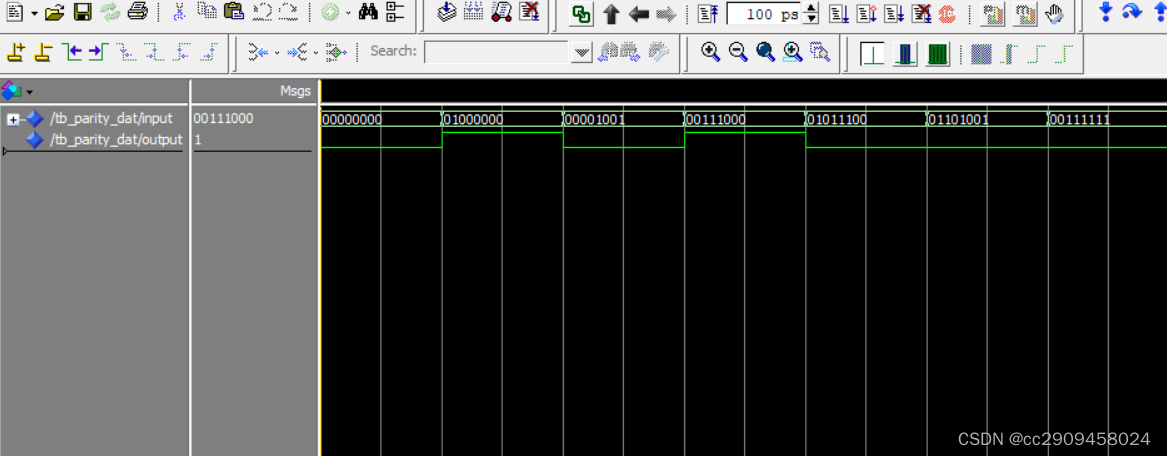

当输入n+1位宽的信号时,判断输入信号中1的个数,这就是奇偶校验。在我设计的电路中,当输入1的个数是偶数时,就输出0,输入1的个数是奇数时,就输出1。

我们这里设置的位宽为8。

另外,附录中的文件能够只输出偶数个1,有兴趣的小伙伴可以看看。

设计文件

library ieee;

use ieee.std_logic_1164.all;

entity parity_dat is

generic (n : integer := 7);

port(

input : in bit_vector (n downto 0);

output: out bit);

end parity_dat;

architecture parity_dat of parity_dat is

begin

process(input)

variable temp : bit;

begin

temp := '0';

for i in input'range loop

temp := temp xor input(i);

end loop;

output <= temp;

end process;

end parity_dat;

测试文件

library ieee;

use ieee.std_logic_1164.all;

entity tb_parity_dat is

generic (n : integer := 7);

end tb_parity_dat;

architecture parity_dat of tb_parity_dat is

component parity_dat is

port(

input : in bit_vector (n downto 0);

output: out bit);

end component parity_dat;

signal input : bit_vector (n downto 0);

signal output : bit;

begin

dut : parity_dat

port map(

input => input,

output => output);

process

begin

input <= "00000000";

wait for 20ns;

input <= "01000000";

wait for 20ns;

input <= "00001001";

wait for 20ns;

input <= "00111000";

wait for 20ns;

input <= "01011100";

wait for 20ns;

input <= "01101001";

wait for 20ns;

input <= "00111111";

wait for 20ns;

end process;

end parity_dat;

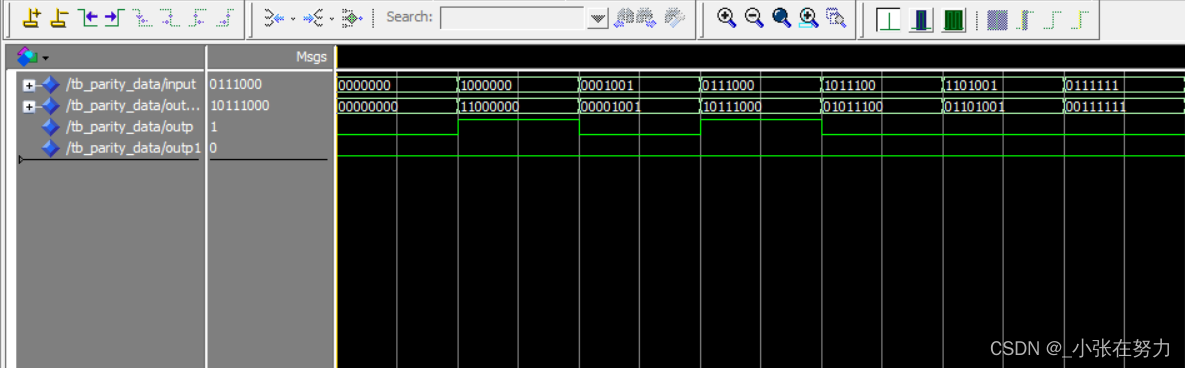

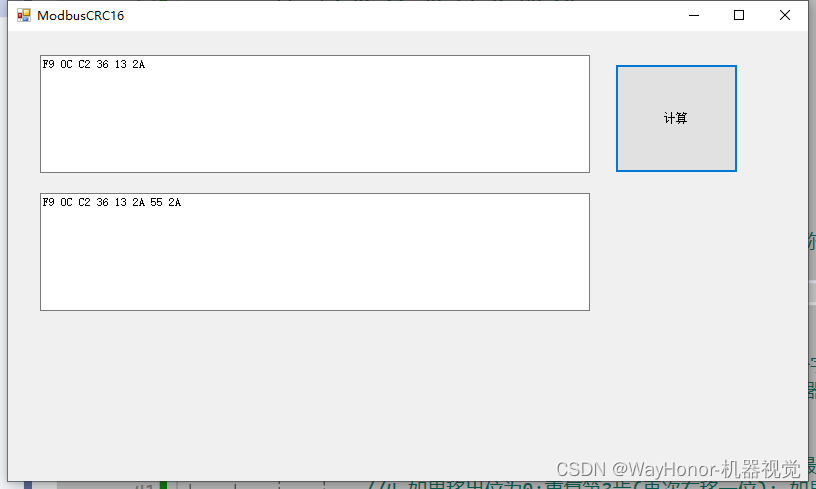

仿真结果

结语

有问题欢迎留言哈。

附录

以上我们就实现了对输入信号的奇偶校验,那么如果我们想让输出信号只有奇数个1或者偶数个1怎么办呢?我们通过在输入信号的左边增加1或者增加0,使输出信号只有偶数个1。

我在设计中设置了三个输出,从output中可以看到输入信号经过电路输出后的结果,从outp中可以看出输入信号中1的个数是奇数还是偶数,从outp1中可以看出经过设计的电路后,输出1的个数都变成了偶数。

设计文件

library ieee;

use ieee.std_logic_1164.all;

entity parity_data is

generic (n : integer := 7);

port(

input : in bit_vector(n-1 downto 0);

output: inout bit_vector(n downto 0);

outp : out bit;

outp1 : out bit

);

end parity_data;

architecture parity_data of parity_data is

begin

process(input)

variable temp1 : bit;

variable temp2 : bit_vector(output'range);

variable temp3 : bit;

variable temp4 : bit;

begin

temp1 := '0';

temp3 := '0';

temp4 := '0';

for i in input'range loop

temp1 := temp1 xor input(i);

temp2(i) := input(i);

temp3 := temp3 xor input(i);

end loop;

temp2(output'high) := temp1;

output <= temp2;

for j in output'range loop

temp4 := temp4 xor output(j);

end loop;

outp <= temp3;

outp1 <= temp4;

end process;

end parity_data;

测试文件

library ieee;

use ieee.std_logic_1164.all;

entity tb_parity_data is

generic (n : integer := 7);

end tb_parity_data;

architecture parity_data of tb_parity_data is

component parity_data is

port(

input : in bit_vector(n-1 downto 0);

output: inout bit_vector(n downto 0);

outp : out bit;

outp1 : out bit

);

end component parity_data;

signal input : bit_vector(n-1 downto 0);

signal output: bit_vector(n downto 0);

signal outp : bit;

signal outp1 : bit;

begin

dut : parity_data

port map(

input => input,

output => output,

outp => outp,

outp1 => outp1

);

process

begin

input <= "0000000";

wait for 20ns;

input <= "1000000";

wait for 20ns;

input <= "0001001";

wait for 20ns;

input <= "0111000";

wait for 20ns;

input <= "1011100";

wait for 20ns;

input <= "1101001";

wait for 20ns;

input <= "0111111";

wait for 20ns;

end process;

end parity_data;