功率优化是一个可选步骤,它通过使用时钟门控来优化动态功率。它既可以在Project模式下使用,也可以在Non-Project模式下使用,并且可以在逻辑优化之后或布局之后运行,以减少设计中的功率需求。功率优化包括Xilinx的智能时钟门控解决方案,这些解决方案可以在不改变功能的前提下,减少设计中的动态功率。

一、Vivado功率优化工具

Vivado功率优化工具会分析设计的所有部分,包括legacy和第三方IP块。它还会识别出可以将活动变化信号进行时钟门控的机会,因为这些信号并非在每个时钟周期都被读取。这减少了切换活动,进而降低了动态功耗。

1、使用时钟使能(CEs)

Vivado功率优化器充分利用了丰富的时钟使能(CEs)资源。功率优化会创建门控逻辑来驱动寄存器时钟使能,以便寄存器只在相关的时钟周期捕获数据。

在实际的硅芯片中,CEs实际上是用于门控时钟,而不是在D输入和触发器反馈Q输出之间进行选择。这提高了CE输入的性能,同时也降低了时钟功耗。

Vivado工具通过智能地应用时钟门控技术和其他功耗降低策略,帮助设计者创建出功耗更低、效率更高的FPGA设计。这种优化不仅减少了功耗,而且通常不会对设计的性能产生负面影响。

2、智能时钟门控

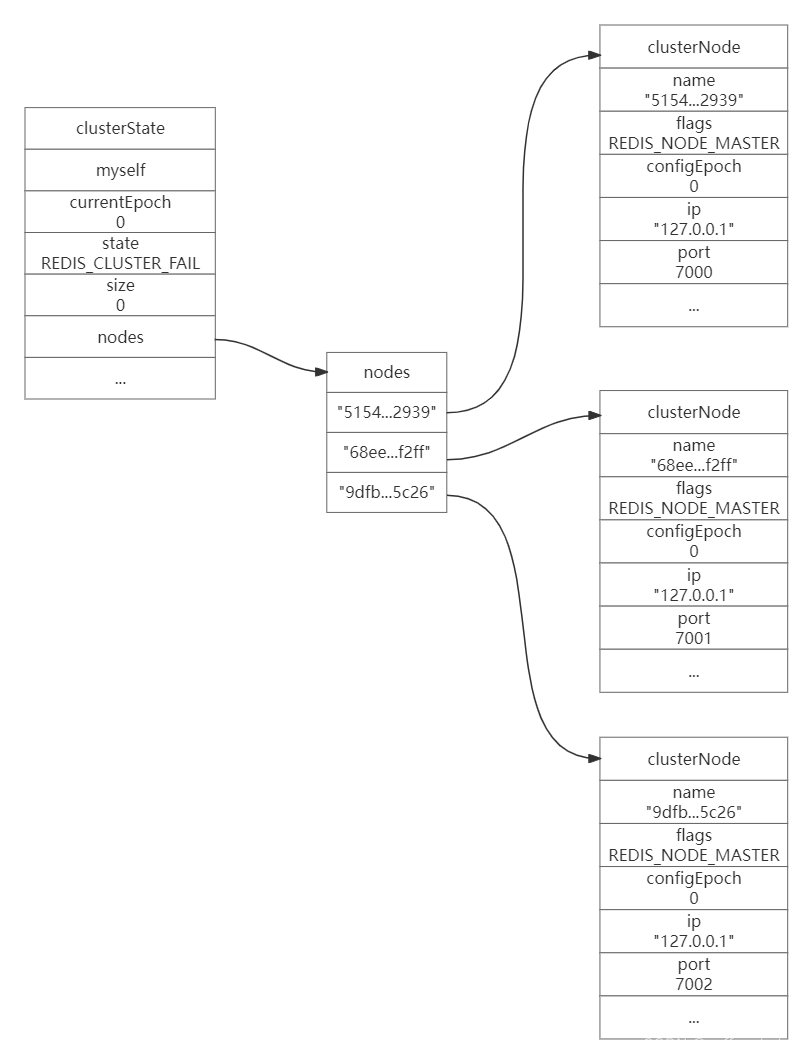

智能时钟门控还可以减少简单双端口或真双端口模式下专用块RAM的功耗,如下图2所示。

这些块包括多个使能信号:

• 数组使能(Array enable)

• 写使能(Write enable)

• 输出寄存器时钟使能(Output register clock enable)

大部分的功耗节省来自于使用数组使能。Vivado功率优化器实现了在没有数据写入且输出未被使用时减少功耗的功能。

通过智能地管理这些使能信号,Vivado工具能够在不需要访问或更新块RAM时关闭相关的时钟和电源,从而显著减少功耗。这种优化特别适用于那些块RAM使用模式不连续或仅在特定时间段内需要访问的设计。

除了数组使能之外,Vivado还会考虑写使能和输出寄存器时钟使能等其他因素,以进一步优化功耗。这些优化策略共同工作,确保在不影响设计功能的前提下最大限度地降低功耗。

二、power_opt_design

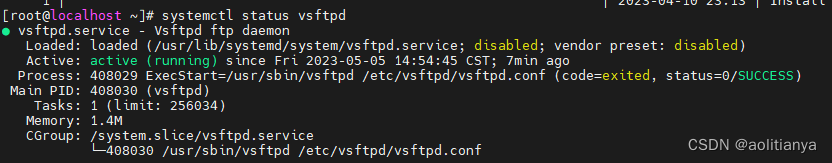

power_opt_design 命令用于分析和优化设计。默认情况下,它会分析和优化整个设计。该命令还执行智能时钟门控以优化功耗。

power_opt_design 语法:

power_opt_design [-quiet] [-verbose]

如果不想分析和优化整个设计,可以使用 set_power_opt 命令来配置优化器。还可以使用 set_power_opt 来指定 opt_design 中用于优化的特定块RAM单元。

set_power_opt 的语法如下:

set_power_opt [-include_cells <args>] [-exclude_cells <args>] [-clocks <args>] [-cell_types <args>] [-quiet] [-verbose]

如果使用 opt_design 运行,块RAM功耗优化将被跳过。

建议:如果希望在 opt_design 期间防止对特定块RAM进行块RAM功耗优化,请使用 set_power_opt -exclude_cells [get_cells <bram_insts>]。这允许通过指定要排除的块RAM实例来精确控制哪些块RAM会被包含在功耗优化中。通过这样做,可以确保只有关心的部分进行优化,同时保持其他部分的功耗优化被禁用。

要在 Vivado集成设计环境中通过power_opt_design启用功耗优化,您可以通过选择“Tools”→ “Project Settings”→ “Implementation”→ “Power Opt Design”来检查可用的is_enabled选项,如以下图3所示。启用后,功耗优化将作为Vivado集成设计环境中实现步骤的一部分运行。

功耗优化设计可以在设计流程中的放置前(pre-place)或放置后(post-place)启用,但不能同时在两个地方启用。

在Vivado中启用功耗优化时,务必注意其在设计流程中的位置。放置在前的优化(pre-place)可能在逻辑和布局优化之前进行,而放置在后的优化(post-place)则在布局和布线完成后进行。

三、显示功耗优化报告

在Vivado中,功耗优化是在Vivado设计流程的opt_design和power_opt_design阶段执行的。这两个阶段都发生在实现过程中,这是在设计被合成之后进行的。

1、 synthesis后生成功耗优化报告

该报告将只包含有关功耗优化特性的信息,这些特性是编码到原始设计中的(例如,使用时钟使能(CE)对块RAM进行门控)。报告不会详细列出工具在实现过程中后来执行的功耗优化。

2、 implementation后生成功耗优化报告

①打开Vivado项目,点击Open Synthesized Design 或 Open Implemented Design。

②点击Reports → Report Power Optimization。

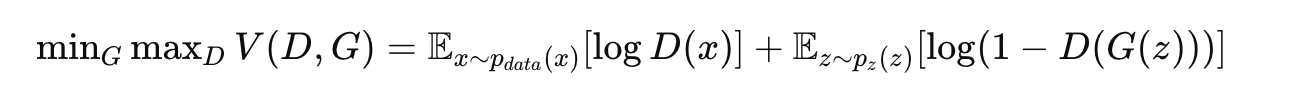

在“Report Power Optimization”对话框中(上图4),可以指定以下选项:

• 结果名称(Results name):指定功耗优化报告在Vivado IDE中的显示名称。这个名称将用于在IDE的报告中标识和引用该报告。

• 导出到文件(Export to file):勾选此选项以在Vivado IDE的功耗优化报告之外,额外生成一个文本报告。需要指定文本报告的文件名和保存位置,并选择文件格式是TXT还是XML。

• 在新标签页中打开(Open in a new tab):勾选此选项以将新的功耗优化报告添加到Vivado IDE中当前显示的其他功耗优化报告中。如果希望保留当前在Vivado中显示的功耗优化报告,请不要勾选此选项,因为新报告将会替换当前显示的报告。

设置完这些选项后,可以点击“OK”或相应的按钮来生成并显示功耗优化报告。

③或者执行相关的Tcl命令:

report_power_opt -name <report_name>

④新的功耗优化报告将显示在IDE的结果窗口区域中。在Vivado IDE中,结果窗口通常用于展示各种设计分析、合成和实现步骤的输出结果。

• 通用信息(General Information)

包含有关设计、在其中实现设计的AMD设备以及生成此功耗优化报告的Tcl命令的信息。这些信息对于理解报告的背景和上下文非常重要。

• 摘要(Summary)

列出了在设计中由用户优化以及由功耗优化工具优化的块RAM(Block RAMs)、SRLs(Shift Register Lookups)和Slice寄存器的数量。这提供了一个关于功耗优化所影响的资源类型的概览。

• 推荐(Recommendations)

提供了一些建议,帮助您进一步针对功耗优化您的设计。这些建议可能包括更改设计策略、使用不同的单元类型或配置,或者应用特定的优化技术。

• 层次结构信息(Hierarchical Information)

详细列出了Vivado针对其执行了功耗优化的块RAMs、SRLs和Slice寄存器的信息。这可能包括它们在设计中的位置(层次结构路径)、优化前后的功耗值,以及具体的优化策略或更改。

通过查看这些信息,可以更深入地了解功耗优化工具是如何影响您的设计的,并据此作出进一步的优化决策。这些信息对于设计工程师来说是非常有价值的,因为它们不仅提供了功耗优化的当前状态,还指出了可能进一步降低功耗的潜在领域。

提示:如果在任何层次结构的模块或实例上标记了DONT_TOUCH属性,功耗优化将不会优化这部分逻辑。

![笔记:[dv-admin开发系列]--2.0版本环境搭建](https://img-blog.csdnimg.cn/direct/61d482e4c0d24c808b1540874e700c22.png)