文章目录

前言

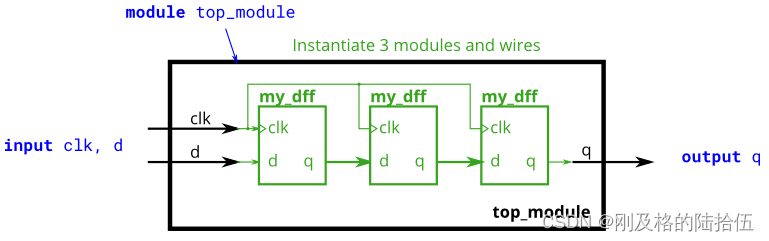

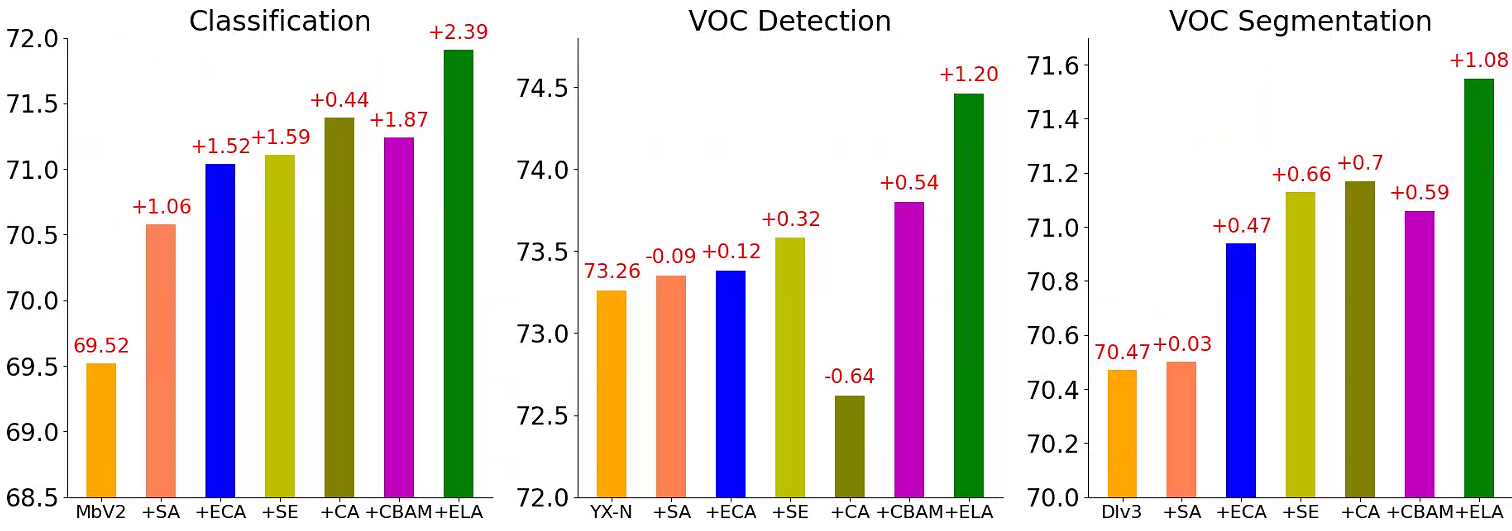

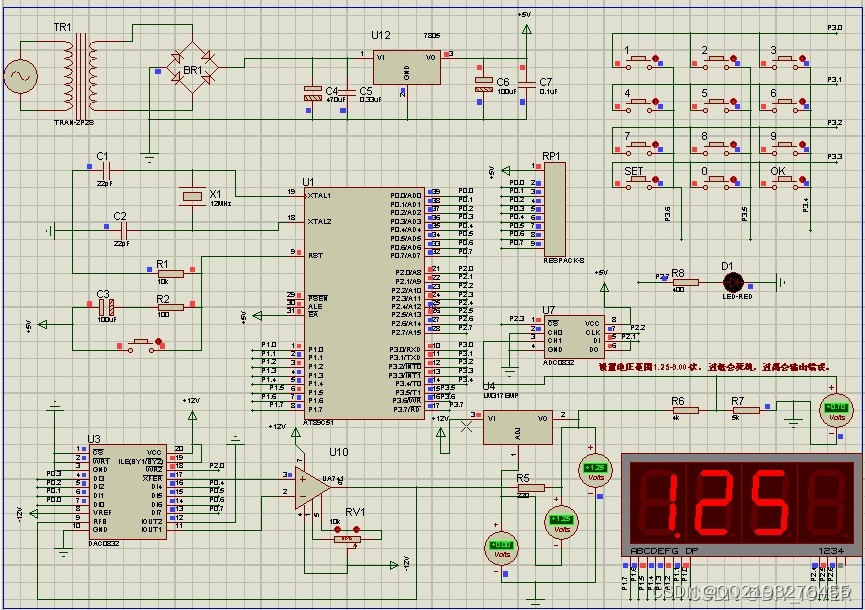

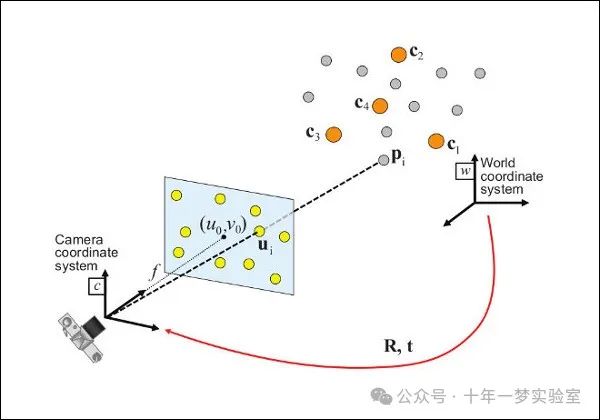

每个channel的时钟结构如图:

Transceiver内部时钟来源可以是QPLL也可以是自己的CPLL。其内部TX 和 RX 时钟分频器可以单独从 QPLL 或 CPLL 中选择时钟,允许 TX和 RX 数据通道使用不同的参考时钟输入在异步频率工作。这个单独二字表明了TX和RX可以独立的选择时钟分频器的时钟来源。CPLL的输出输入到 TX 和 RX 时钟分频器模块,控制 PMA 和 PCS 模块使用的串行和并行时钟的生成。如果 TX和 RX 数据通道的运行速率是相同 VCO (压控振荡器)频率的整数倍,则可以在它们之间共享 CPLL。

一、CPLL工作原理

CPLL工作原理是:

输入时钟在进入相位频率检测器之前可以被除以M的系数。 反馈分频器N1和N2决定了VCO的乘法比率和CPLL的输出频率。锁定指示块比较参考时钟和VCO反馈时钟的频率,以确定是否已实现频率锁定。(建议这段话配合下面的公式一起理解)

GTX收发器中的CPLL的额定工作范围在1.6 GHz至 3.3 GHz。GTH收发器中的CPLL的标称工作范围为 1.6 GHz至5.16 GHz。7系列FPGAs Transceiver Wizard根据应用要求选择适当的CPLL设置。

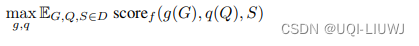

下面两个公式决定了PLL时钟输出频率以及transceiver的线速率:

如下Aurora标准协议的线速率与外部参考时钟之间的关系:

一些协议显示为单速率配置和多速率配置。在单速率配置中,只需要一个线速,参考时钟为该特定线速进行了优化。在多速率配置中,为最高的线路速率选择参考时钟,并选择适当的分频器来支持较低的线路速率。

二、QPLL工作原理

输入的时钟在进入相位频率检测器之前可以被除以一个系数M。反馈分频器N决定了VCO的乘法比率。QPLL的输出频率是VCO频率的一半。锁定指示块比较参考时钟和VCO反馈时钟的频率,以确定是否已经实现了频率锁定。

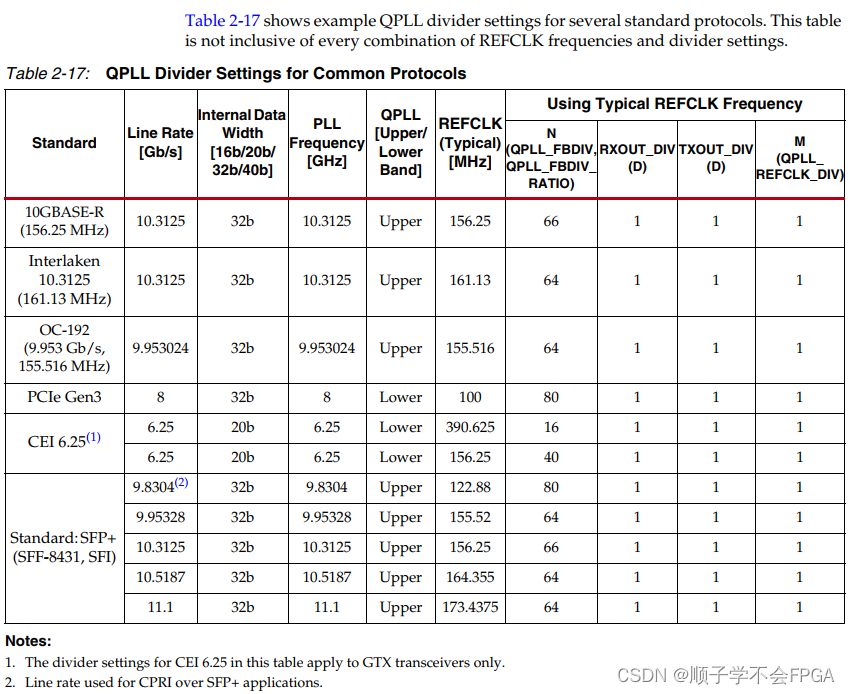

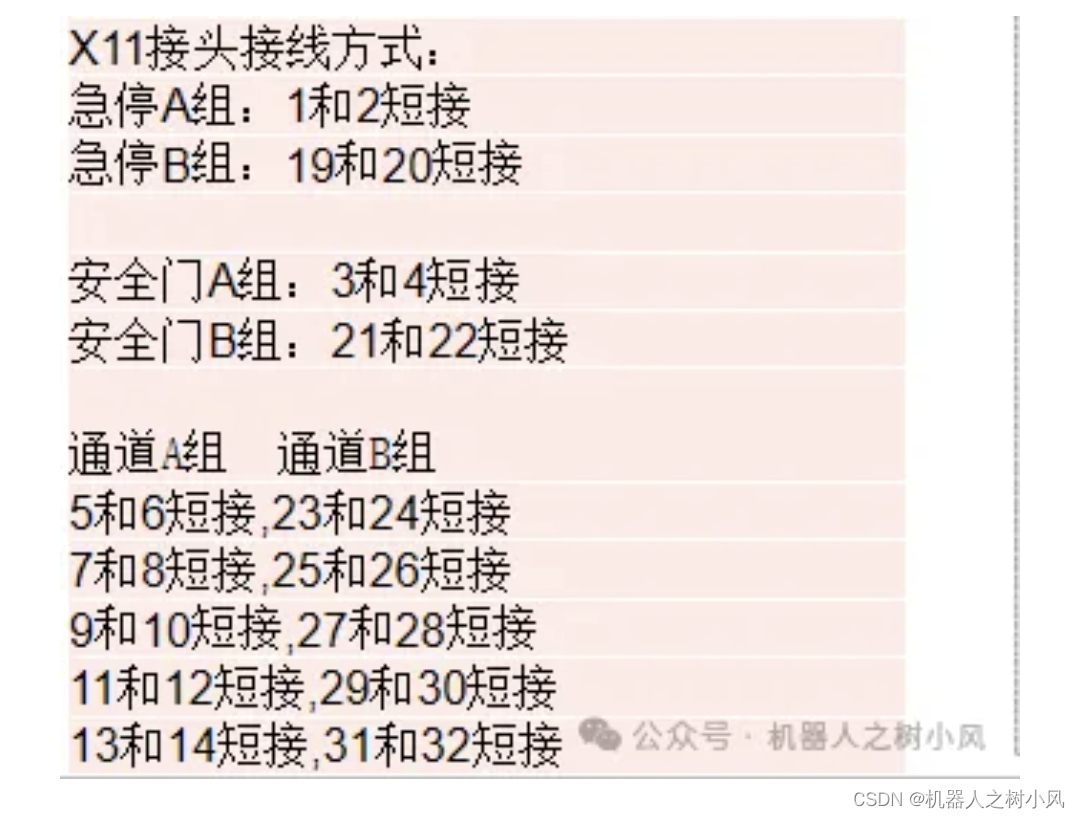

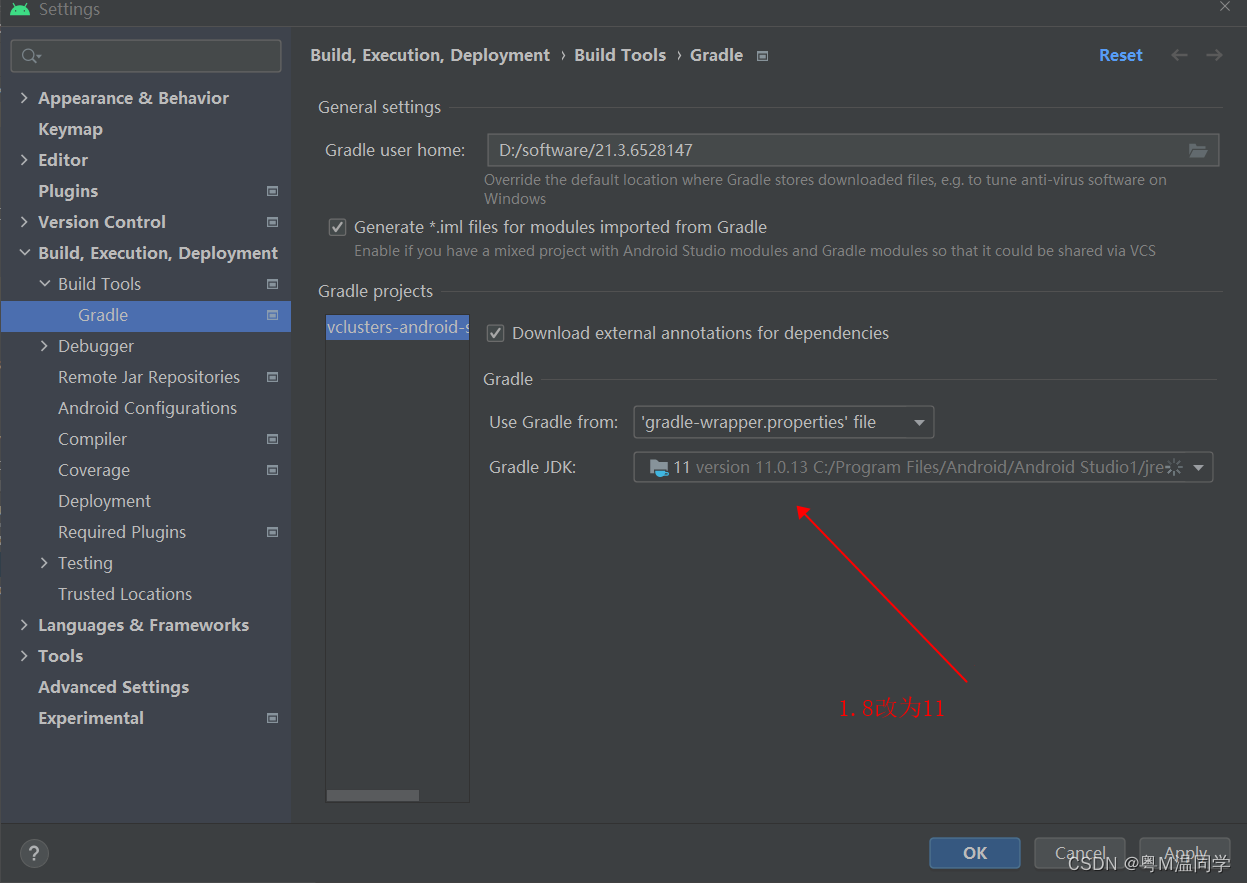

QPLL VCO在两个不同的频段内工作。下表描述了这些Band的标称工作范围。

当选择低频段VCO时,高频段VCO会自动断电,反之亦然。7系列FPGA Transceiver向导根据应用要求选择适当的频段和QPLL设置。

下面两个公式分别决定了QPLL的输出频率GHz以及transceiver线速率: