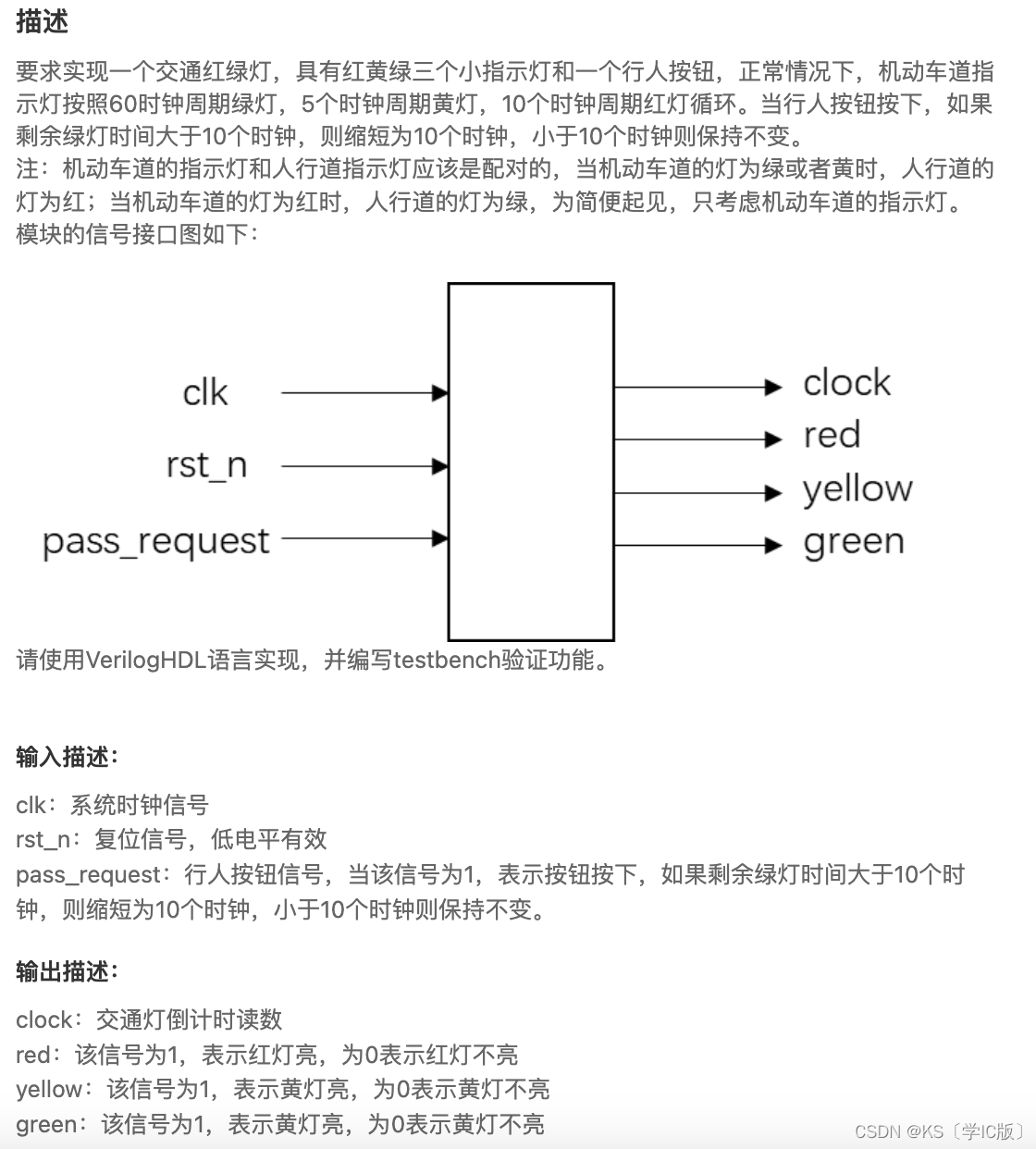

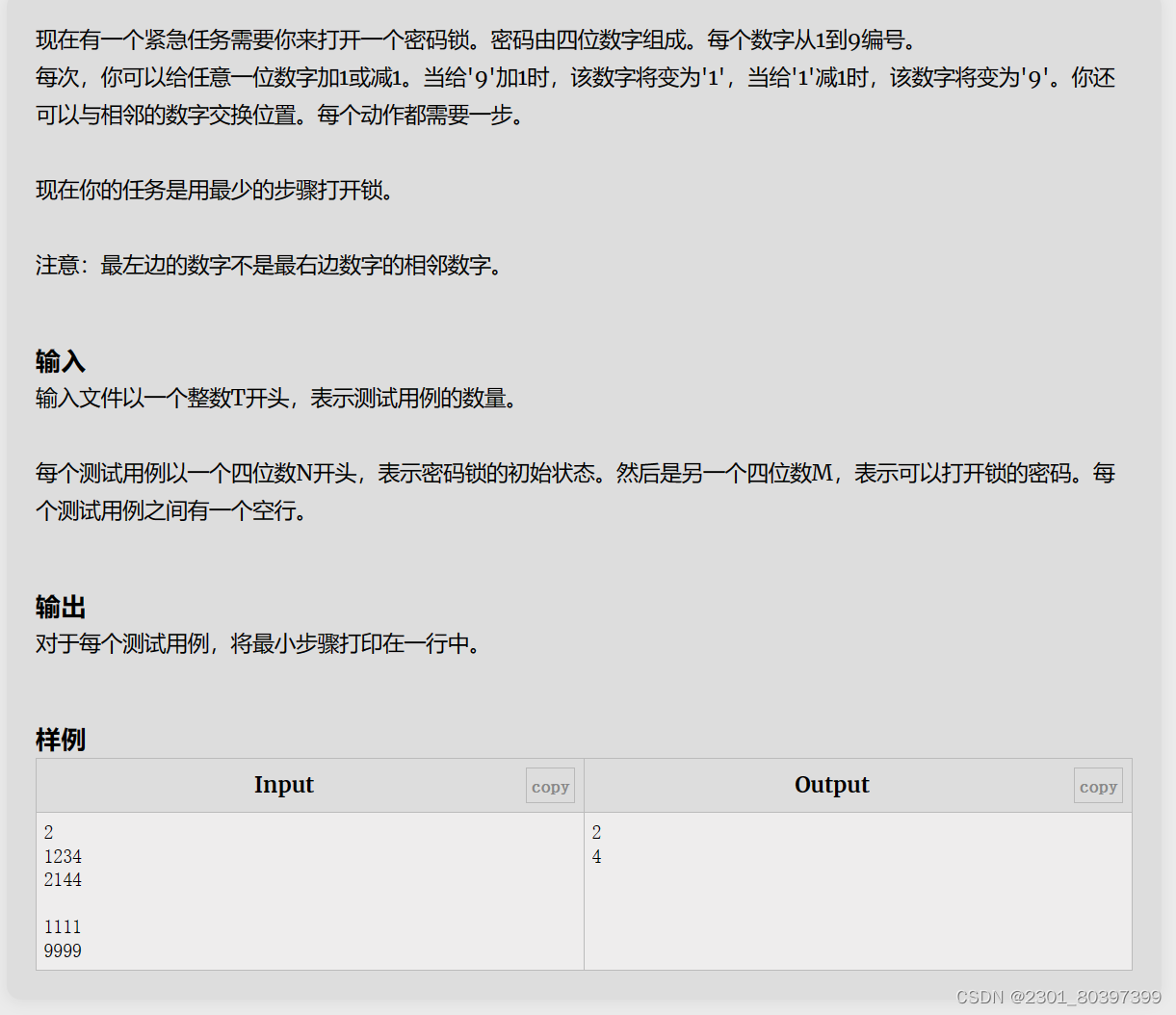

1、要求 : Modelsim 仿真软件

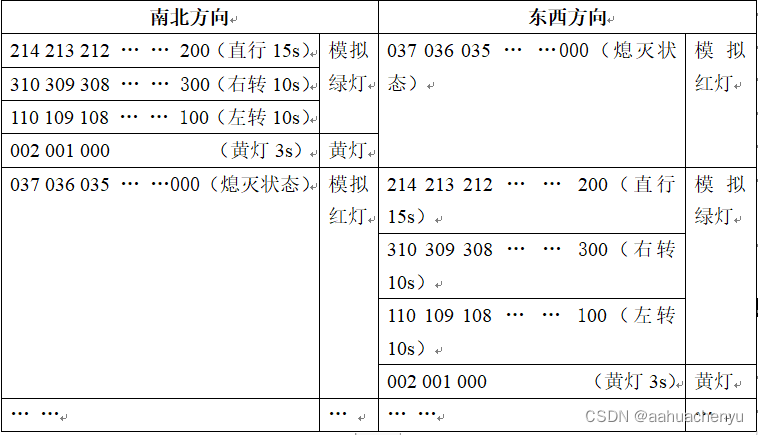

1)能依次显示显示十字路口东西方向和南北方向倒计时时间,单位为秒;显示路口↑↓← →四个方向指示灯状态(0/1/2/3 分别表示熄灭/左转/前行/右转);

2)为便于模拟观察,统一按如下顺序操作:先前行 15s,之后右转 10s,再左转 10s,接着 倒计时 3s(相当于黄灯),最后熄灭方向指示灯,切换到另一方向;

3)通过拨动开关 切换日常/凌晨模式;日常模式按 2)执行;凌晨模式用于模拟 00 点~ 04 点时间段路口暂停交通灯控制,倒计时器显示 0;

4)设置 S3/S0 键选择调整位置;S4/S1 键进行±调整,在合法值域内变动;设置 S2为调 整确认键,一旦确认,则保存调整后的倒计时时间。

2、要求分析

3、功能实现

module top(

input I_clk_1 ,

input I_rst ,

input I_k0 ,

input I_s3 ,

input I_s0 ,

input I_s2 ,

input I_s4 ,

input I_s1 ,

output [5:0] O_data_count_a ,

output reg [1:0] O_data_state_a = 'd0 ,

output [5:0] O_data_count_b ,

output reg [1:0] O_data_state_b = 'd0

);

parameter IDLE = 4'b0000;//IDLE

parameter S0 = 4'b0001;//S0?

parameter S1 = 4'b0010;//S1

parameter S2 = 4'b0011;//S2

parameter S3 = 4'b0100;//S3

parameter S4 = 4'b0101;//S0

parameter S5 = 4'b0110;//S1

parameter S6 = 4'b0111;//S2

parameter S7 = 4'b1000;//S3

//------------------------------------

reg [3:0] S_count;

always @(posedge I_clk_1)begin

if(I_rst)begin

S_count <= 'd0;

end else if(I_s4)begin

S_count <= S_count + 'd1;

end else if(S_count > 'd0 && I_s1)begin

S_count <= S_count - 'd1;

end else begin

S_count <=S_count;

end

end

//-----------------------------

reg [3:0] S_c_state = 'd0;

reg [3:0] S_n_state = 'd0;

reg [5:0] S_cnt_A = 'd0;

reg [5:0] S_cnt_B = 'd0;

//StateMachine:First_para

always @(posedge I_clk_1)begin

if(I_rst)begin

S_c_state <= IDLE;

end else begin

S_c_state <= S_n_state;

end

end

//StateMachine:Second_para

always @(*)begin

case(S_c_state)

IDLE : begin

if(I_rst || I_k0)begin

S_n_state = IDLE;

end else begin

S_n_state = S0;

end

end

S0 : begin

if(S_cnt_A == 6'd0)begin

S_n_state = S1;

end else if(I_k0)begin

S_n_state = IDLE;

end else if(I_s3)begin

S_n_state = S1;

end else if(I_s0)begin

S_n_state = IDLE;

end else begin

S_n_state = S0;

end

end

S1 : begin

if(S_cnt_A == 6'd0)begin

S_n_state = S2;

end else if(I_k0)begin

S_n_state = IDLE;

end else if(I_s3)begin

S_n_state = S2;

end else if(I_s0)begin

S_n_state = S0;

end else begin

S_n_state = S1;

end

end

S2 : begin

if(S_cnt_A == 6'd0)begin

S_n_state = S3;

end else if(I_k0)begin

S_n_state = IDLE;

end else if(I_s3)begin

S_n_state = S3;

end else if(I_s0)begin

S_n_state = S1;

end else begin

S_n_state = S2;

end

end

S3 : begin

if(S_cnt_A == 6'd0)begin

S_n_state = S4;

end else if(I_k0)begin

S_n_state = IDLE;

end else if(I_s3)begin

S_n_state = S4;

end else if(I_s0)begin

S_n_state = S2;

end else begin

S_n_state = S3;

end

end

S4 : begin

if(S_cnt_B == 6'd0)begin

S_n_state = S5;

end else if(I_k0)begin

S_n_state = IDLE;

end else if(I_s3)begin

S_n_state = S5;

end else if(I_s0)begin

S_n_state = S3;

end else begin

S_n_state = S4;

end

end

S5 : begin

if(S_cnt_B == 6'd0)begin

S_n_state = S6;

end else if(I_k0)begin

S_n_state = IDLE;

end else if(I_s3)begin

S_n_state = S6;

end else if(I_s0)begin

S_n_state = S4;

end else begin

S_n_state = S5;

end

end

S6 : begin

if(S_cnt_B == 6'd0)begin

S_n_state = S7;

end else if(I_k0)begin

S_n_state = IDLE;

end else if(I_s3)begin

S_n_state = S7;

end else if(I_s0)begin

S_n_state = S5;

end else begin

S_n_state = S6;

end

end

S7 : begin

if(S_cnt_B == 6'd0)begin

S_n_state = S0;

end else if(I_k0)begin

S_n_state = IDLE;

end else if(I_s3)begin

S_n_state = S0;

end else if(I_s0)begin

S_n_state = S6;

end else begin

S_n_state = S7;

end

end

default:S_n_state = IDLE;

endcase

end

//StateMachine:Third_para

//----------------------

reg S_i_s2_buf;

always @(posedge I_clk_1)begin

if(I_rst||(S_c_state == S7) && (S_n_state == S0))begin

S_i_s2_buf <= 'd0;

end else if(I_s2)begin

S_i_s2_buf <= 'd1;

end else begin

S_i_s2_buf <= S_i_s2_buf;

end

end

//---------------------------

integer i_9 = 'd9 ,i_2 = 'd2,i_14 = 'd14,i_37 = 'd37;

always @(posedge I_clk_1)begin

if(S_i_s2_buf && (S_c_state == S7) && (S_n_state == S0))begin

i_9 <= i_9 + S_count;

i_2 <= i_2 + S_count;

i_14 <= i_14 + S_count;

i_37 <= i_37 + S_count+ S_count+ S_count+ S_count;

end

end

always@(posedge I_clk_1) begin

if(I_rst||S_n_state == IDLE)begin

S_cnt_A <= 6'd0;

S_cnt_B <= 6'd0;

end else if((S_c_state == IDLE)&&(S_n_state == S0)) begin

S_cnt_A <= i_14;

S_cnt_B <= i_37;

end else if((S_c_state == S0) && (S_n_state == S1)) begin

S_cnt_A <= i_9;

S_cnt_B <= S_cnt_B - 'd1;

end else if((S_c_state == S1) && (S_n_state == S2)) begin

S_cnt_A <= i_9;

S_cnt_B <= S_cnt_B - 'd1;

end else if((S_c_state == S2) && (S_n_state == S3)) begin

S_cnt_A <= i_2;

S_cnt_B <= S_cnt_B - 'd1;

end else if((S_c_state == S3) && (S_n_state == S4)) begin

S_cnt_B <= i_14 ;

S_cnt_A <= i_37;

end else if((S_c_state == S4) && (S_n_state == S5)) begin

S_cnt_B <= i_9;

S_cnt_A <= S_cnt_A - 'd1;

end else if((S_c_state == S5) && (S_n_state == S6)) begin

S_cnt_B <= i_9;

S_cnt_A <= S_cnt_A - 'd1;

end else if((S_c_state == S6) && (S_n_state == S7)) begin

S_cnt_B <= i_2;

S_cnt_A <= S_cnt_A - 'd1;

end else if((S_c_state == S7) && (S_n_state == S0)) begin

if(S_i_s2_buf)begin

S_cnt_A <= i_14+S_count;

S_cnt_B <= i_37+S_count+S_count+S_count+S_count;

end else begin

S_cnt_A <= i_14;

S_cnt_B <= i_37;

end

end else begin

S_cnt_A <= S_cnt_A - 'd1;

S_cnt_B <= S_cnt_B - 'd1;

end

end

//-----------------------

always@(posedge I_clk_1) begin

if(S_n_state == IDLE) begin

O_data_state_a <= 'd0;

O_data_state_b <= 'd0;

end else if(S_n_state == S0) begin

O_data_state_a <= 'd2;

O_data_state_b <= 'd0;

end else if(S_n_state == S1) begin

O_data_state_a <= 'd3;

O_data_state_b <= 'd0;

end else if(S_n_state == S2) begin

O_data_state_a <= 'd1;

O_data_state_b <= 'd0;

end else if(S_n_state == S3) begin

O_data_state_a <= 'd0;

O_data_state_b <= 'd0;

end else if(S_n_state == S4) begin

O_data_state_a <= 'd0;

O_data_state_b <= 'd2;

end else if(S_n_state == S5) begin

O_data_state_a <= 'd0;

O_data_state_b <= 'd3;

end else if(S_n_state == S6) begin

O_data_state_a <= 'd0;

O_data_state_b <= 'd1;

end else if(S_n_state == S7) begin

O_data_state_a <= 'd0;

O_data_state_b <= 'd0;

end else begin

O_data_state_a <= O_data_state_a;

O_data_state_b <= O_data_state_b;

end

end

assign O_data_count_a = S_cnt_A;

assign O_data_count_b = S_cnt_B;

endmodule

4、测试文件

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2023/03/13 13:29:41

// Design Name:

// Module Name: tb

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module tb( );

reg I_clk;

reg I_rst;

reg I_k0;

reg I_s0;

reg I_s1;

reg I_s2;

reg I_s3;

reg I_s4;

wire [5:0] O_data_count_a ;

wire [1:0] O_data_state_a;

wire [5:0] O_data_count_b ;

wire [1:0] O_data_state_b ;

initial begin

I_clk <= 'd0;

I_rst <= 'd1;

I_k0 <= 'd0;

I_s0 <= 'd0;

I_s1 <= 'd0;

I_s2 <= 'd0;

I_s3 <= 'd0;

I_s4 <= 'd0;

#1005

I_rst <= 'd0;

#2000

I_k0 <= 'd1;

#5000

I_k0 <= 'd0;

#3050

I_s3 <= 'd1; #10 I_s3 <= 'd0;

#3050

I_s3 <= 'd1; #10 I_s3 <= 'd0;

#3000

I_s4 <= 'd1; #10 I_s4 <= 'd0;

#1000

I_s2 <= 'd1; #10 I_s2 <= 'd0;

#3000

I_s4 <= 'd1; #10 I_s4 <= 'd0;

end

always #5 I_clk = ~I_clk;

top u_state(

.I_clk_1 (I_clk ),

.I_rst (I_rst ),

.I_k0 (I_k0 ),

.I_s3 (I_s3 ),

.I_s0 (I_s0 ),

.I_s2 (I_s2 ),

.I_s4 (I_s4 ),

.I_s1 (I_s1 ),

.O_data_count_a(O_data_count_a),

.O_data_state_a(O_data_state_a),

.O_data_count_b(O_data_count_b),

.O_data_state_b(O_data_state_b)

);

endmodule