1.集成12位DAC和ADC的一款器件,2个输入模拟通道和2个输出模拟通道

2.• TX频段:47 MHz至6.0 GHz • RX频段:70 MHz至6.0 GHz

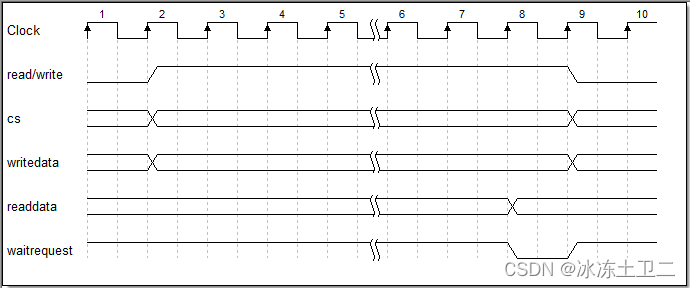

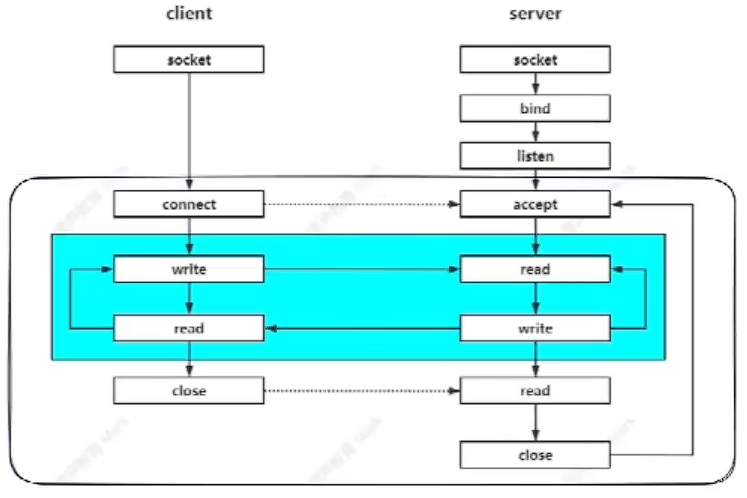

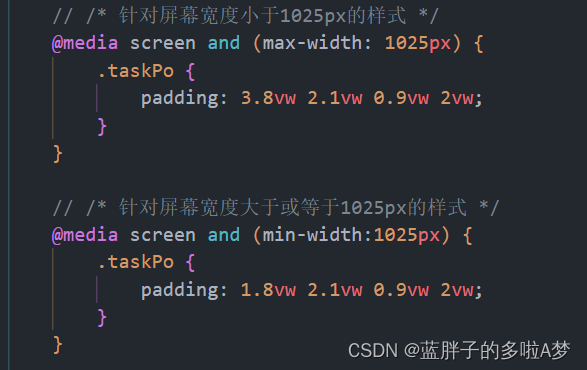

3.SPI配置成LVDS或CMOS接口,也可以还可以选择FDD(频分双工——全双工,操作时需要两个独立的信道)或TDD(时分双工——半双工,只需要一个信道)工作方式

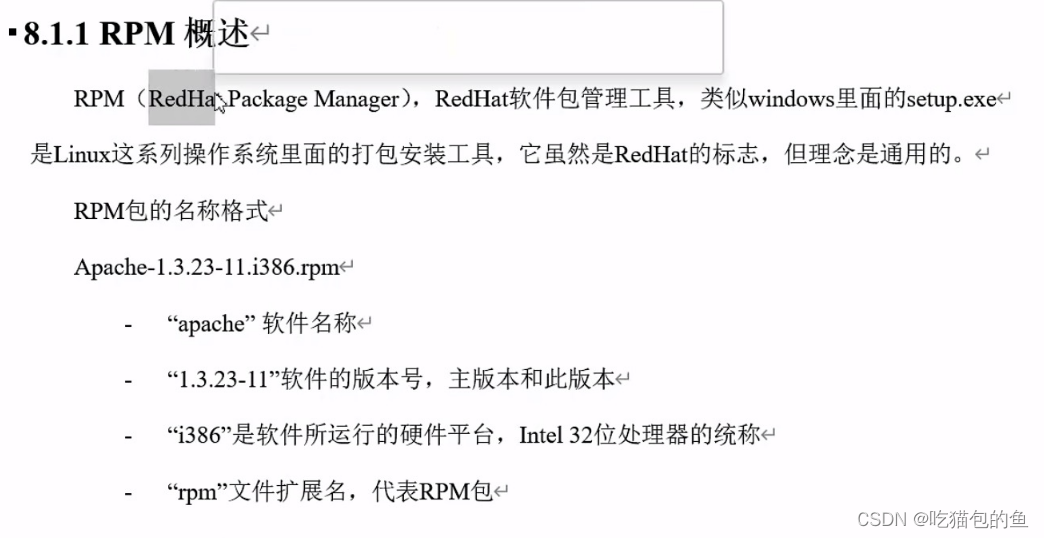

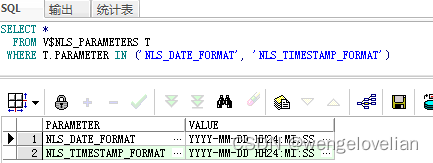

4.由于9361的寄存器较多,首先利用AD936X Evaluation Software 软件(安装包在百度网盘里面),根据我们的项目需求,配置相应的功能参数,生成寄存器参数配置文件。详细配置流程AD936x Evaluation Software 详细配置_ad936x软件时钟配置界面-CSDN博客

5.好像也有官方代码