LabVIEW 以数据流方式执行代码。 当节点的所有输入上都存在数据时,该节点就会执行。 当节点完成执行时,节点的输出将数据传递到下游的下一个节点。 LabVIEW FPGA 使用三个组件来维护这种数据流范例。

节点具有与其功能相对应的逻辑

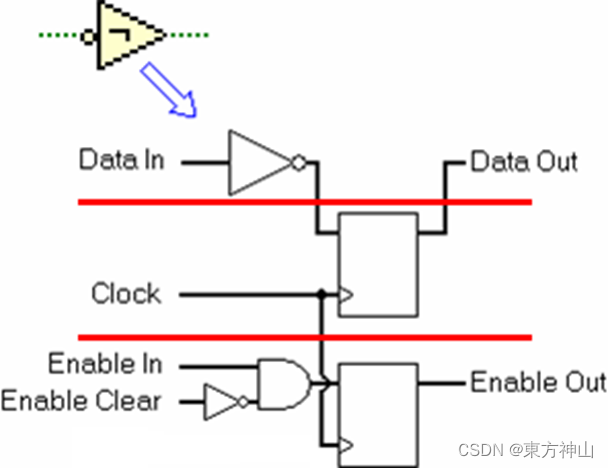

同步,该组件记录函数的输出,以便将逻辑与时序不确定性隔离

启用链,附加逻辑通过验证输入和输出来协调数据流

启用链

启用链是LabVIEW添加至FPGA代码的附加逻辑,用于强制执行FPGA的数据流。启用链包含两个部分:

- 与程序框图上的实际数据流并行运行的一组寄存器。启用链的此部分仅位于单周期定时循环的外部。

- 强制执行单周期定时循环内部数据流的隐式启用信号该信号扇出包含状态保持元素的循环内部的全部节点。

数据流编程概述

数据流编程模型与用 C 等语言实现的控制流模型形成对比。

由于自上而下的顺序编程方法,用 C 编写的应用程序在映射到并行硬件时具有固有的局限性。相反,在数据流模型中,框图上的节点相互连接以表达逻辑执行流,并且可以使用它们轻松地表达并行性。当框图节点接收到所有必需的输入时,它会生成输出数据并将该数据传递到数据流路径中的下一个节点。数据通过节点的移动决定了框图上功能的执行顺序。

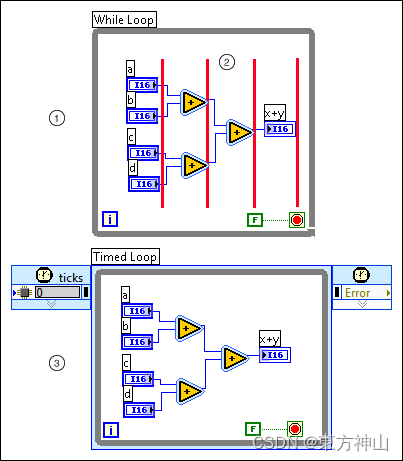

LabVIEW数据流编程范例允许LabVIEW执行系统在不同线程中运行两个循环。在许多基于文本的编程语言中,您必须显式创建和处理线程。

L abVIEW 还提供特殊结构,将代码映射到并行硬件资源以实现显式线程。例如,一种这样的结构是定时循环。当定时循环中包含的代码在双核或多核系统上运行时,将创建一个唯一的线程。下图演示了两个定时循环如何创建两个独特的线程,这两个线程可以在多核系统的两个独立核心之间进行平衡。

对于 FPGA,不存在线程概念,因此循环结构在 FPGA 结构上保留空间并作为独特的处理器内核执行。

总之,由于数据流编程语言本质上是并行的,因此开发人员可以创建隐式并行的应用程序。编程语言的这一特性意味着开发人员无需成为多核处理器和 FPGA 等并行硬件的低级复杂性方面的专家即可获得性能优势 - 语言本身有助于代码的并行化。

FPGA内的数据流

LabVIEW以数据流的方式执行代码。当所有输入都有数据时,节点才会执行。当节点完成执行时,节点的输出将数据传递给下游的下一个节点。

单周期定时循环外的数据流

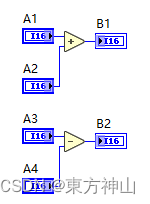

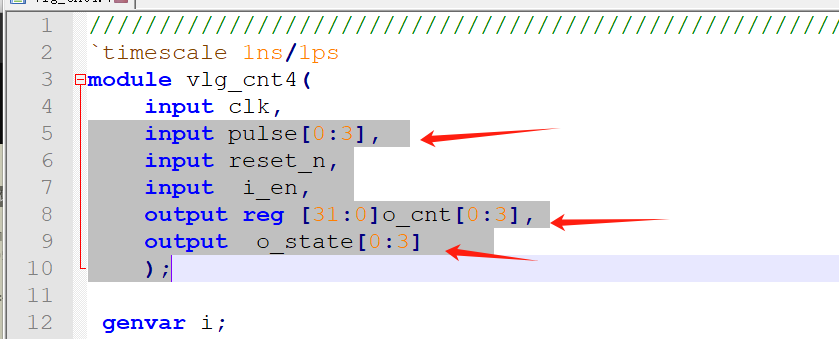

LabVIEW以数据流的方式执行代码。当数据在节点运行所需的全部输入端就绪时,节点开始执行。节点执行结束后,节点输出传送数据至下一节点。下列示意图显示了一个要在单周期定时循环外部实现布尔函数的FPGA硬件的范例。

启用链确保FPGA逻辑按照其在LabVIEW程序框图中的顺序执行。示意图显示了函数位于单周期定时循环外部时,布尔函数转换为FPGA逻辑的过程。下列示意图的函数部分显示了程序框图上相对于“取负数”函数的布尔逻辑。启用链部分包含额外的同步寄存器,仅在时钟的上升沿输出数据。

下列示意图给出了一个执行算法操作的FPGA硬件的范例。

根据启用链的系统开销,每个函数或VI至少占用一个时钟周期。某些函数(例如,模拟输入运算)将占用几百个时钟周期。具体取决于运算的复杂程度及硬件限制。

单周期定时循环内的数据流

放置在单周期定时循环内部的节点不包含启用链的寄存器部分。如排除启用链的系统开销,FPGA的整体空间使用量将有所下降。因为不再需要用于启用链的触发器。同样由于不再存在启用链,单周期定时循环内的所有运算均可在一个时钟周期内完成。但某些节点(例如,存储器方法节点或FFT Express VI)需要大于一个时钟周期的执行时间,因此该节点的输出要等待至单周期定时循环的下一次迭代时才有效。获取有效数据所需的时钟周期数量为节点的延时。

隐式启用信号对定时性能的影响

单周期定时循环内的隐式启用信号扇出程序框图内的全部触发器。LabVIEW将门控与单周期定时循环相关的时钟,直至隐式启用信号被移除。该扇出的额外连线系统开销将限制大型设计的定时性能。如设计包含独立于程序框图上其他节点运行的单周期定时循环,请考虑从上述循环中移除隐式启用信号以改善定时性能。

注:移除隐式启用信号的支持随终端变化。关于移除隐式启用信号支持的详细信息,见终端硬件文档。

下文描述了一个包含单周期定时循环代码的程序框图。

下列示意图为上述程序框图代码的VHDL表示。

注意,默认情况下,隐式启用信号扇出包含状态保持元素(例如,触发器或存储器块)的单周期定时循环的每个节点。该连线的系统开销限制了某些应用的定时性能。

下列示意图为移除了隐式启用信号的同一VHDL表达。

![[深度学习] 计算机视觉低代码工具Supervision库使用指北](https://img-blog.csdnimg.cn/img_convert/c189480de366e1fafc60edcbe21aff0c.jpeg)

![练习8 Web [GYCTF2020]Blacklist](https://img-blog.csdnimg.cn/direct/9bc22046a3134ace84938261661af191.png)