该系列为神经网络硬件加速器应用中涉及的模块接口部分,随手记录,以免时间久了遗忘。

一 背景

我们知道,在FPGA做神经网络应用加速时,涉及到权重参数的存储和加载。通常在推理过程中,会将权重参数存储在外部DDR或片上SRAM上。但是对于一些大的网络模型,往往片上RAM受限而无法完全保存权重,因此需要将权重放置在外部DDR或者PSRAM等外部存储器中,等具体需要的时候,从片外load进片上,然后计算完丢弃,重新load下一批次权重。

这里就涉及到,当我们的应用固化后,片外DDR存储器权重加载问题,通常包括集中方法,一是上电后,通过PCIE/UART/SD卡等load进DDR;另一种方法是将权重和FPGA bit文件一并打包存储在FLASH中,上电后,从FLASH中加载至片外DDR,或者直接load进片上SRAM。

为了简化设计,这里采用第二种方法,将FPGA位流和权重等用户数据打包存入Flash配置芯片中。

二 方案设计

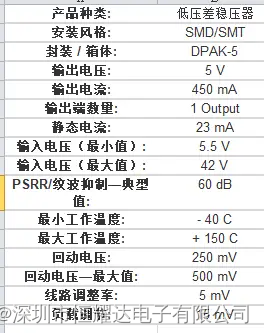

FPGA:XC7A50T

配置芯片:MX25L6433F Flash

为了简化设计,这里采用第二种方法,将FPGA位流和权重等用户数据打包存入Flash配置芯片中。

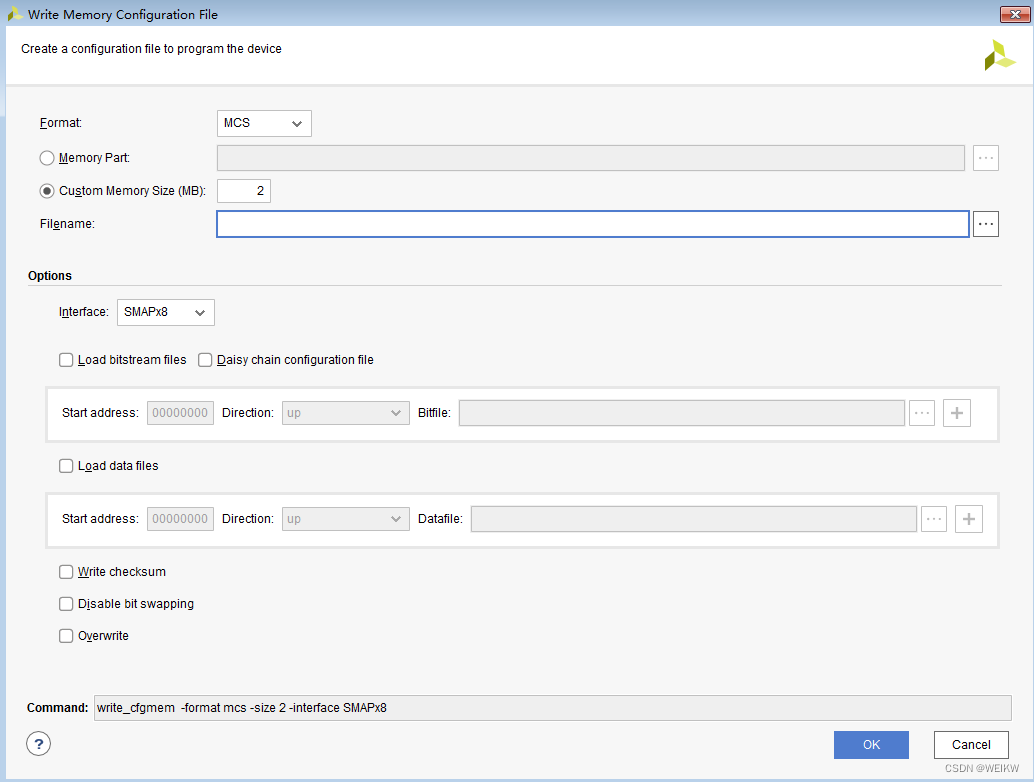

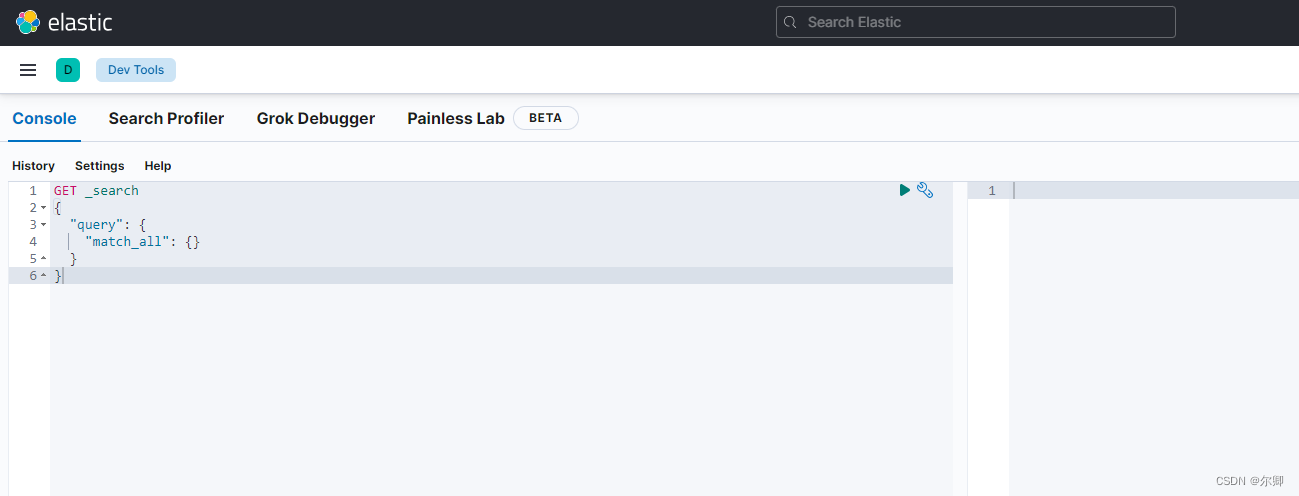

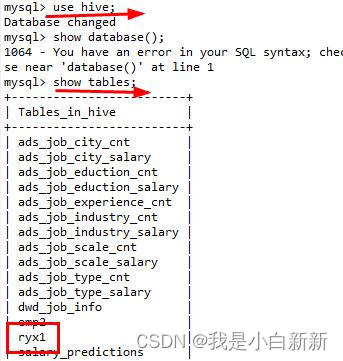

简单讲就是通过VIVADO的工具,将用户数据和FPGA bit进行打包生成mcs,同时注意需要将用户数据存储在程序空间之外。上电后,通过SPI_Loader将Flash中的用户数据,加载至外部DDR即可。

架构分析:

架构分析:

SPI接口部分,没有什么新意,和常规读写FLASH一样,用户接口为了方便,直接采用AXI协议进行控制,方便与标准总线互通。

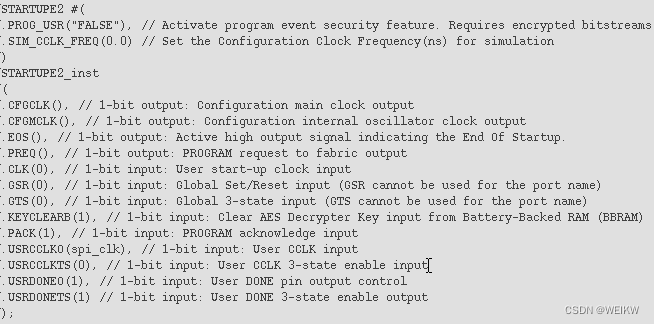

另外,由于涉及对FLASH读控制操作,需要配置FLASH管脚,需要调用STARTUPE2原语,用于对CCLK进行设置,用于该时钟。

调用方法:

调用方法:

![[ C++ ] STL---string类的模拟实现](https://img-blog.csdnimg.cn/direct/0dfe7a3b382f46008e190481fa4f7d68.png)