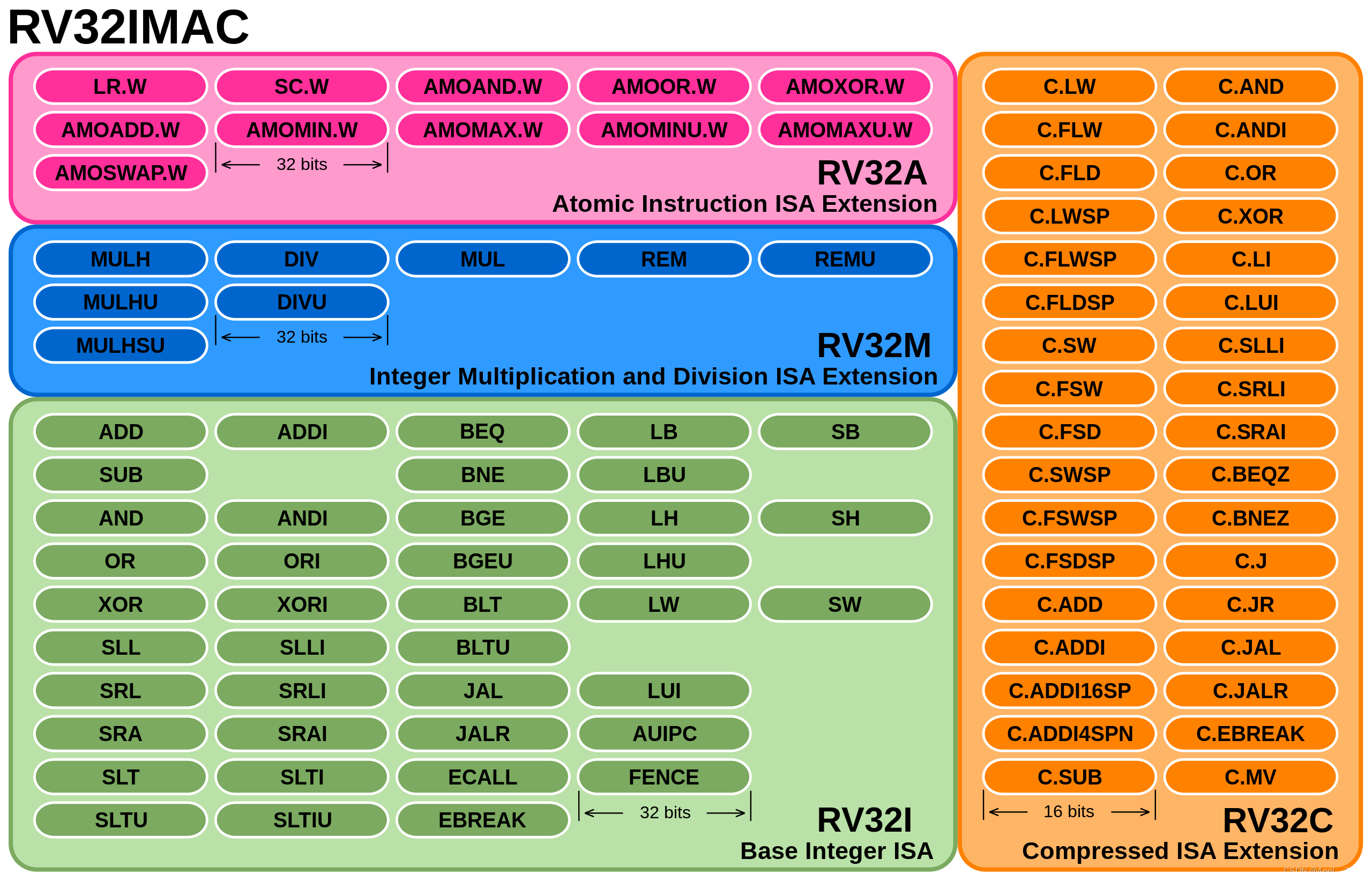

RISCV架构 ACLINT文档

ACLINT原文档:https://github.com/riscv/riscv-aclint/blob/main/riscv-aclint.adoc

在这里进行了翻译以及校对,仅供参考,不正确的地方欢迎指出

1、介绍

【此 RISC-V ACLINT 规范定义了一组内存映射设备,这些设备为多 HART RISC-V 平台上的每个 HART 提供处理器间中断 (IPI) 和定时器功能】。 在多 HART RISC-V 平台上运行的操作系统、引导加载程序和固件需要这些 HART 级 IPI 和定时器功能。

SiFive 核心本地中断器 (CLINT) 器件已在 RISC-V 领域广泛采用,以提供机器级 IPI 和定时器功能。 不幸的是,【SiFive CLINT 具有针对 IPI 和定时器功能的统一寄存器映射,并且不提供 supervisor-level IPI 功能】。

【RISC-V ACLINT 规范采用更加模块化的方法,为 IPI 和定时器功能定义单独的内存映射设备】。 当平台具有替代机制时,这种模块化允许 RISC-V 平台省略一些 RISC-V ACLINT 设备。 除了模块化之外,【RISC-V ACLINT 规范还为 Supervisor 级 IPI 定义了专用内存映射设备】。 下面的表 1 显示了 RISC-V ACLINT 规范定义的器件列表。

Table 1. ACLINT 设备

| 名称 | 特权级 | 功能 |

|---|---|---|

| MTIMER | Machine | 固定频率计数器和定时器事件 |

| MSWI | Machine | 处理器间(或软件)中断 |

| SSWI | Supervisor | 处理器间(或软件)中断 |

RISC-V ACLINT 规范被定义为向后兼容 SiFive CLINT 规范。 MTIMER 和 MSWI 器件的寄存器定义和寄存器偏移量与 SiFive CLINT 规范定义的定时器和 IPI 寄存器兼容。 RISC-V 平台上的 SiFive CLINT 设备在逻辑上可以看作是在内存地址空间中彼此相邻放置的一个 MSWI 设备和一个 MTIMER 设备,如下表 2 所示。

1.1、与 SiFive CLINT 向后兼容

RISC-V ACLINT 规范与 SiFive CLINT 规范向后兼容。**【MTIMER 和 MSWI 器件的寄存器定义和寄存器偏移量与 SiFive CLINT 规范定义的定时器和 IPI 寄存器兼容】。**在 RISC-V 平台上,一个 SiFive CLINT 器件在逻辑上可视为一个 MSWI 器件和一个 MTIMER 器件,它们在内存地址空间中相邻放置,如下表 2 所示。

Table 2. 一个 SiFive CLINT 设备相当于两个 ACLINT 设备

| SiFive CLINT 偏移范围 | ACLINT 设备 | 功能 |

|---|---|---|

| 0x0000_0000 - 0x0000_3fff | MSWI | 机器级处理器间(或软件)中断 |

| 0x0000_4000 - 0x0000_bfff | MTIMER | 机器级固定频率计数器和定时器事件 |

2、机器级定时器设备(MTIMER)

【MTIMER 器件为 RISC-V 平台上的一组 HART 提供机器级定时器功能。它有一个固定频率单调时间计数器 (MTIME) 寄存器,并且对于连接到 MTIMER 设备的每个 HART 都有一个时间比较寄存器 (MTIMECMP)。 未连接到任何 HART 的 MTIMER 设备应仅具有 MTIME 寄存器,而没有 MTIMECMP 寄存器】。

在具有多个 MTIMER 设备的 RISC-V 平台上:

- 每个 MTIMER 设备为不同(或不相交)的 HART 集提供机器级定时器功能。 MTIMER 设备为与其关联的每个 HART 分配一个从零开始的 HART 索引。 MTIMER 设备分配给 HART 的 HART 索引可能与 RISC-V 特权架构分配给 HART 的唯一 HART 标识符(hart ID)有任何关系,也可能没有关系

- 两个或多个 MTIMER 设备可以共享相同的物理 MTIME 寄存器,同时拥有自己单独的 MTIMECMP 寄存器

- MTIMER 设备的 MTIMECMP 寄存器必须仅与同一 MTIMER 设备的 MTIME 寄存器进行比较,以生成机器级定时器中断

单个 MTIMER 设备支持的最大 HART 数量为 4095,相当于 MTIMECMP 寄存器的最大数量。

2.1、寄存器映射

一个 MTIMER 设备有两个独立的基地址:一个用于 MTIME 寄存器,另一个用于 MTIMECMP 寄存器。 单个 MTIMER 设备的单独的基地址允许多个 MTIMER 设备共享相同的物理 MTIME 寄存器。

下面的表 3 显示了 MTIME 寄存器的映射,而下面的表 4 显示了 MTIMECMP 寄存器相对于单独基地址的映射。

Table 3. ACLINT MTIMER Time 寄存器映射

| Offset | Width | Attr | Name | Description |

|---|---|---|---|---|

| 0x0000_0000 | 8B | RW | MTIME | Machine-level time counter |

Table 4. ACLINT MTIMER Compare 寄存器映射

| Offset | Width | Attr | Name | Description |

|---|---|---|---|---|

| 0x0000_0000 | 8B | RW | MTIMECMP0 | HART index 0 machine-level time compare |

| 0x0000_0008 | 8B | RW | MTIMECMP1 | HART index 1 machine-level time compare |

| … | … | … | … | … |

| 0x0000_7FF0 | 8B | RW | MTIMECMP4094 | HART index 4094 machine-level time compare |

2.2、MTIME 寄存器 (Offset: 0x00000000)

MTIME 寄存器是一个 64 位读写寄存器,包含基于固定参考频率计数的周期数。

MTIMER 器件复位时,MTIME 寄存器被清零。

2.3、MTIMECMP 寄存器 (Offsets: 0x00000000 - 0x00007FF0)

MTIMECMP 寄存器是每个 HART 一个的 64 位读写寄存器。它包含相应的 HART 触发机器级定时器中断的 MTIME 寄存器的值。

**每当 MTIME 大于或等于相应 MTIMECMP 寄存器中的值时,HART 的机器级定时器中断就会挂起,而每当 MTIME 小于相应 MTIMECMP 寄存器中的值时,HART 的机器级定时器中断就会被清除。**机器级定时器中断反映在 mip CSR 的 MTIP 位中。

在 MTIMER 器件复位时,MTIMECMP 寄存器处于未知状态。

2.4、同步多个 MTIME 寄存器

RISC-V 平台可以将多个 HART 分组为分层拓扑组(例如 clusters、nodes 或 sockets),其中每个拓扑组都有自己的 MTIMER 设备。 此外,此类 RISC-V 平台还允许在运行时对拓扑组(包括 MTIMER 设备)进行时钟门控或断电。

2.4 节省略了部分内容,这一部分可以查阅资料

暂时未涉及到多个 MTIMER 设备的情况

3、机器级软件中断设备(MSWI)

【MSWI 设备为 RISC-V 平台上的一组 HART 提供机器级 IPI 功能。 它为连接到 MSWI 设备的每个 HART 提供一个 IPI 寄存器 (MSIP)】。

在具有多个 MSWI 设备的 RISC-V 平台上,每个 MSWI 设备为不同(或不相交)的 HART 集提供机器级 IPI 功能。 MSWI 设备为与其关联的每个 HART 分配一个从零开始的 HART 索引。 MSWI 设备分配给 HART 的 HART 索引可能与 RISC-V 特权架构分配给 HART 的唯一 HART 标识符 (hart ID) 有任何关系,也可能没有关系。

单个 MSWI 设备支持的 HART 最大数量为 4095,相当于 MSIP 寄存器的最大数量。

3.1、寄存器映射

Table 5. ACLINT MSWI 设备寄存器映射

| Offset | Width | Attr | Name | Description |

|---|---|---|---|---|

| 0x0000_0000 | 4B | RW | MSIP0 | HART index 0 machine-level IPI register |

| 0x0000_0004 | 4B | RW | MSIP1 | HART index 1 machine-level IPI register |

| … | … | … | … | … |

| 0x0000_3FFC | 4B | RESERVED | Reserved for future use. |

3.2、MSIP Registers (Offsets: 0x00000000 - 0x00003FF8)

每个 MSIP 寄存器都是一个 32 位宽的 WARL 寄存器,其中高 31 位连接为零。 最低有效位反映在 mip CSR 的 MSIP 中。【通过向相应的 MSIP 寄存器写入 1 或 0 可以挂起或清除 HART 的机器级软件中断】。

在 MSWI 设备复位时,每个 MSIP 寄存器都被清零。

4、Supervisor-level Software Interrupt Device (SSWI)

【SSWI 设备为 RISC-V 平台上的一组 HART 提供 Supervisor 级 IPI 功能。它提供一个寄存器来为连接到 SSWI 设备的每个 HART 设置 IPI (SETSSIP)】。

在具有多个 SSWI 设备的 RISC-V 平台上,每个 SSWI 设备为不同(或不相交)的 HART 集提供 Supervisor 级 IPI 功能。 SSWI 设备为与其关联的每个 HART 分配一个从零开始的 HART 索引。 SSWI 设备分配给 HART 的 HART 索引可能与 RISC-V 特权架构分配给 HART 的唯一 HART 标识符 (hart ID) 有任何关系,也可能没有关系。

单个 SSWI 设备支持的最大 HART 数量为 4095,相当于 SETSSIP 寄存器的最大数量。

4.1、Register Map

Table 6. ACLINT SSWI Device 寄存器映射

| Offset | Width | Attr | Name | Description |

|---|---|---|---|---|

| 0x0000_0000 | 4B | RW | SETSSIP0 | HART index 0 set supervisor-level IPI register |

| 0x0000_0004 | 4B | RW | SETSSIP1 | HART index 1 set supervisor-level IPI register |

| … | … | … | … | … |

| 0x0000_3FFC | 4B | RESERVED | Reserved for future use. |

4.2、SETSSIP Registers (Offsets: 0x00000000 - 0x00003FF8)

每个 SETSSIP 寄存器都是一个 32 位宽的 WARL 寄存器,其中高 31 位连接为零。 SETSSIP 寄存器的最低有效位始终读取 0。**将 0 写入 SETSSIP 寄存器的最低有效位没有任何效果,而将 1 写入最低有效位会向相应的 HART 发送边沿敏感中断信号,导致 HART 置位 mip CSR 中的 SSIP。**对 SETSSIP 寄存器的写入保证反映在相应 HART 的 SSIP 中,但不一定立即反映。

注意:RISC-V 特权架构将 mip 和 sip CSR 中的 SSIP 定义为可写位,因此 M 模式或 S 模式软件可以直接清除 SSIP。