1,同步复位与异步复位

简单来说:复位信号与时钟同步,称之为同步复位。

复位信号与时钟不同步,称之为异步复位。

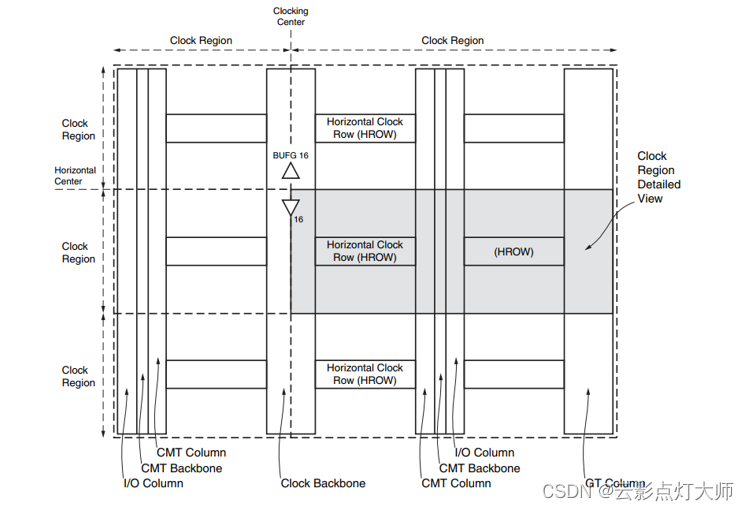

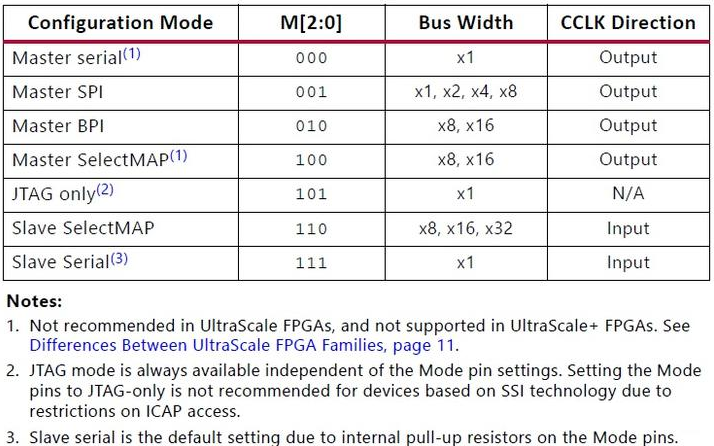

2、xilinx 的复位策略

① 同步高复位

② 计数器和状态机必须复位

③ 能不使用复位尽量不使用复位,比如中间打拍的信号。因为过多的复位会增加扇出(一个复位信号驱动了过多的信号,这种情况下就称为扇出过大),引起时序不稳定。

3、实际工程复位的写法

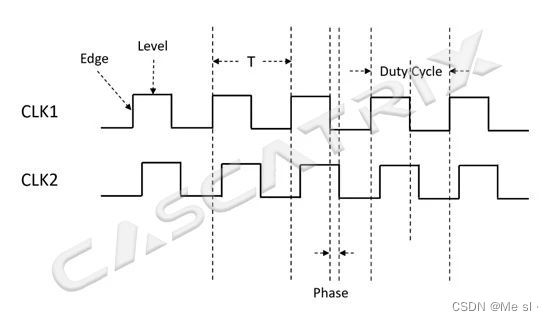

实际项目工程一般有几万行甚至几十万行的代码,工程里面有多个时钟域, 这种情况怎么处理时钟和复位的问题呢?一般单独弄一个时钟复位模块来管理不同的时钟和复位信号。

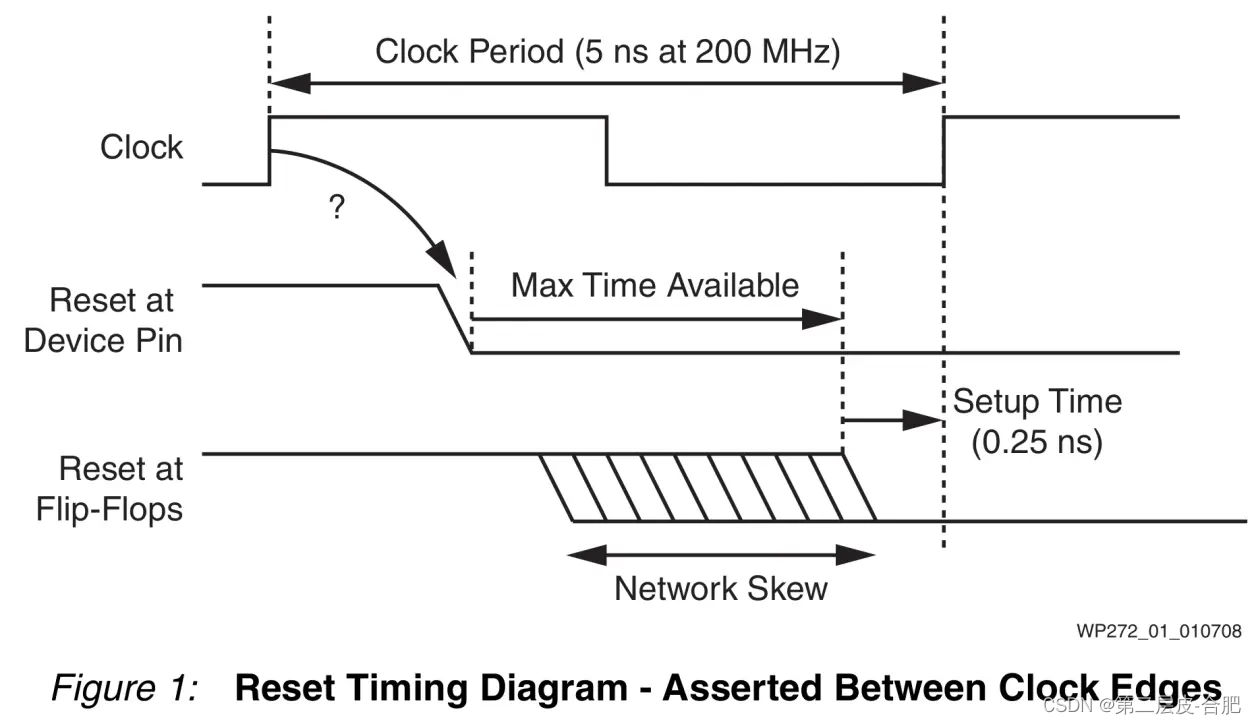

4、同步复位致命的缺点

虽然 xilinx 推荐同步复位,不过同步复位有个致命的缺点,没有控制好,非常容易引起时序问题

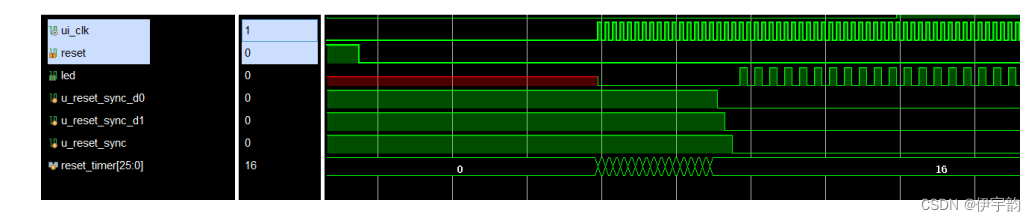

ui_clk在开始时是不稳定的,但是复位信号在不稳定的时候已经结束了,右面这个代码就进不去复位信号为为高时,LED为0。这是,这种复位是有问题的,这时LED为不定态。这是需要怎么做呢就是需要把reset信号展宽,展宽到ui_clk稳定时,复位一段时间,再拉低。

5、多时钟域下的同步复位设计(非常容易引起时序问题)

多时钟域下,如果使用同步复位,一定要注意复位信号的设计,比如读写 DDR3 的时候,有个 ui_clk 和用户 clk,一定要注意 DDR3 模块的复位信号设计。

reset 信号不能作为 ui_clk 的复位信号,即使打两拍也不行,因为 reset 复位 时间比较短,在 ui_clk 还没有稳定就复位结束了。

常见的做法就是将 reset 信号展宽后进行打拍。时序图和代码如下:

always @(posedge ui_clk or posedge reset) begin

if (reset) begin

reset_timer <= 'do;

end

else if (reset_timer <= 4'hf) begin

reset_timer <= reset_timer + 1'b1;

end

else

beginreset_timer <= reset_timer;

end

end

always @(posedge ui_clk or posedge reset) begin

if (reset) begin

u_reset_sync_do <= 1'b1;

u_reset_sync_d1 <= 1'b1;

ui_clk_reset_sync <= 1'b1;

end

else begin

u_reset_sync_do <= reset_timer <= 4'hf;

u_reset_sync_d1 <= u_reset_sync_do;

u_reset_sync <= u_reset_sync_di;

end

end

always @(posedge ui_clk) begin

if (u_reset_sync) begin

led <= 1'b0;

end

else begin

led <= led;

end

end