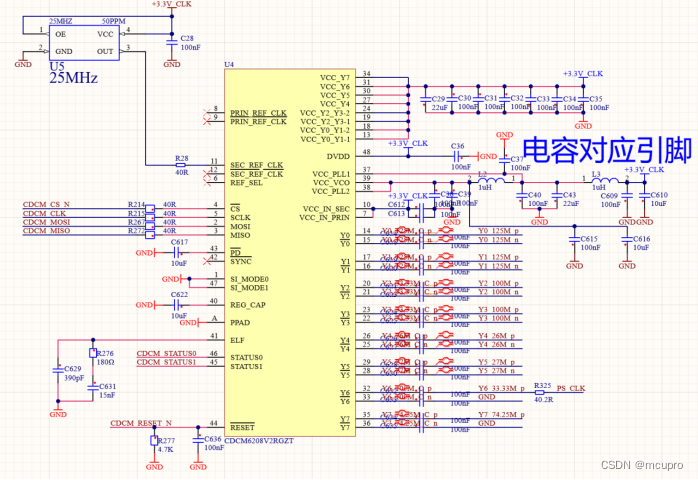

时钟资源

采用时钟芯片CDCM6208提供系统时钟

PL端时钟

PS 收发器时钟

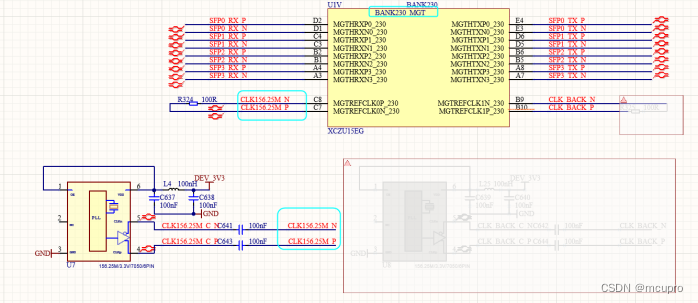

PL收发器时钟

电源

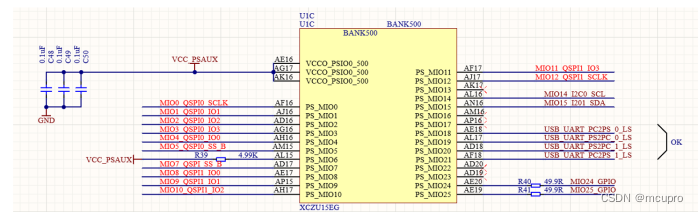

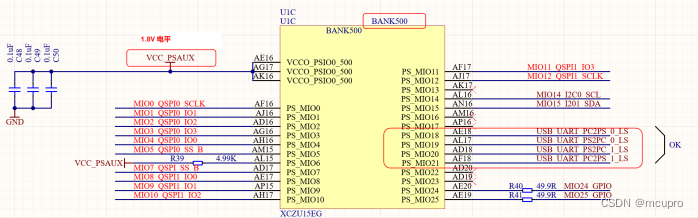

BANK500 |

BANK501 |

BANK502 |

BANK503(专用) |

|

1.8V |

1.8V |

1.8V |

1.8V |

PS端外设

QSPI

采用2片MT25QU256 拼接成8bit的QSPI存储系统。采用1.8V供电

SD卡

SATA接口

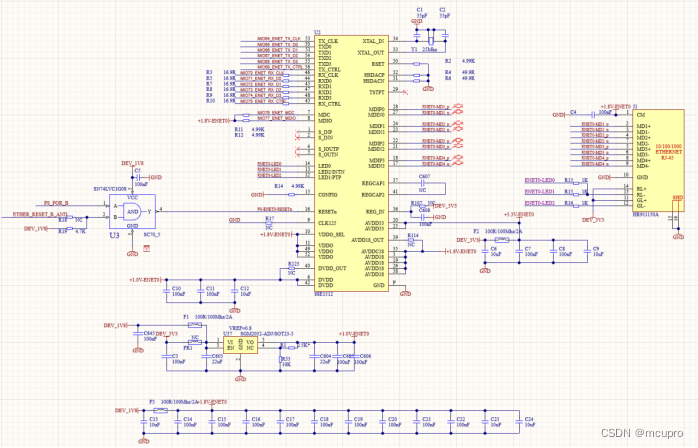

PS端以太网接口

DP接口

USB外设

采用USB3220芯片

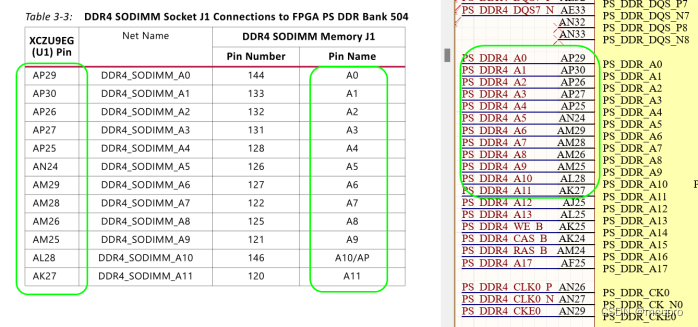

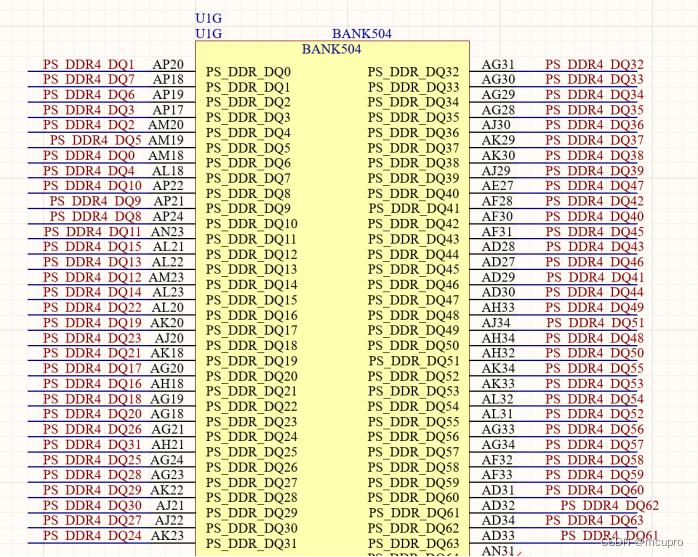

DDR4资源

T15EG开发板采用4片DDR4构成64位的存储系统,具体型号如下

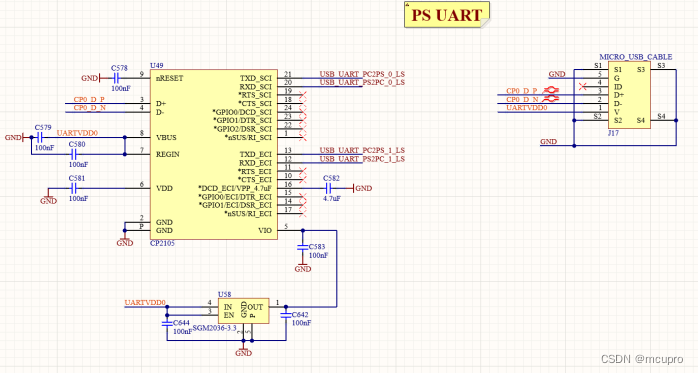

串口

EMMC

PL端资源

QSFP光口

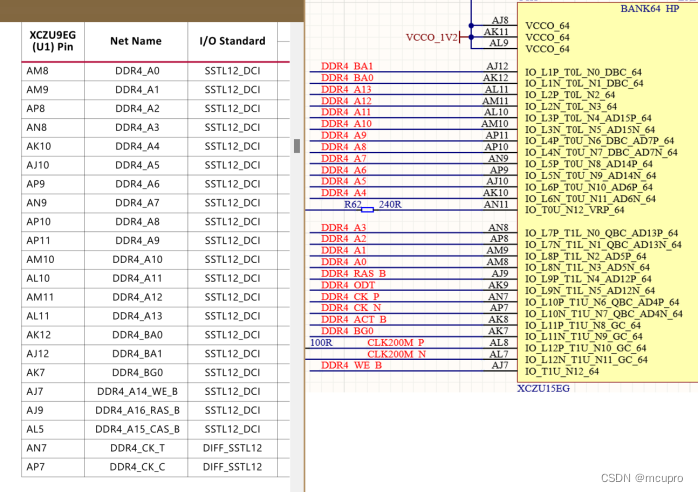

DDR4

PL端挂载单片16位的DDR4颗粒

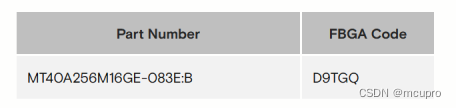

ZCU102原厂开发板的DDR4的具体型号

唯一的区别:本开发板采用标准的2400速度等级的内存颗粒;

拨码开关

拨码开关 |

FPGA管脚 |

电平标准 |

SW0 |

AM13 |

LVCMOS1V8 |

SW1 |

AN12 |

LVCMOS1V8 |

SW2 |

AP12 |

LVCMOS1V8 |

SW3 |

AL13 |

LVCMOS1V8 |

LED灯

PL端:4个

PS端:2个

LED |

FPGA管脚 |

电平标准 |

LD0 |

AN13 |

LVCMOS1V8 |

LD1 |

AM14 |

LVCMOS1V8 |

LD2 |

AP14 |

LVCMOS1V8 |

LD3 |

AN14 |

LVCMOS1V8 |

LD4 |

MIO25 |

|

LD5 |

MIO24 |

按键

PL端按键2个

PS端按键2个

按键 |

FPGA管脚 |

电平标准 |

K0 |

AK15 |

LVCMOS1V8 |

K1 |

AK14 |

LVCMOS1V8 |

K2 |

MIO39 |

|

K3 |

MIO38 |

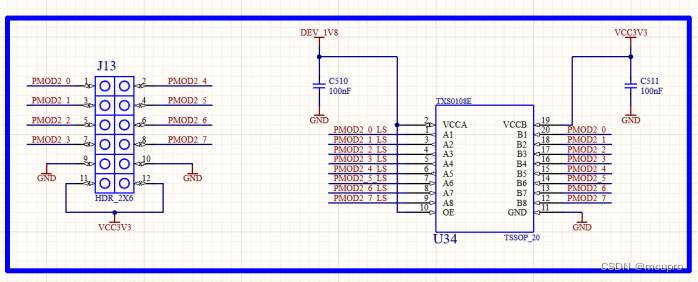

PMOD

PMOD所在的bank 1.8V供电,外部采样3.3V电平转换芯片

串口

PL端实验例程

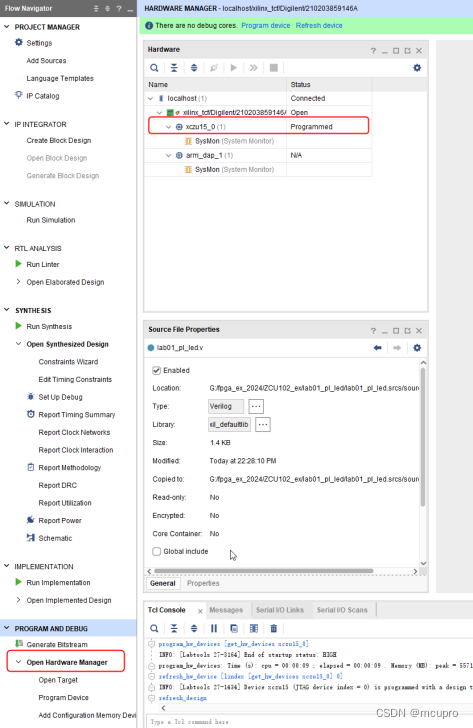

PL端的LED实验

选择芯片型号 : XCZU15EG-FFVB1156-2-i

默认选择都OK

编写“led.v” ,这里定义了一个 32 位的寄存器 timer, 用于循环计数 0~199999999(1 秒钟),

计数到 199999999(1 秒)的时候, 寄存器 timer 变为 0,并翻转1个 LED。这样原来 LED 是

灭的话,就会点亮,如果原来 LED 为亮的话,就会熄灭。 由于输入时钟为 200MHz 的差分

时钟,因此需要添加 IBUFDS 原语连接差分信号, 编写好后的代码如下:

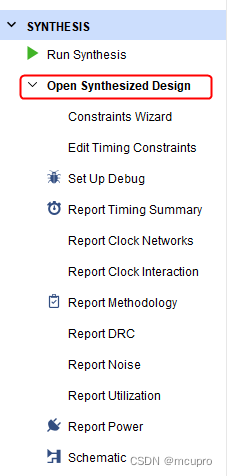

开始综合设计,综合完成后打开”Open Synthesized Design”

,然后切换到I/O Planning编辑状态, 进行IO管脚的分配

然后可以进行实现设计,产生位流bit文件了

输入时钟是PL端的200M差分时钟; 电平是1.8V的, PL端有2个按键,我们使用 K0来作为复位输入,高电平复位;

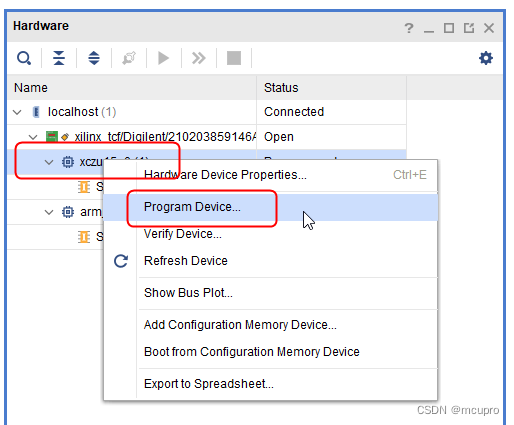

等待完成, 打开下载界面.

因为器件 为ZCU15EG, 为了下载速度更快,我们用最快的时钟频率

下载完成后,可以看见led等 LD0 , 开始每秒闪烁一次

PL端的PLL实验

很多初学者看到板上只有一个 200Mhz 时钟输入的时候都产生疑惑,时钟怎么是 200Mhz?

如果要工作在 100Mhz、 150Mhz 怎么办? 其实在很多 FPGA 芯片内部都集成了 PLL,其他厂商

可能不叫 PLL,但是也有类似的功能模块,通过 PLL 可以倍频分频,产生其他很多时钟。本实验

通过调用 PLL IP core 来学习 PLL 的使用、 vivado 的 IP core 使用方法。

实验原理

PLL(phase-locked loop),即锁相环。是 FPGA 中的重要资源。由于一个复杂的 FPGA 系统往往需要多个不同频率,相位的时钟信号。所以,一个 FPGA 芯片中 PLL 的数量是衡量 FPGA 芯片能力的重要指标。 FPGA 的设计中,时钟系统的 FPGA 高速的设计极其重要, 一个低抖动, 低延迟的系统时钟会增加 FPGA 设计的成功率。

本实验将通过使用 PLL, 输出一个方波到开发板上的扩展口,来给大家演示在 Vivado 软件里使用 PLL 的方法。

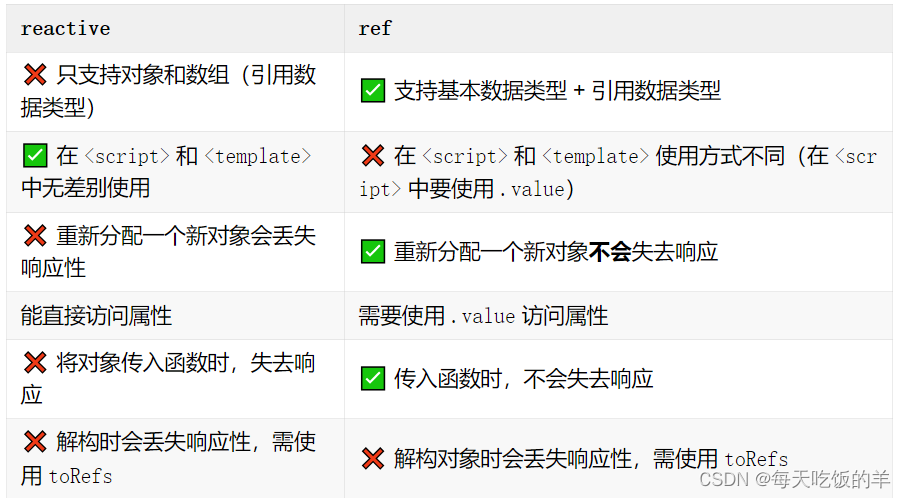

Ultrascale+系列的 FPGA 使用了专用的全局(Global)和区域(Regional)IO 和时钟资源来管理设计中各种的时钟需求。 Clock Management Tiles(CMT)提供了时钟合成(Clock frequency synthesis),倾斜矫正(deskew),过滤抖动(jitter filtering)功能。每个 CMTs 包含一个 MMCM(mixed-mode clock manager)和一个 PLL。 如下图所示, CMT 的输入可以是 BUFR, IBUFG, BUFG, GT, BUFH,本地布线(不推荐使用),输出需要接到 BUFG 或者

BUFH 后再使用。

混合模式时钟管理器(MMCM)

MMCM 用于在与给定输入时钟有设定的相位和频率关系的情况下,生成不同的时钟信号。 MMCM 提供了广泛而强大的时钟管理功能,

MMCM 内部的功能框图如下图所示:

数字锁相环(PLL)

锁相环(PLL)主要用于频率综合。使用一个 PLL 可以从一个输入时钟信号生成多个时钟信号。 与 MMCM 相比,不能进行时钟的 deskew,不具备高级相位调整,倍频器和分频器可调范围较小等。

PLL 功能框图如下图所示

想了解更多的时钟资源, 建议大家看看 Xilinx 提供的文档"7 Series FPGAs ClockingResources User Guide"。

本实验中为大家演示如果调用 Xilinx 提供的 PLL IP 核来产生不同频率的时钟, 并把其中的一个时钟输出到 FPGA 外部 IO 上, 下面为程序设计的详细步骤。

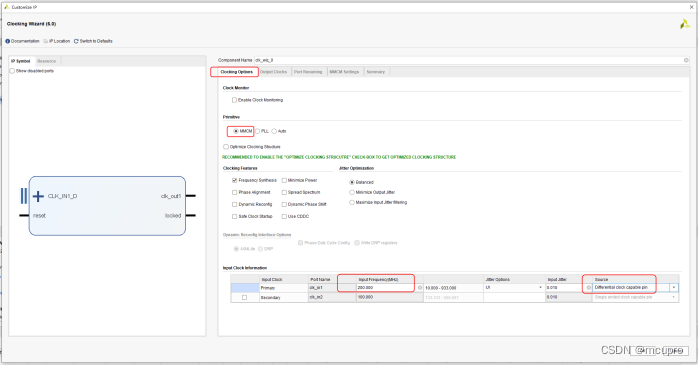

1) 新建一个 lab02_pl_pll 的工程,点击 Project Manager 界面下的 IP Catalog。

按照LED实验的方法新建一个工程,然后添加IP核

默认这个 Clocking Wizard 的名字为 clk_wiz_0, 这里我们不做修改。在第一个界面 Clocking

Options 里,输入的时钟频率为 200Mhz,并选择 Differential clock capable pin,因为时钟输

入是差分的。

其他保持默认设置

在 Output Clocks 界面里选择 clk_out1~clk_out4 四个时钟的输出,频率分别为 200Mhz,

100Mhz, 50Mhz, 25Mhz。这里还可以设置时钟输出的相位,我们不做设置,保留默认相位,

点击 OK 完成,

![BUUCTF-Real-[Flask]SSTI](https://img-blog.csdnimg.cn/direct/5fb10bf0145f48f0b514881dfb04b04a.png)