接前一篇文章:《PCI Express体系结构导读》随记 —— 第I篇 第2章 PCI总线的桥与配置(25)

2.5 非透明PCI桥

本回将以Intel 21555为例说明非透明PCI桥。

2.5.1 Intel 21555中的配置寄存器

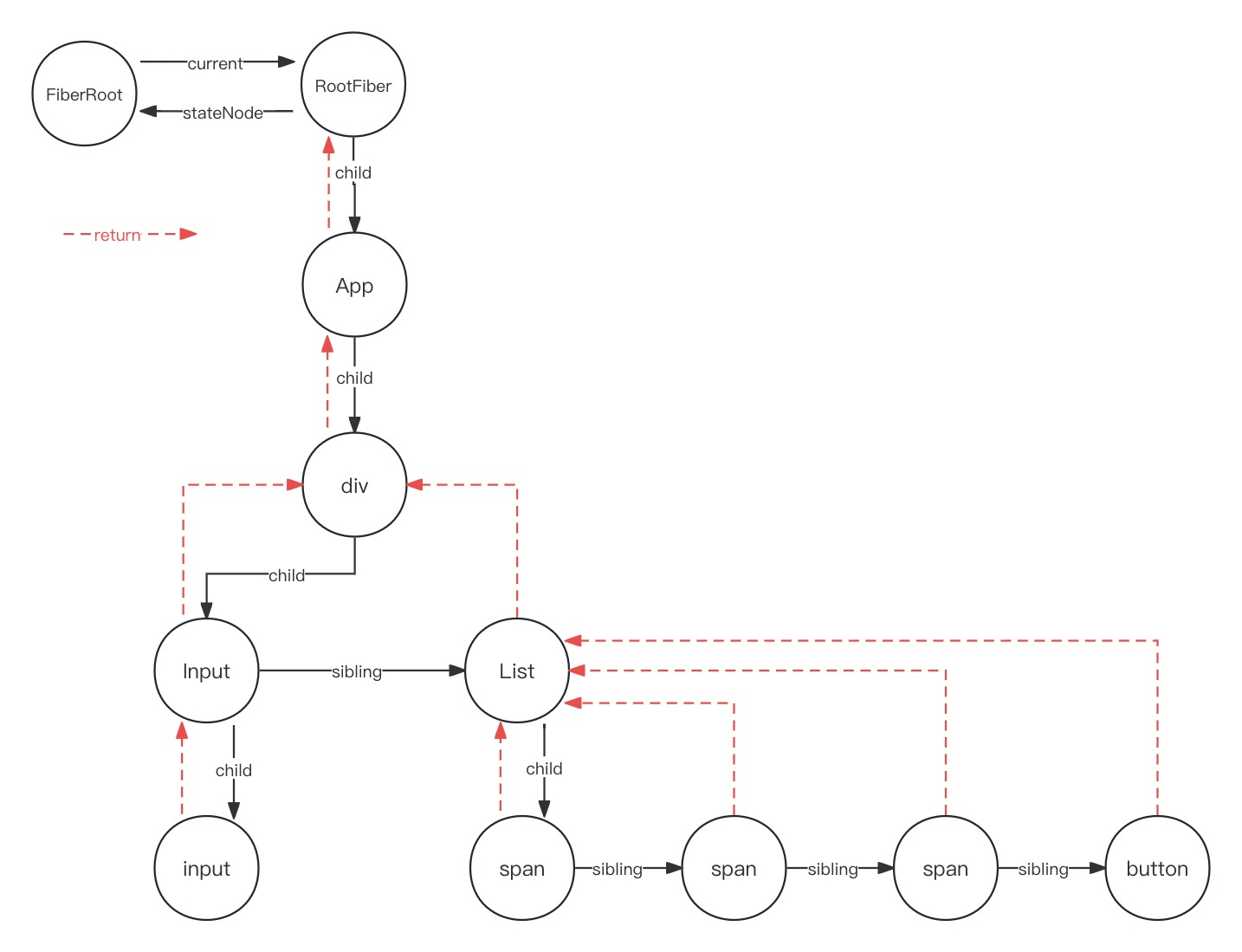

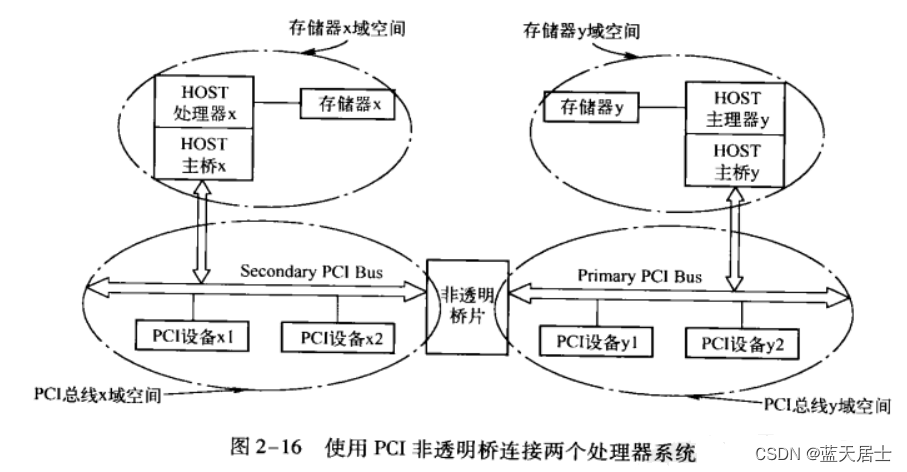

Intel 21555非透明PCI桥源于DEC21554(DEC21544是Digital公司的产品),并在此基础上做了一些改动。Intel 21555桥片与其它透明桥在系统中的位置相同。如图2-16所示,这个桥片一边与Primary PCI总线相连,另一边与Secondary PCI总线相连。

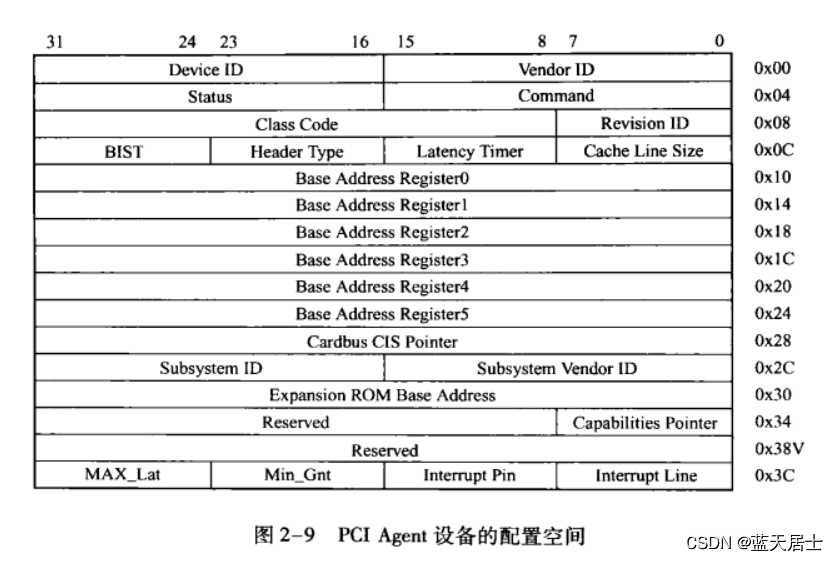

在Intel 21555桥片中,包含两个PCI 设备配置空间,分别是Primary PCI总线配置空间和Secondary PCI总线配置空间,处理器可以使用Type 00h配置请求访问这些配置空间。在大多数情况之下,在Primary PCI总线上的HOST处理器管理Primary PCI配置空间;在Secondary PCI总线上的HOST处理器管理Secondary PCI配置空间(Intel 21555非透明桥片两边的HOST处理器都可以访问Primary和Secondary总线的配置寄存器)。

在Intel 21555桥片中,还有一组私有寄存器CSR(Control and Status Register)。系统软件使用这组寄存器对非透明桥进行管理并获得桥片的一些信息,这组寄存器可以被映射成为PCI总线的存储器地址空间或者I/O地址空间。

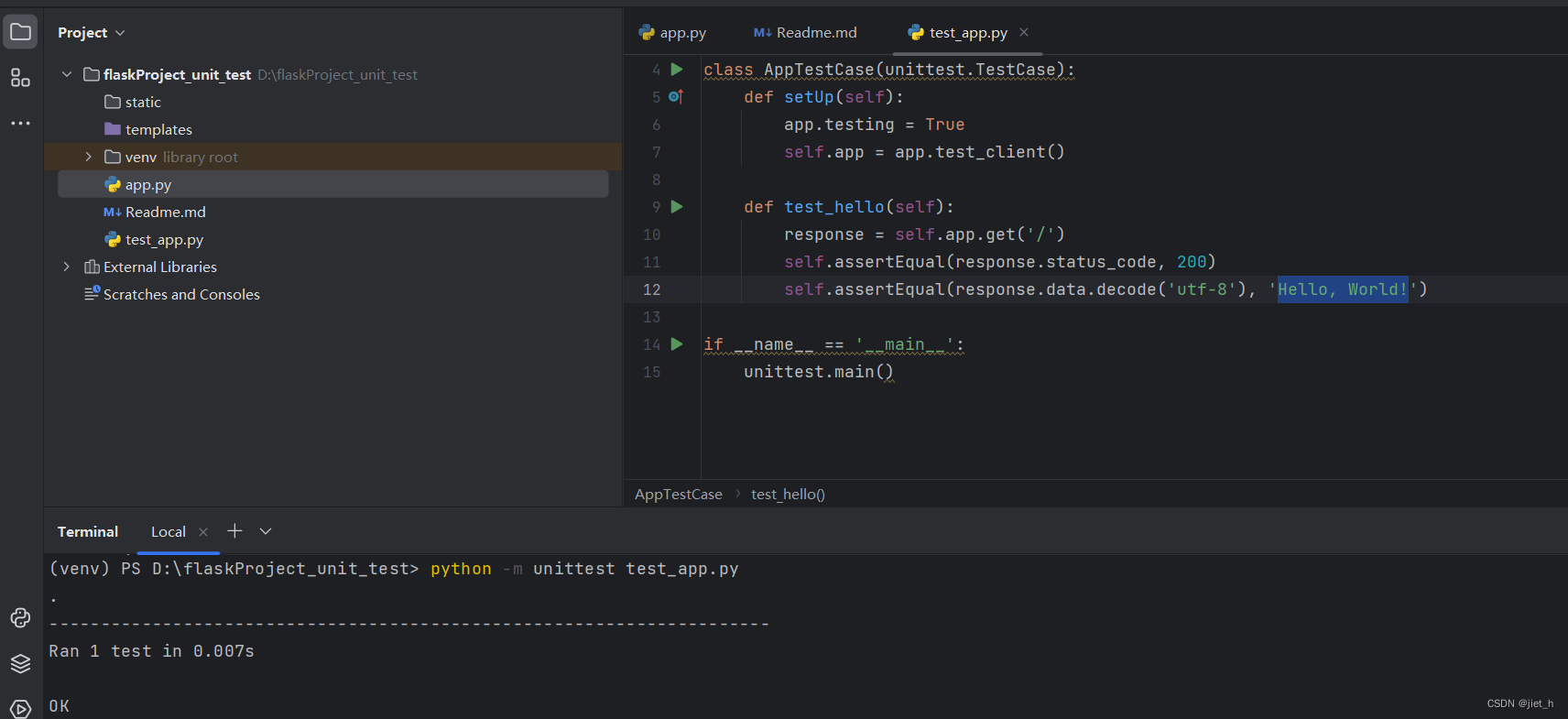

本章仅介绍Primary PCI总线这一边的配置寄存器,Secondary PCI总线的配置寄存器虽然与Primary PCI总线的这些寄存器略有不同,但是基本对等,因此本节对此不做介绍。Primary PCI总线的主要寄存器如表2-6所示:

表2-6 Primary PCI总线的配置寄存器

| Offset | 寄存器 | PCI配置寄存器 | 复位值 |

|---|---|---|---|

| 0x13 ~ 0x10 | Primary CSR and Memory 0 BAR | BAR0 | 0x00000000 |

| 0x17 ~ 0x14 | Primary CSR I/O BAR | BAR1 | 0x00000001 |

| 0x1B ~ 0x18 | Downstream Memory 1 BAR | BAR2 | 0x00000000 |

| 0x1F ~ 0x1C | Downstream Memory 2 BAR | BAR3 | 0x00000000 |

| 0x23 ~ 0x20 | Downstream Memory 3 BAR | BAR4 | 0x00000000 |

| 0x27 ~ 0x24 | Downstream Memory 3 BAR Upper 32 Bits | BAR5 | 0x00000000 |

| 0x97 ~ 0x94 | Downstream Memory 0 Translated Base | None | 不确定 |

| 0x9B ~ 0x98 | Downstream I/O or Memory 1 Translated Base | None | 不确定 |

| 0x9F ~ 0x9C | Downstream Memory 2 Translated Base | None | 不确定 |

| 0xA3 ~ 0xA0 | Downstream Memory 3 Translated Base | None | 不确定 |

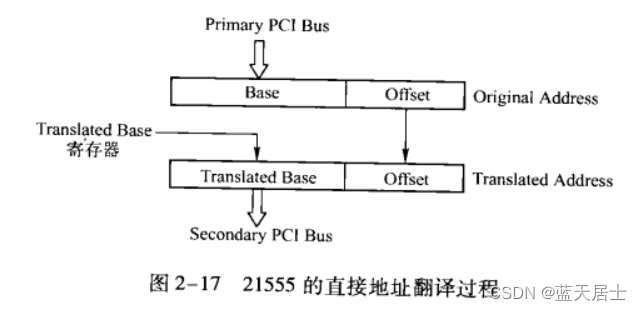

从表2-6中,我们可以发现Primary PCI总线的这些配置寄存器共分为两组:一组寄存器与PCI设备的配置寄存器的BAR0~5对应,这些寄存器与标准PCI配置寄存器BAR0~5的功能相同;另一组寄存器是Translated Base寄存器,这组寄存器的主要作用是将来自Primary PCI总线的数据访问转换到Secondary PCI总线。

其中,BAR0~5寄存器在系统初始化时由Primary PCI总线上的HOST处理器进行配置,配置过程与PCI总线上的普通设备完全相同。只是Intel 21555规定,BAR0只能映射为32位存储器空间。

CSR寄存器可以根据需要映射在BAR0空间中,此时BAR0空间最小为4KB;CSR寄存器也可以根据需要使用BAR1寄存器映射为I/O地址空间,同时BAR1寄存器还可以映射其它I/O空间;BAR2~3只能映射为32位存储器地址空间;而BAR4~5用来映射64位的存储器地址空间。

对于Primary PCI总线,所有BAR0~5寄存器映射的地址空间都将占用Primary PCI总线域,然而这些地址空间中所对应的数据并不在Primary PCI总线域中,而是在Secondary PCI总线域中。Translated Base寄存器实现不同PCI总线域地址空间的转换,Intel 21555将不同PCI总线域地址空间的转换过程称为“地址翻译”。

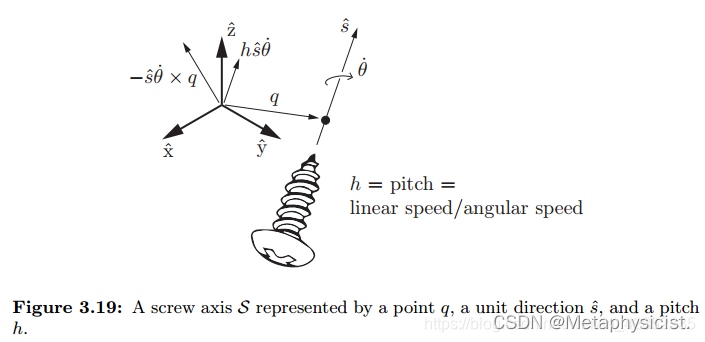

Intel 21555支持两种地址翻译方法:一个是直接地址翻译,一个是查表翻译。Primary PCI总线的BAR空间只支持直接地址翻译,而Secondary PCI总线的Memory 2 BAR空间支持查表翻译,本节仅介绍直接地址翻译方法,对查表翻译有兴趣的读者请阅读Intel 21555的数据手册。直接地址翻译过程如图2-17所示:

当Primary PCI总线对非透明桥21555的BAR0~5地址空间进行数据请求时,这个数据请求将被转换为对Secondary PCI总线的数据请求。Translated Base寄存器将完成这个地址翻译过程。

下一回将结合实例说明这个直接地址翻译过程。