系列文章

数值(整数,实数,字符串)与数据类型(wire、reg、mem、parameter)

运算符

数据流建模

行为级建模

结构化建模

组合电路的设计

组合电路的特点是,电路中任意时刻的稳态输出仅仅取决于该时刻的输入,而与电路原来的状态无关。组合电路没有记忆功能.

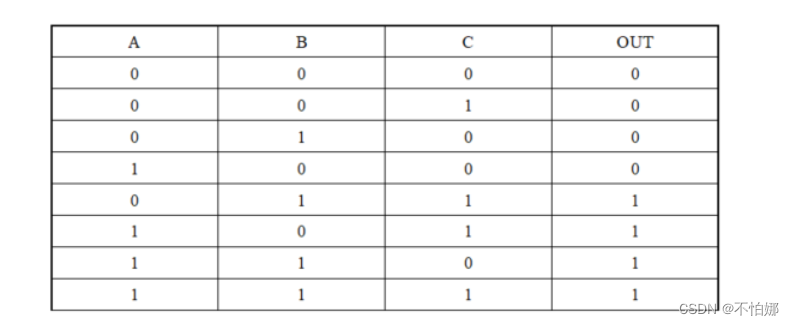

例4.2-1 设计一个3个裁判的表决电路,当两个或两个以上裁判同意时,判决器输出“1”,否则输出“0”。

真值表法:

真值表是对电路功能最直接和简单的描述方式。根据电路的功能,可以通过真值表直接建立起输出与输入之间的逻辑关系。

module design(A,B,C,OUT);

input A,B,C;

output reg OUT;

always @(A or B or C) // 或者@(*)

case({A,B,C})

3'b000 : OUT=0;

3'b001 : OUT=0;

3'b010 : OUT=0;

3'b100 : OUT=0;

3'b011 : OUT=1;

3'b101 : OUT=1;

3'b110 : OUT=1;

3'b111 : OUT=1;

endcase

endmodule

多路选择器的代码和上面类似:

//4选1多路选择器

module mux41_case(in0,in1,in2,in3,se,out);

input in0,in1,in2,in3;

input [1:0] se;

output reg out;

always @(*)

begin

case(se)

2'b00: out = in0;

2'b01: out = in1;

2'b10: out = in2;

default: out = in3;

endcase

end

endmodule

2输入1 bit信号全加器

assign {C_OUT,SUM}=A+B+C_IN;module one_bit_fulladder(A,B,C_IN,SUM,C_OUT);

input A, B, C_IN;

output SUM, C_OUT;

assign {C_OUT,SUM}=A+B+C_IN;

endmodule

时序电路的设计

与组合逻辑电路不同,时序逻辑电路的输出不仅与当前时刻输入变量的取值有关,而且与电路的原状态(即过去的输入情况有关)。