概要

时间:2023.11.14 全天 ( 9:00 - 16: 20)

地点:北京望京. 凯悦酒店

主题内容:分享交流了Intel FPGA 产品技术优势和落地实践方案。

会议的议程

开场致词:

FPGA业务,是几年前intel收购而来的(Altera),并入后属于 PSG(Programmable Solutions Group),相信当初收购altera,是为了整合数据中心的业务,将Intel的服务端 优势扩大,但结果做得并不好。因此,PSG在明年会分拆独立运营,准备单独IPO(据说是为了更好的收回资金,重建晶元厂)。

会上宣布,在 2024.3.1 网上会直播 新的PSG第一次公开课。

注:从Altera并入Intel后,实际业绩一直在下滑(相比 AMD 的 Xilinx),拆开运营估计是要想扭转一下,另外,也可能认为主营业务有些拖了它的后腿。

* 2014年 Atlera 年销售额 19.3亿 全球占比 38% 同年 Xilinx 占比 50% FPGA全球 50亿

* 2015年 Intel 167亿美元 收购 Altera,整合数据中心业务,阻击ARM。

* 2019年,全球占比 34%,Xilinx 占比 52% FPGA 全球 60 亿

* 2022年,全球占比下滑至 32%,Xilinx 占比 54% 差距拉大 FPGA全球 78 亿

市场预计,2028年 FPGA全球规模 130亿(2023年 80亿)

2023年,PSG决定今年推出15款新的FPGA,此次会议,宣布了6款新品和平台(完成11款发布)

主题演讲:赋能可编程创新:

强调了三点:全新的产品组合,增强软件可用性,弹性供应链周期变长(这个我不关注)。

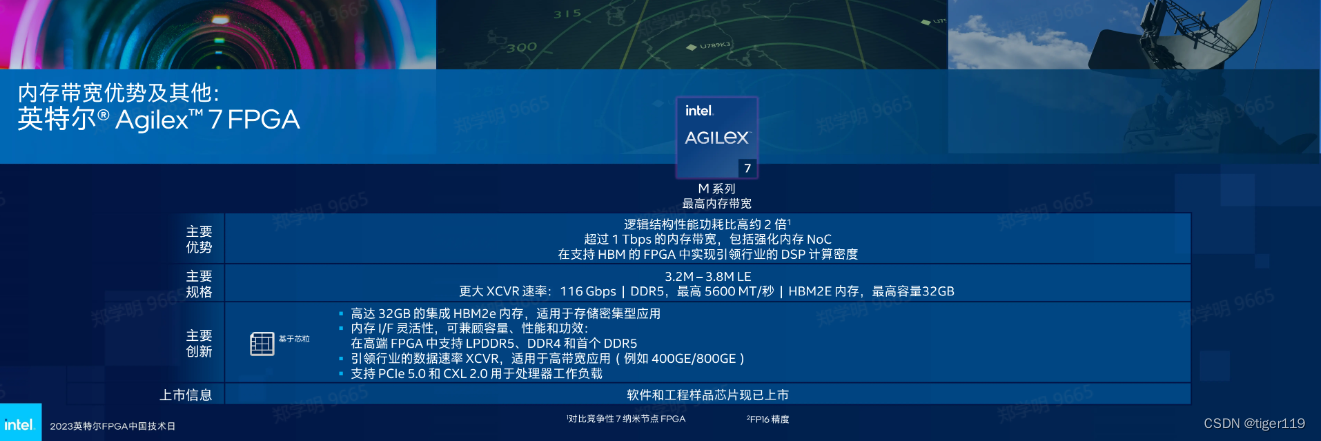

全新的产品组合:

3,5,7,9 全面的,全新的组合,涵概高,中,低端 ,所以可能(9系列面向无线RF)

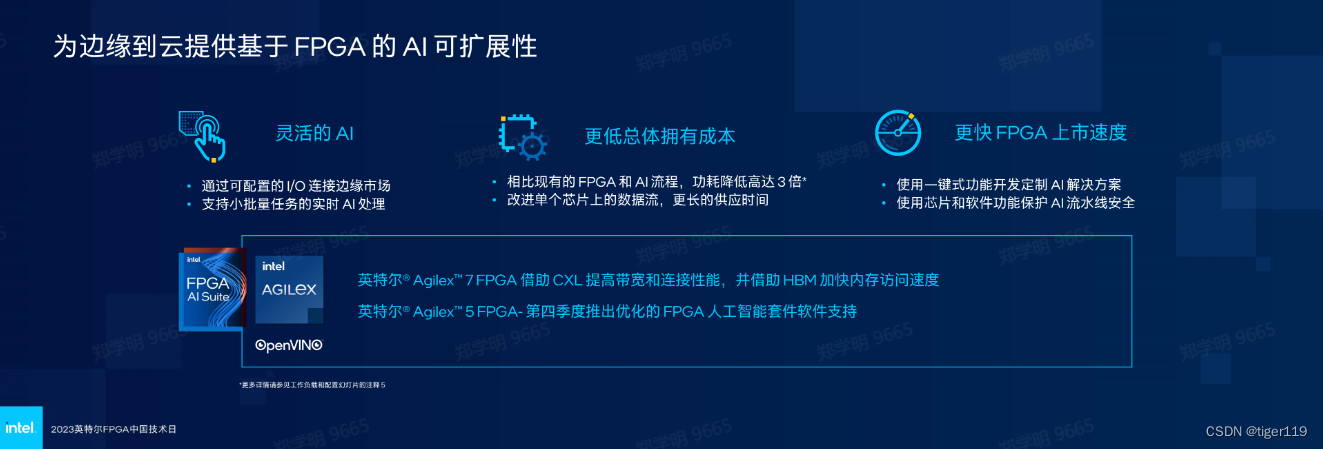

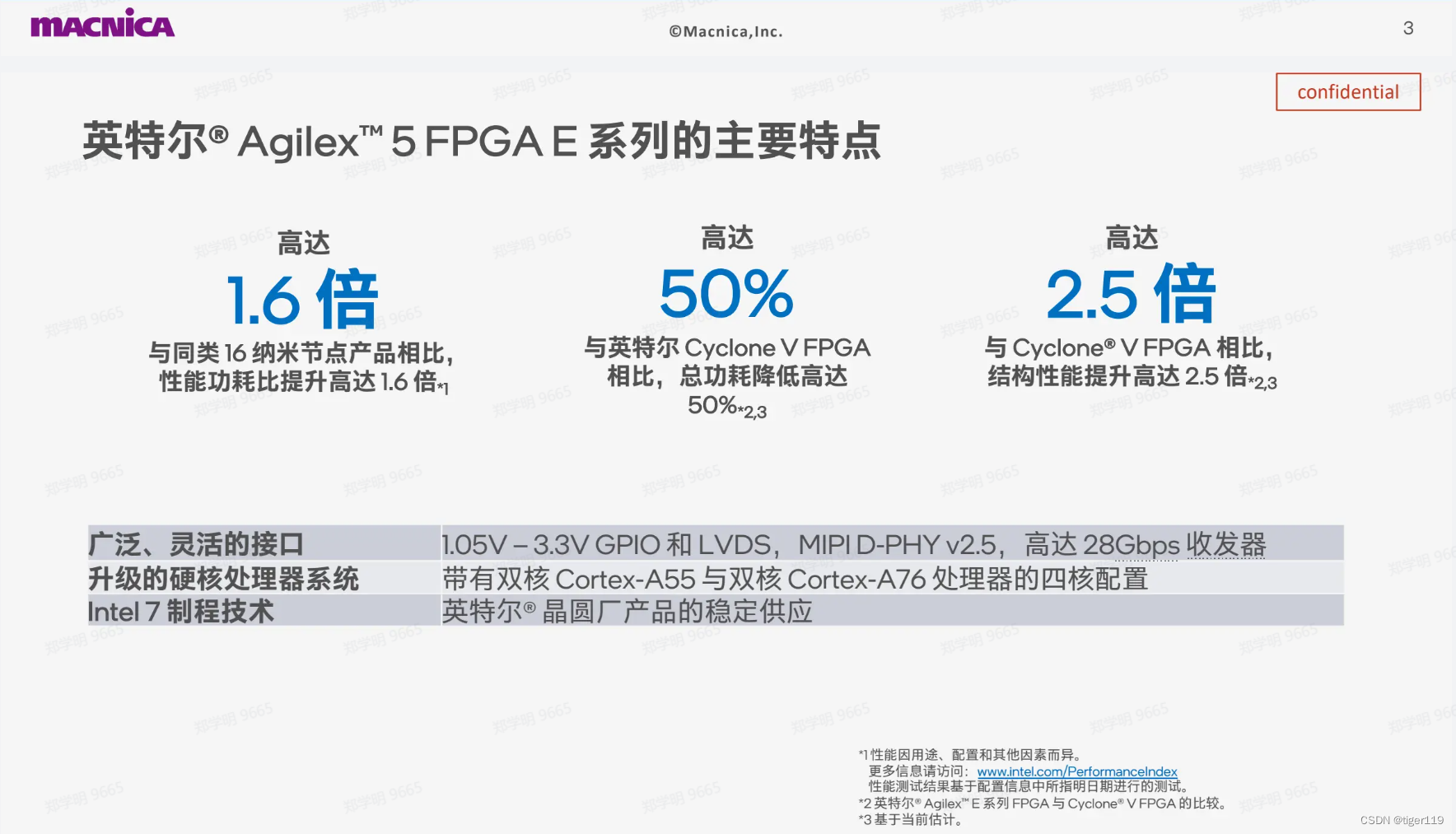

英特尔® Agilex™ 5 FPGA — 第四季度推出优化的 FPGA 人工智能套件软件支持

Agilex™ 7 FPGA 使用 CXL 提高连接性能,并借助 HBM 加快内存访问速度

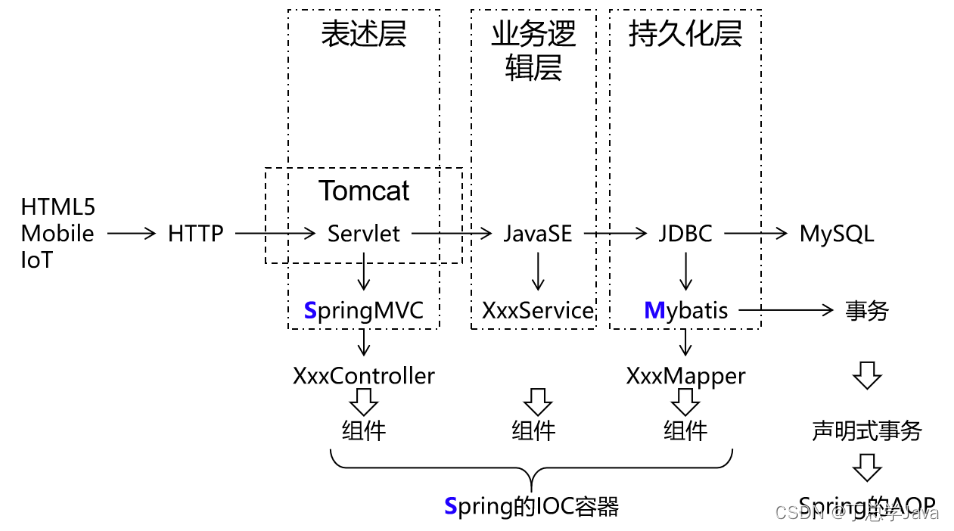

CXL(Compute Express Link)高速,高带宽的互联标准。使得FPGA可以有效的与CPU和其它组件协同工作,主要用在数据中心/云计算中心,推动计算和存储性能。

HBM(High Bandwith Memory )高带宽内存技术。

Nios V Soft Processer: 在FPGA 上的软核 处理器 基于RISC-V的架构。

F2000ipu: A7 和 Intel 至强-D处理器的融合,配合IPDK,进行数据平台和存储性能进行开发。

增强软件的易用性:

重点关注:

将 AI、C++ 转换为 RTL、RISC-V 和 Arm 工具套 件,就像添加 IP 一样简单。

与至强® CPU 实现全栈连接。

至于供应链,不是重点,就不说了。

三大关键市场的应用

后面有专门的主题讲解,这里就略过了。

主题演讲:全新的产品组合

产品组合原则:芯片异构化,更大的存储和带宽,AI加速

看看典型芯片的大小:

Intel 7 制程 10纳米Super Fin 技术。

(并不是7纳米,而是 10 纳米,不过,也不用太在意,本来这个计算就很不标准)

对于Agilex有丰富的组合,包括3,5,7,9系列,分别对标低(低功耗,低成本),中,高场景。

对于 9 系列,会上没提,我查了一下官网,实际上主要是针对无线的,添加了RF的支持。

所以,实际上容量最大的还是 7 系列

Intel 最大的逻辑容量是 3.8M,和AMD比,算是一个量级,但小了不少。AMD最大容量是 Versal P1920 的 5.6M。

另外,3,5,7,9系列都是有SoC产品的,只不过它搭戴的都是 A 核 ,并没有 R 核 ,这和AMD是有区别的,具体原因,不是很清楚,或者与Intel的市场定位或者AE的实施方案有关?

A5 四季度推出人工智能开发套件,值得关注!

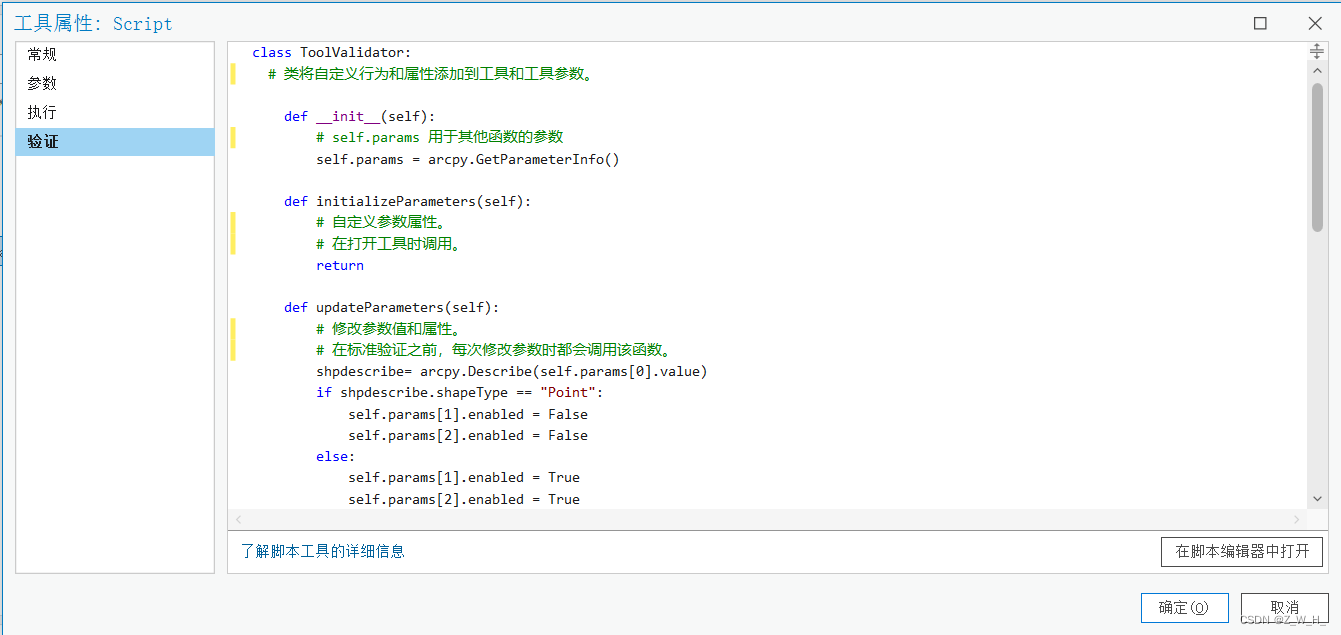

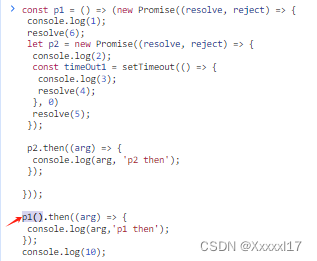

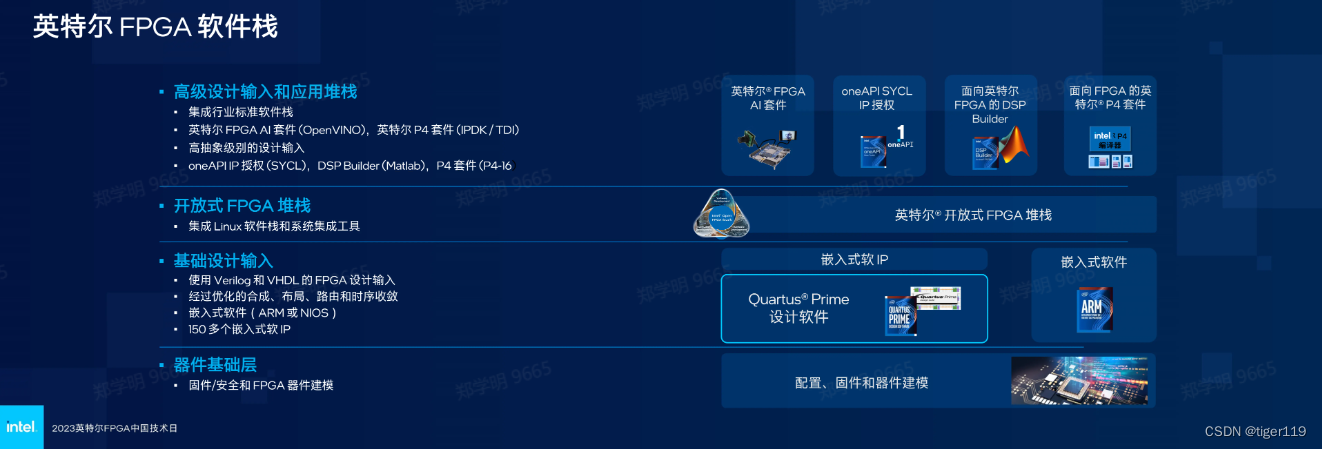

主题演讲:Quartus设计软件——简单易用

性能,UI/UE,社区支持 三个层面的支持

软件栈——对于开放式FPGA开发栈是不是有疑惑?后面再讲。

对于AI的开发套件,需要重点关注:OpenNIVO 是不是就是针对 FPGA 的重要的模型压缩/适配?

这里提到一个数字化的概念,也就是将一切可度量。把看似不可测的指标进行量化,达到持续改进的效果。

主题演讲:FPGA针对人工智能应用中的核心价值

好了,到了重点了。人工智能!!!!

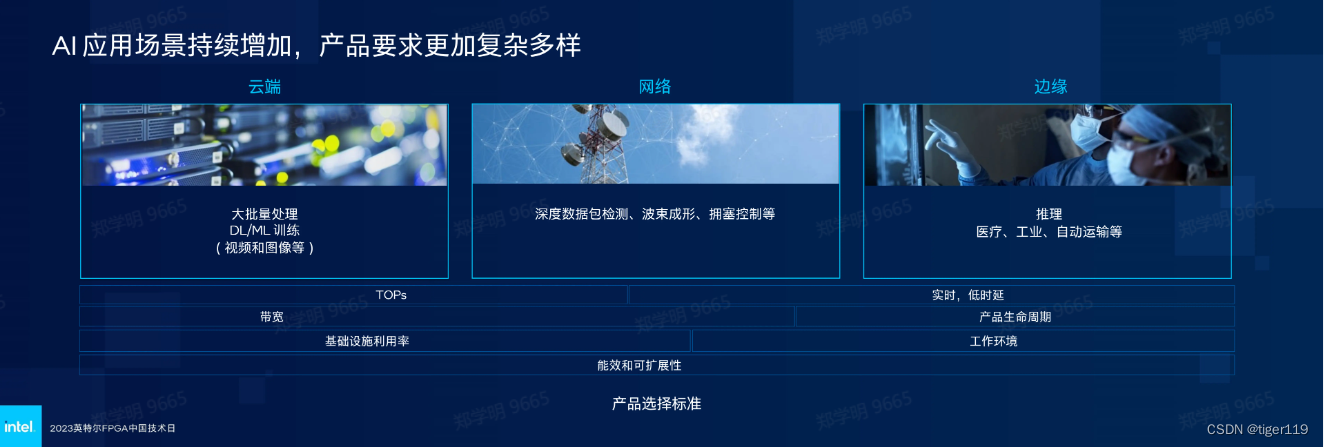

AI的挑战——低延时,安全,数据量,计算成本,新兴模型!

这个意思嘛 ,就是要引入边缘计算层

对于边缘层,可能有更多的想象空间。

插播一个广告——A5 For AI 即将推出

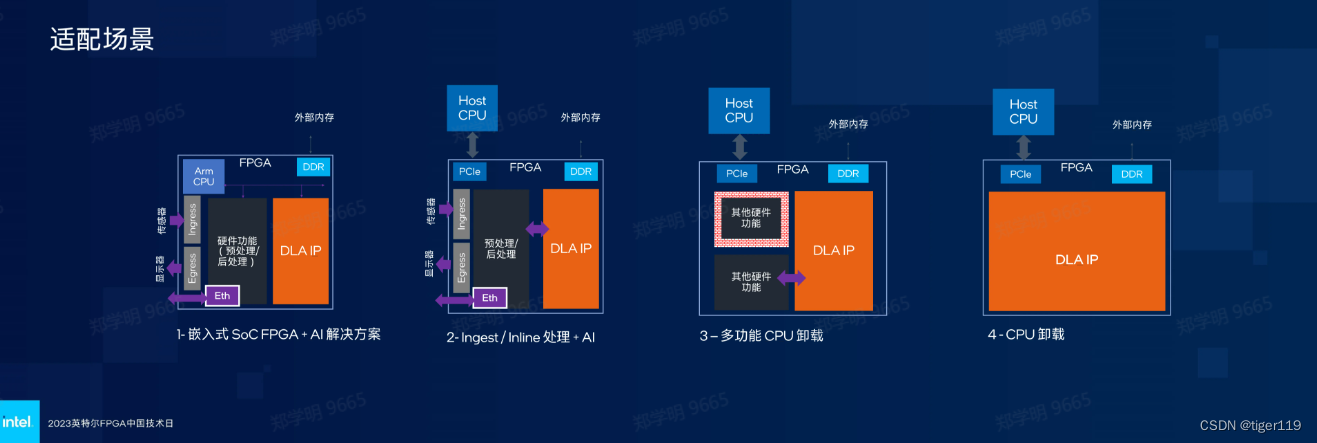

这个图非常重要,说明了几种AI处理场景,

当然,不一定是唯一的解决方案。

场景一:完成数据预处理和数据推理的全过程。完全可以完成一个边缘侧场景。比如一个工业相机,可以完成数据采集,预处理,图像识别,识别后的控制。

场景二:数据并不需要实时处理,是在端侧采集和简单处理后,传回电脑/CPU进行最终的分析处理。属于非实时的场景。这种没有用到ARM处理器。但是数据不能丢,需要有很好的传输通道,当然,最好做一些预处理,可以减少数据量(但又不丢失信息)。

场景三:数据并不做预处理,而是给回CPU,可能是一个多步处理的场景。

场景四:DLA IP独立完成AI工作,CPU只负责必要的调度。适用于HPC的场景。

注:对于DLA IP 需要有一定的了解,才能理解上面的场景。

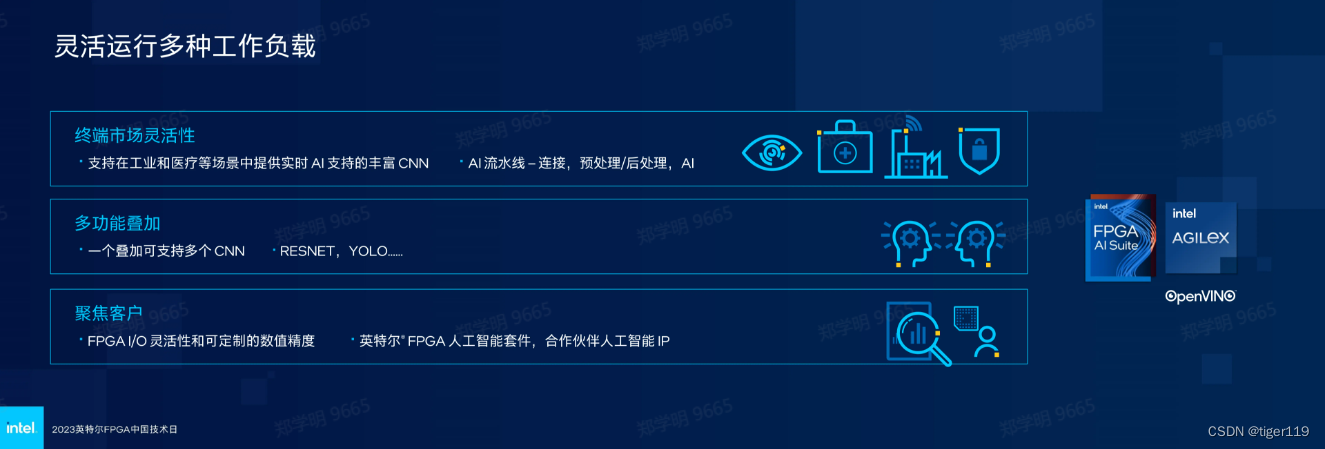

这里想表达的是,AI的应用会有多种组合(并且其中一部分也是辅助AI)

进一步表达,助力降低成本,实际上是在完成整个AI工程全流程(不仅仅是AI推理阶段)

这是AI开发的全流程:个人觉得没太看懂(因为没有实际使用过)

AI建模过程——这是一个通用的过程。并不限于最终使用什么解决方案。当然,因为知道是在受限设备运行,可能会选用tiny ML。

缺失和步预——我认为是缺失的,一定会有量化,压缩的过程,因为要在FPGA上运行。模型的容量是必须要处理的。否则,在后期处理,代价很大。

适配FPGA——我理解这是EDA工具链要做的。具体要看实现的架构。如果使用的是纯PL,那就是考虑如何将算子和计算流在LUTS,DSP中实现,需要相应的IP来支撑(预置的),然后配置这个通用的IP。

OpenVINO——这个软件鹕实没有用过,我理解是不是将高级的模型,直接转换。但如果直接转换后就直接到FPGA中运行,我觉得跨度有点大。按理应该要有一些通过IP 来支持。否则,太不可控,没有调整的空间。想想太难。对于 Xilinx的VITIS AI 在这块是做了很多工作的,并且,它们还主要针对AIE这种专用AI引擎来完成(难度降低)。

这块需要实际去做项目,在项目中学习,否则不太能理解。

AI 解决方案,也关注数据分类,过滤,传输,收集等,看似与AI无关的事情,但实际上,这类应用不在少数。

下午是平行的三个分论坛,我参加了一部分,其它没有参加的,因为开放日的视频和资料已经公开,我也补看了一下,也一并列出来,供懒人查看。

嵌入式分论坛:

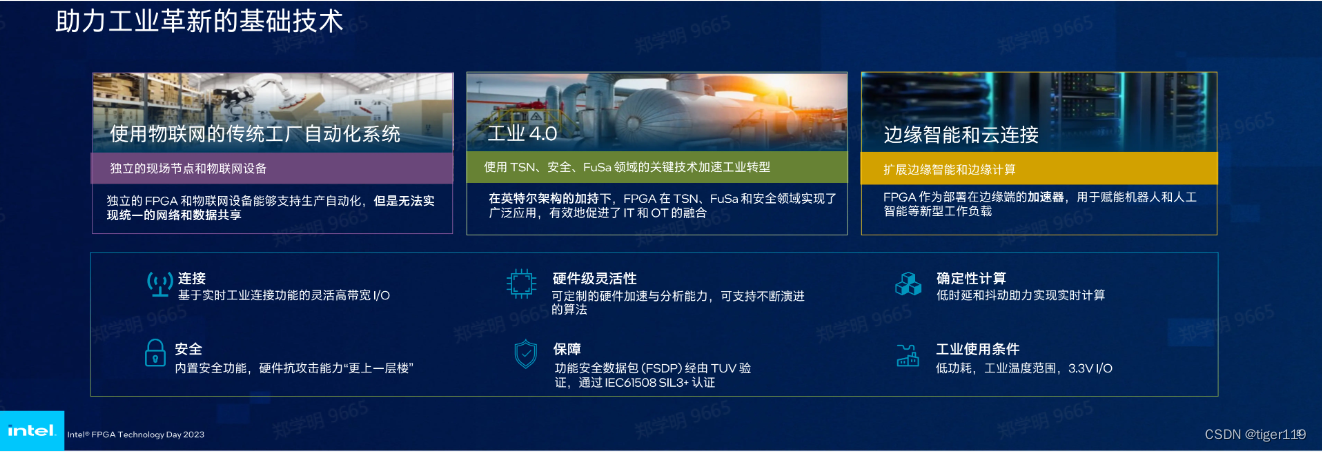

机器人与人工智能助力工业边缘变革

这是工业自动化的全流程——AI可能会改变某些环节,并且会造成最多的融合。

IT 在纵向(南北向),OT在横向(东西向),两者会产生融合。

下面提到的这些点,恰恰都是FPGA比较擅长的。

工业4.0重要的2项技术——机器人 & 人工智能

机器人领域的intel psg 解决方案

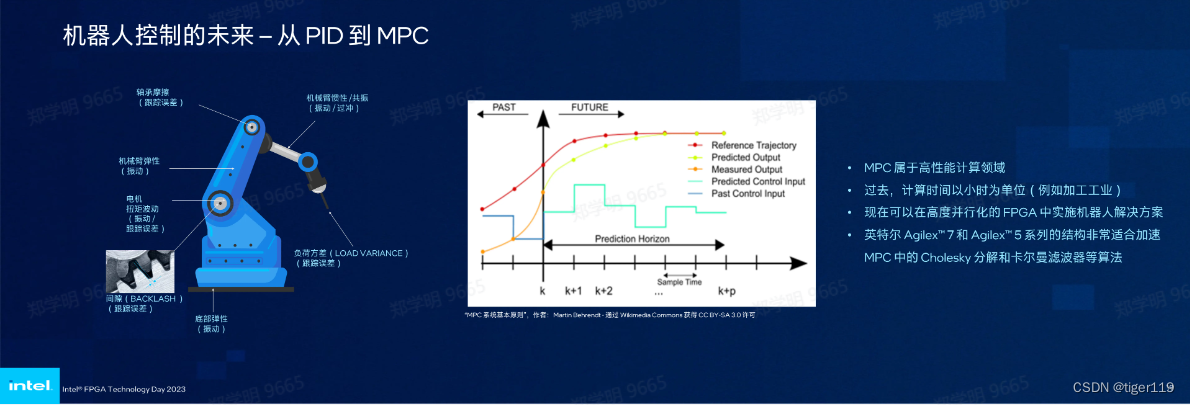

MPC技术优于传统的PID技术

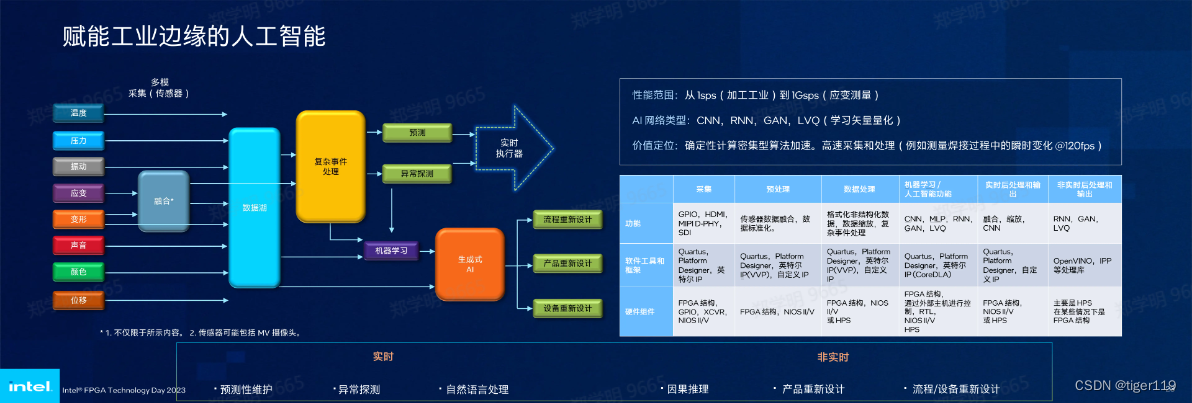

这里比较详细的写明了工业领域用到的人工智能技术

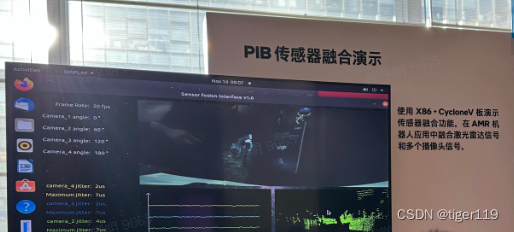

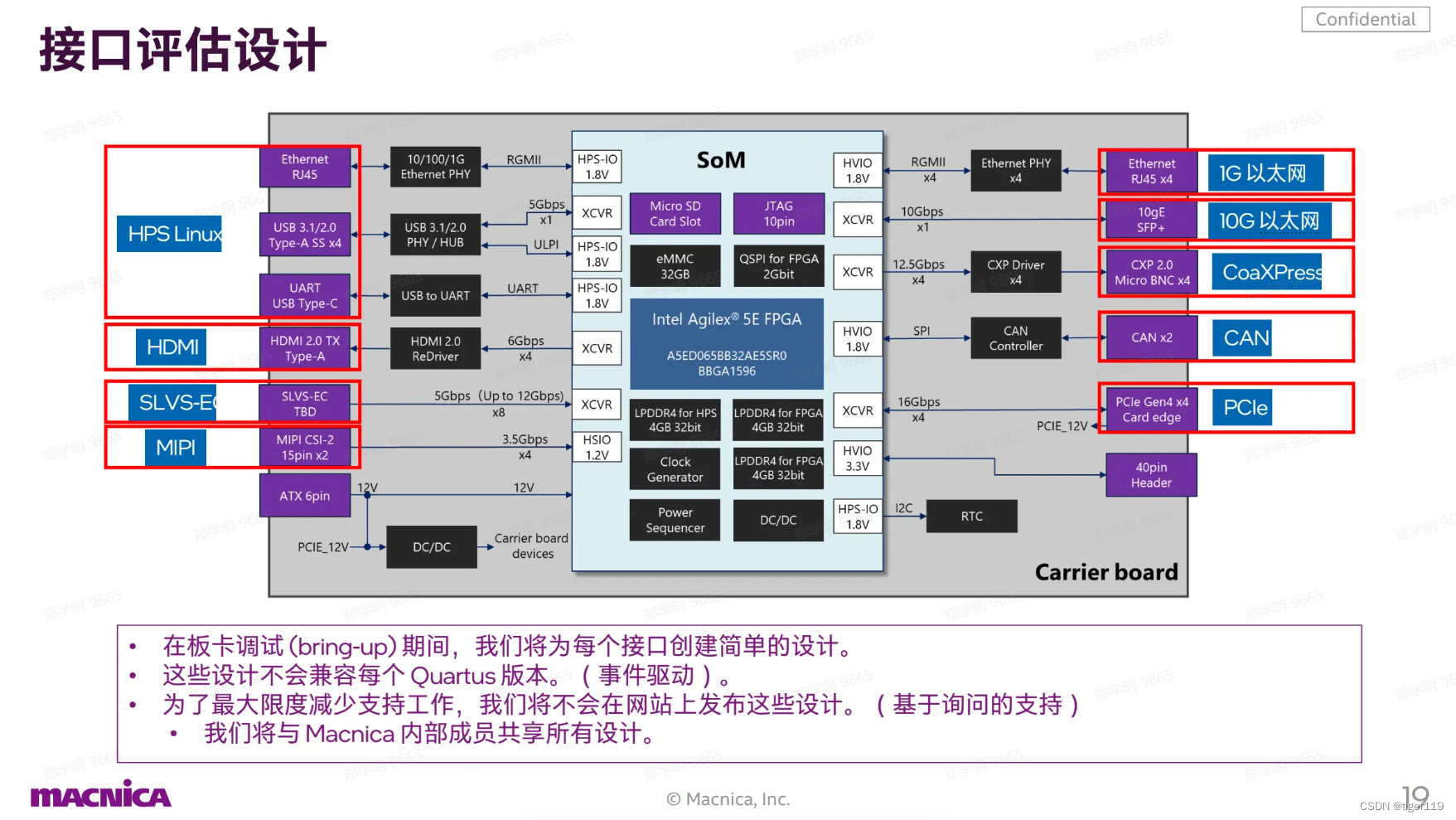

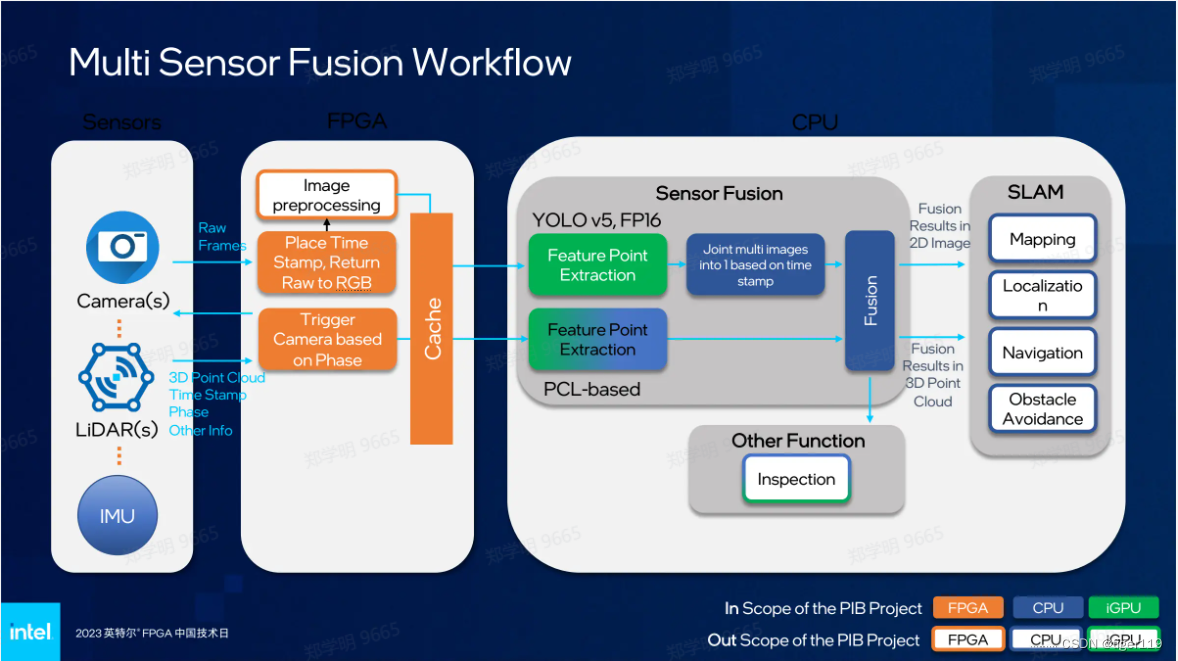

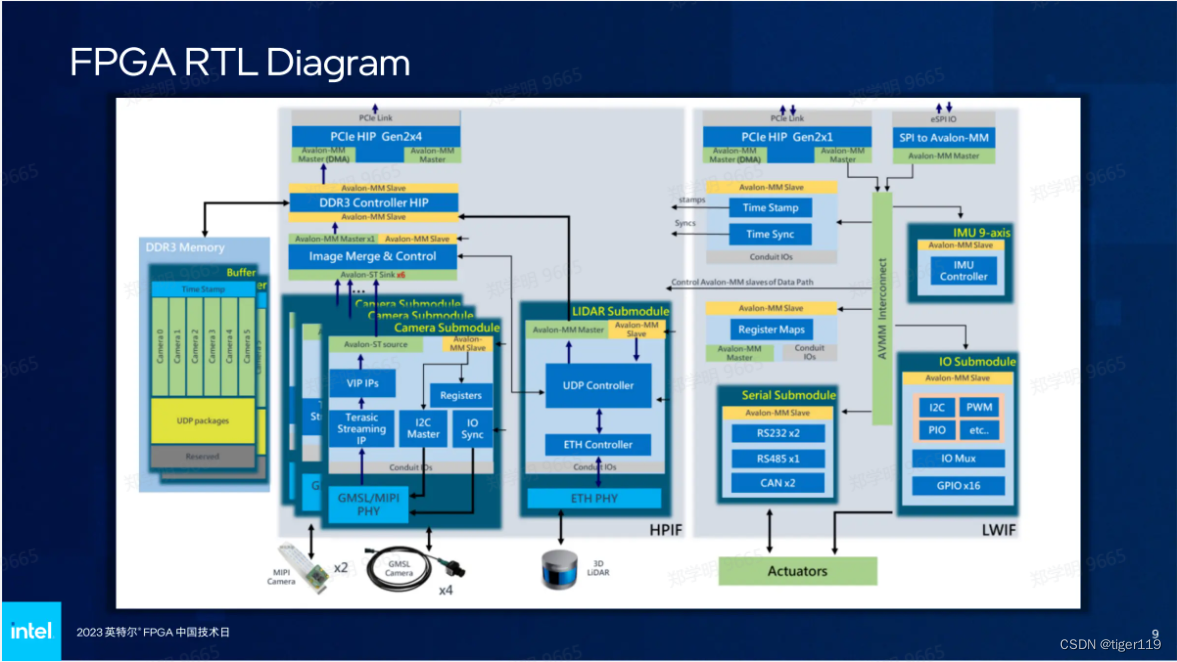

【展示】PIB传感器融合演示

提取有价值信息或做进一步的统计分析。

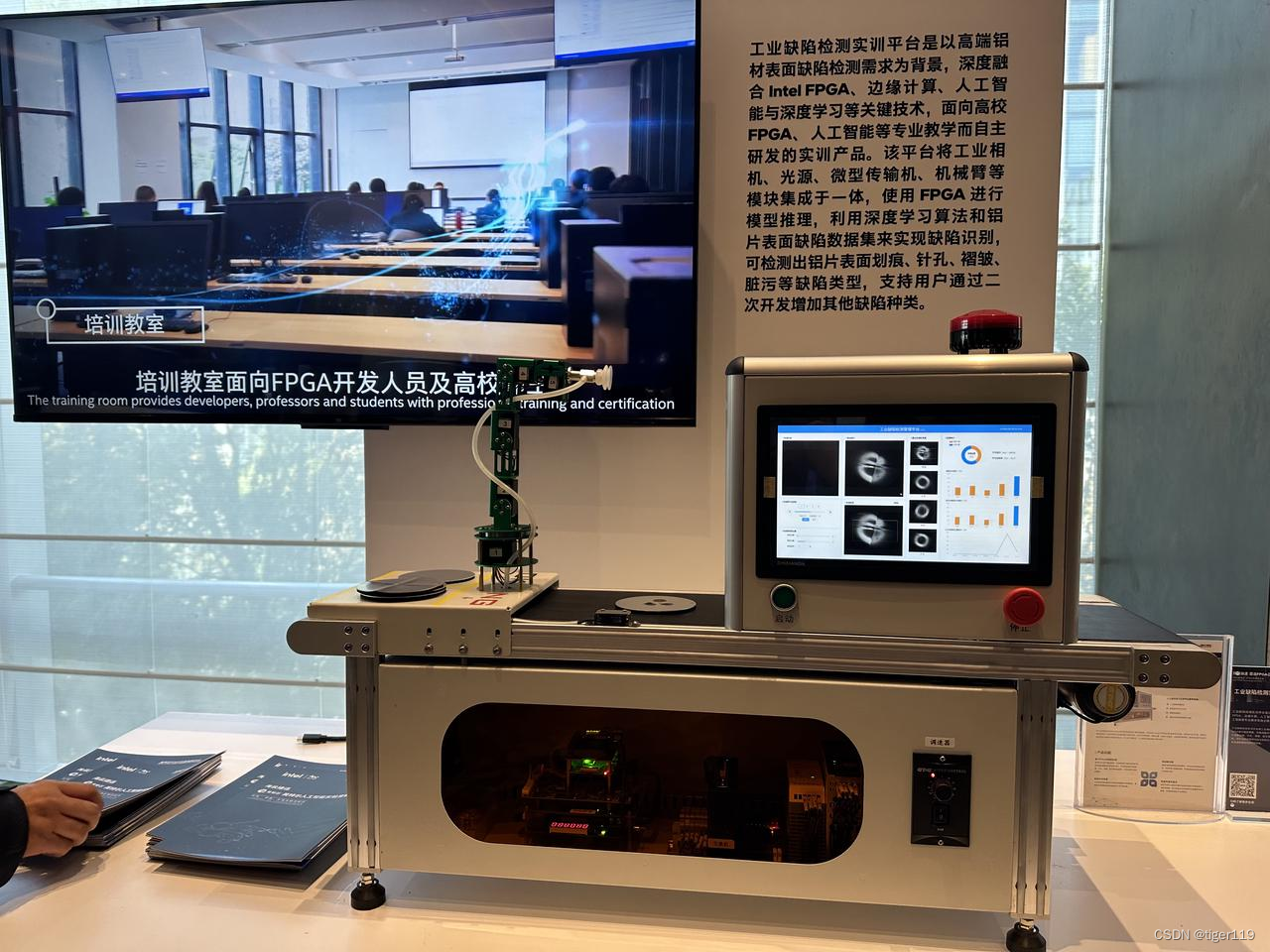

【展示】工业缺陷检测实训平台

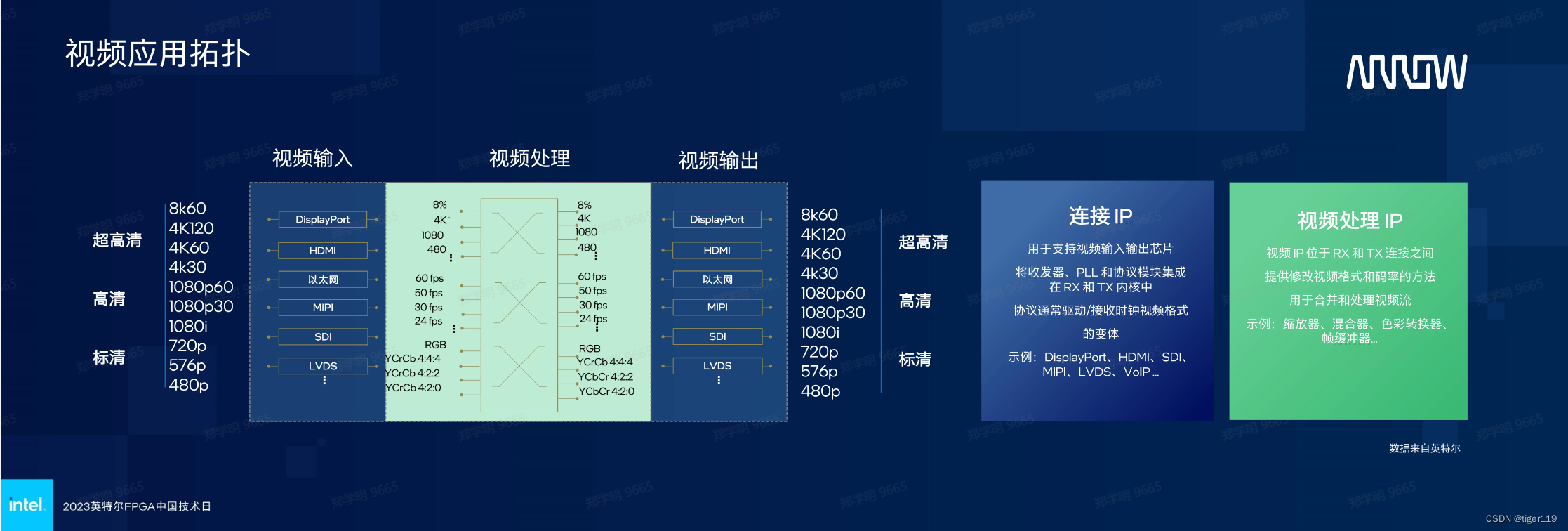

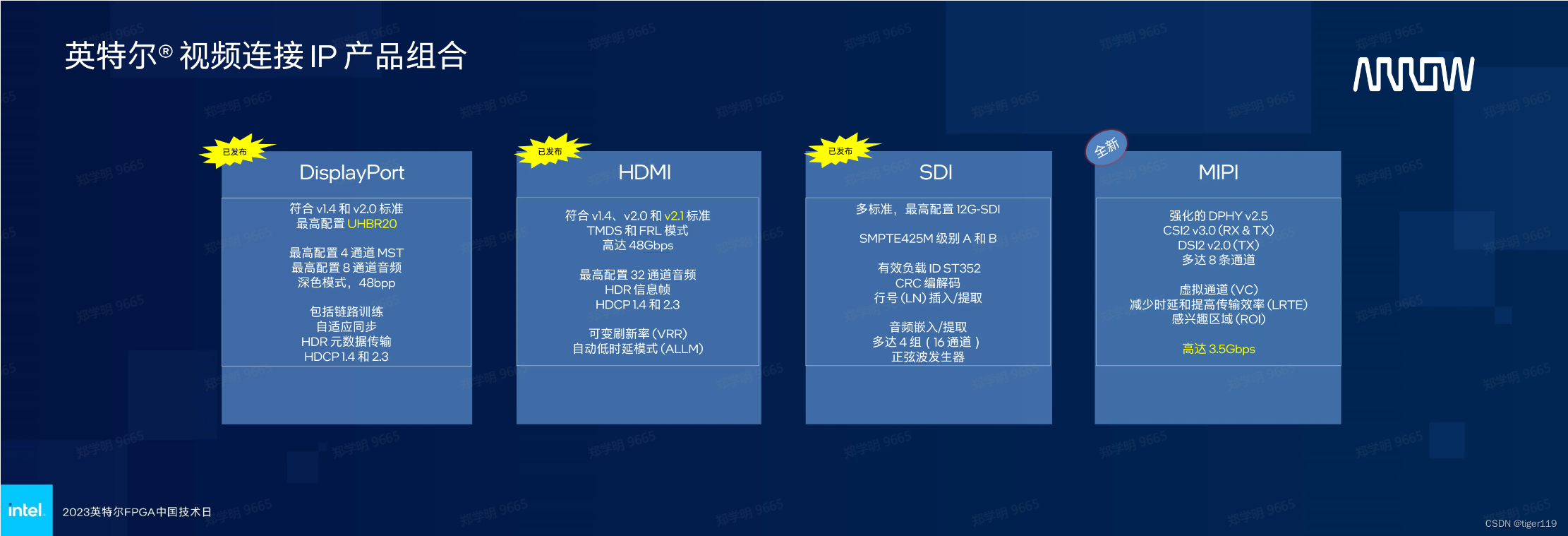

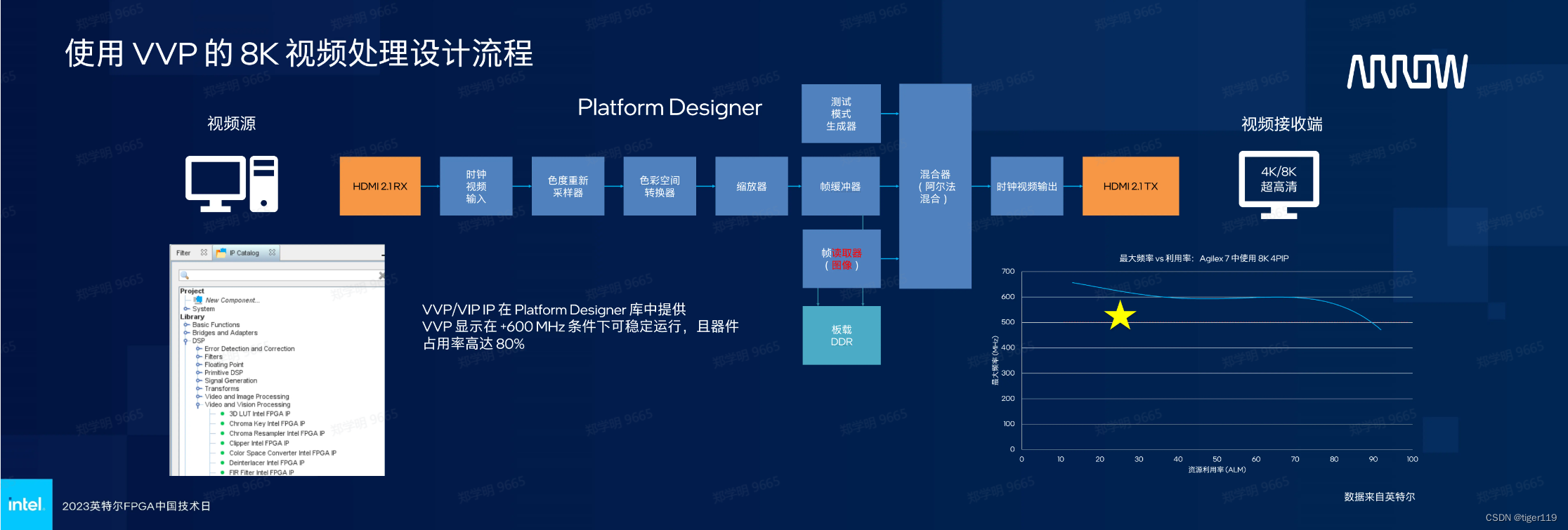

FGA 视频解决方案:

关键点:视频连接处理 + 视频处理

视频连接处理——视频信号的输入/输出,如何从一个设备传到另一个设备。处理数据传输层和物理层的事情:数据的打包,编码,解码,时钟同步(数据是要按时间排列的),信号放大。

视频处理——调整分辨率,格式,颜色,图象增强等…… 需要复杂的数学运算。

常见的,能支持8K的视频接口。USB之类的肯定是不行的了。注意:MIPI是一种全新连接方式。

注意:VVP是全新的,提供A7和5D支持的技术,专门针对8K的。

重点讲了VVP的处理细节:具体就不讲了。

现场有看到相关的展示:

【展示】编解码器(KCL-100)

0延时,视觉无损,轻压缩IP传输编解码器。

公司:广州柯维数码——专注音视频解码底层技术与实现技术的研究

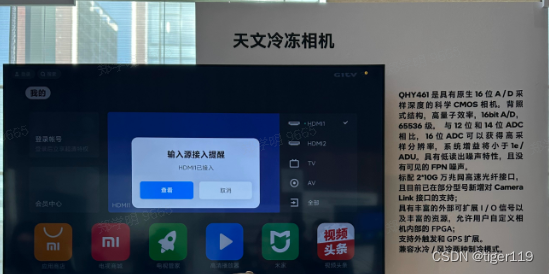

【展示】天文冷冻相机

CMOS相机,处理传感器的原始数据,实时数据处理,提高曝光期的图像质量,可针对特定的观测目标或实验条件进行编程。信号同步。

【展示】(LILMON5)摄影监视

4K高亮 1000尼特单反微单摄影机HDMI监督。

FPGA应用点:实现H.264或H.265的视频压缩,运动检测,识别跟踪画面中移动的图像。可以实现人脸识别,处理多通道的视频流,实现多画面监控。

【展示】Intel图像处理 IP

【展示】ISP-Intel图像处理IP

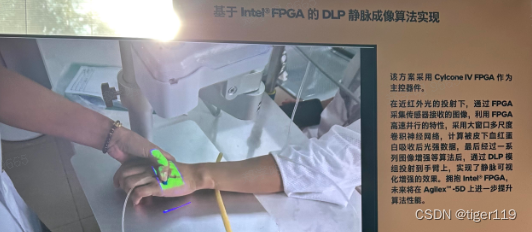

【展示】DLP静脉成像算法

DLP静脉成像——高精度的安全的生物识别技术

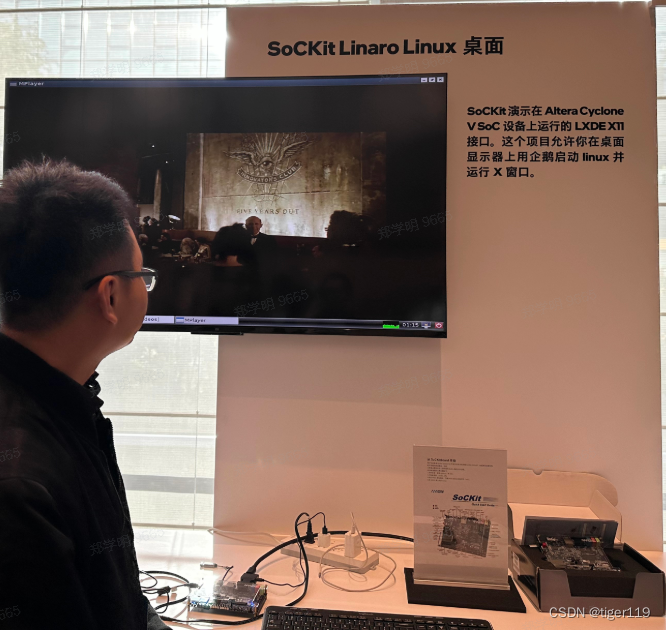

【展示】Linux桌面

让视觉无限延伸

好了,一定会扯到元宇宙的。

有这么一个新技术,我理解就有点象祼眼3D。

这算是一个广告吧,说实话,我觉得效果一般。之前在深圳见过这么一家企业在做,效果不好。现场好象也有展示:

【展示】祼眼3D显示屏技术

使用FPGA完成大量的数据运算,光线,位置,不同的算法(可能变更),低延迟(可以获得更好的观看体验)。能效比:相比CPU和GPU,FPGA在运算时,能耗比更低,更加节能,并且可以维持更长的时间。当然,FPGA还需要和GPU进行协同运算,达到更好的效果。

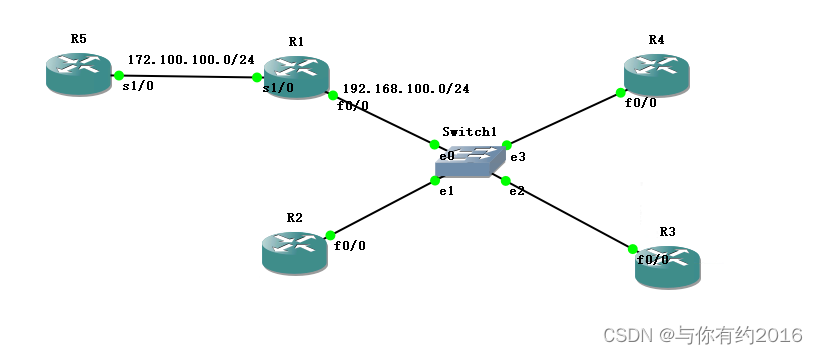

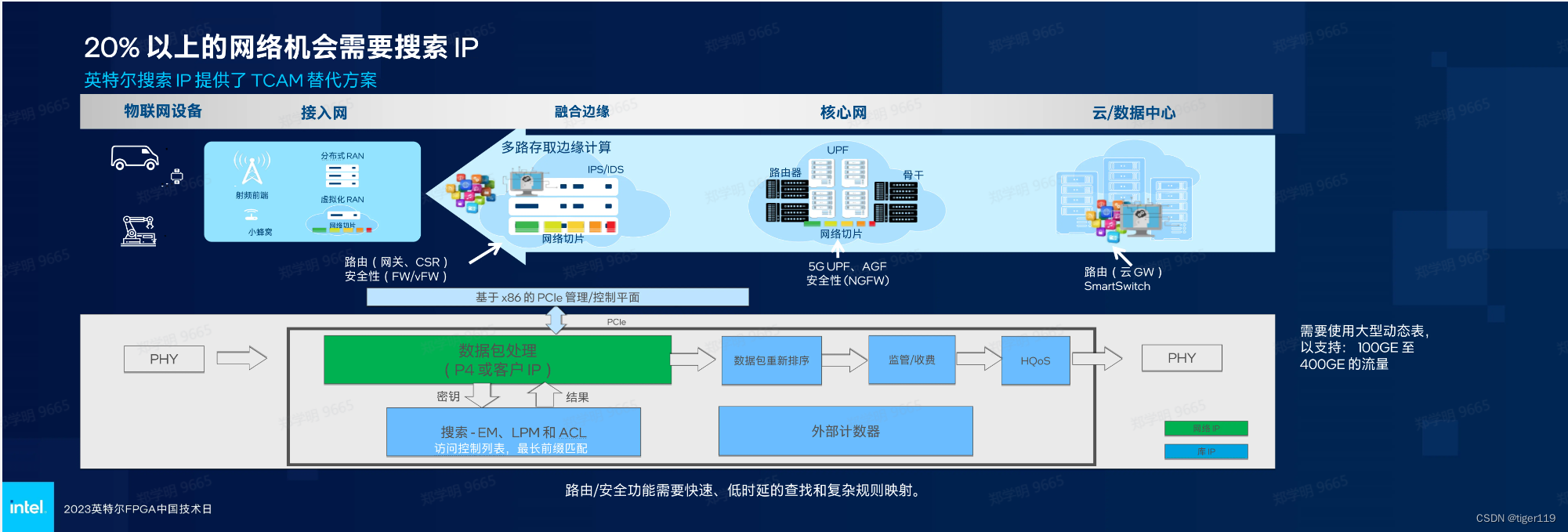

网络与云分论坛

蓬勃兴起的网络转型

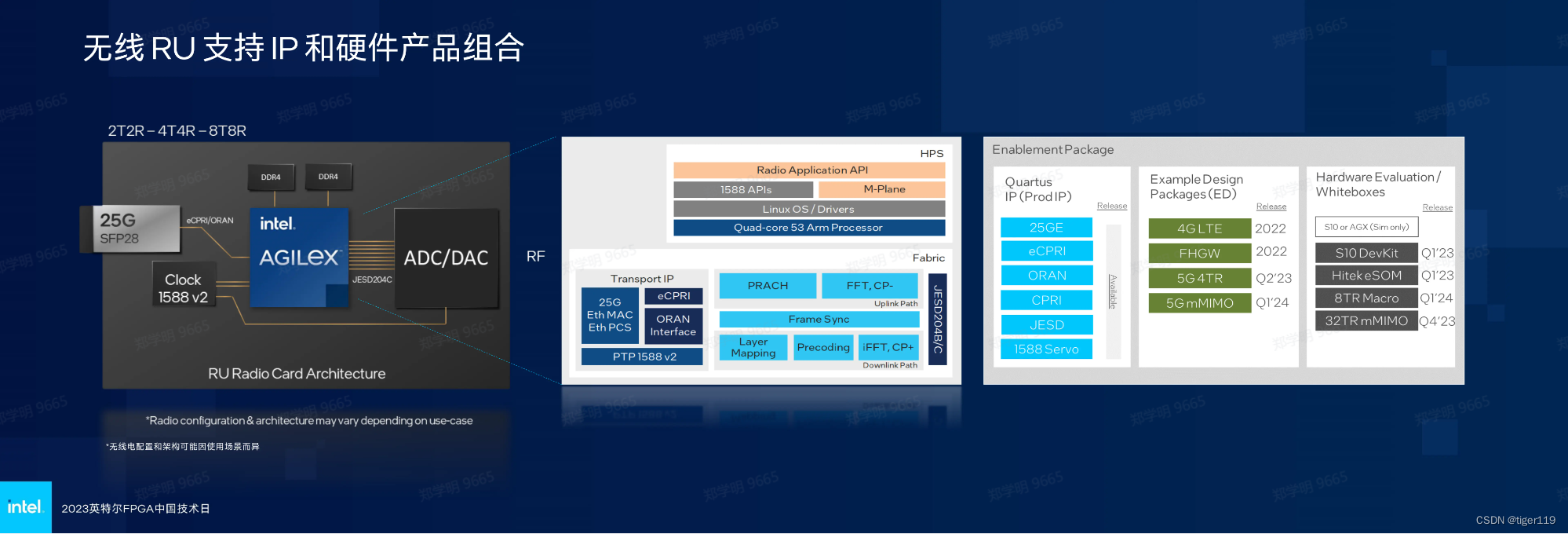

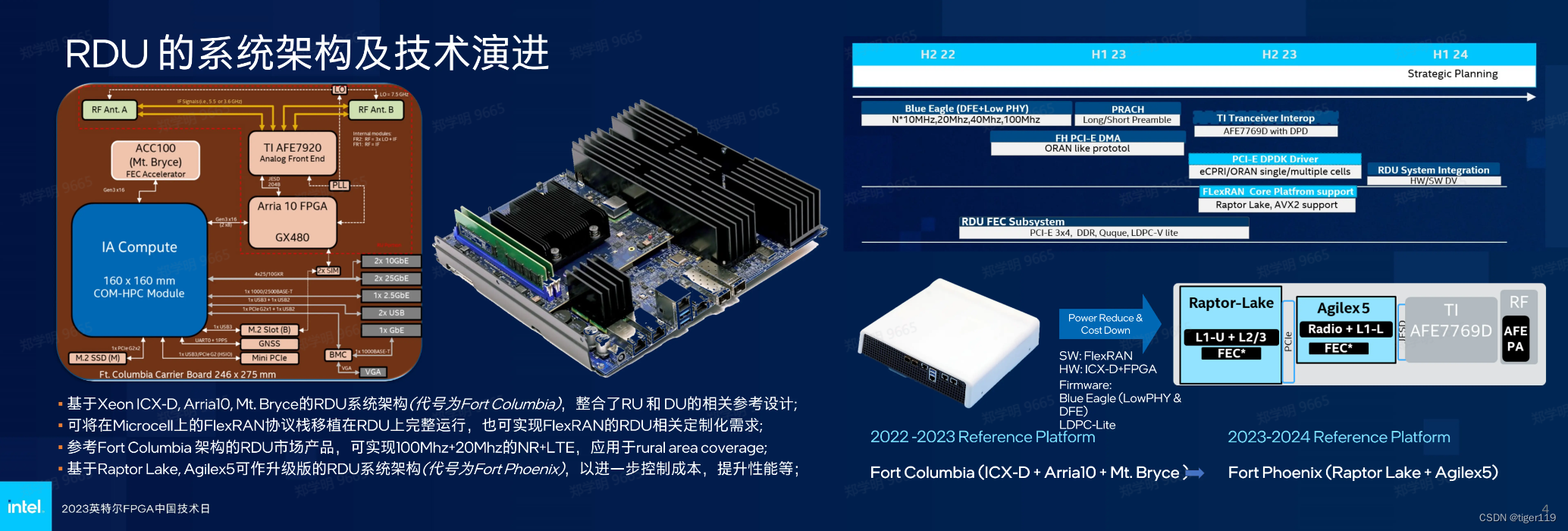

RDU 5G一体化基站解决方案

RU:接收/发送无线电波,与RF相关

DU:信号解调,编码,解码功R能,处理和准备数据。

【展示】RDU 5G 一体化基站解决方案

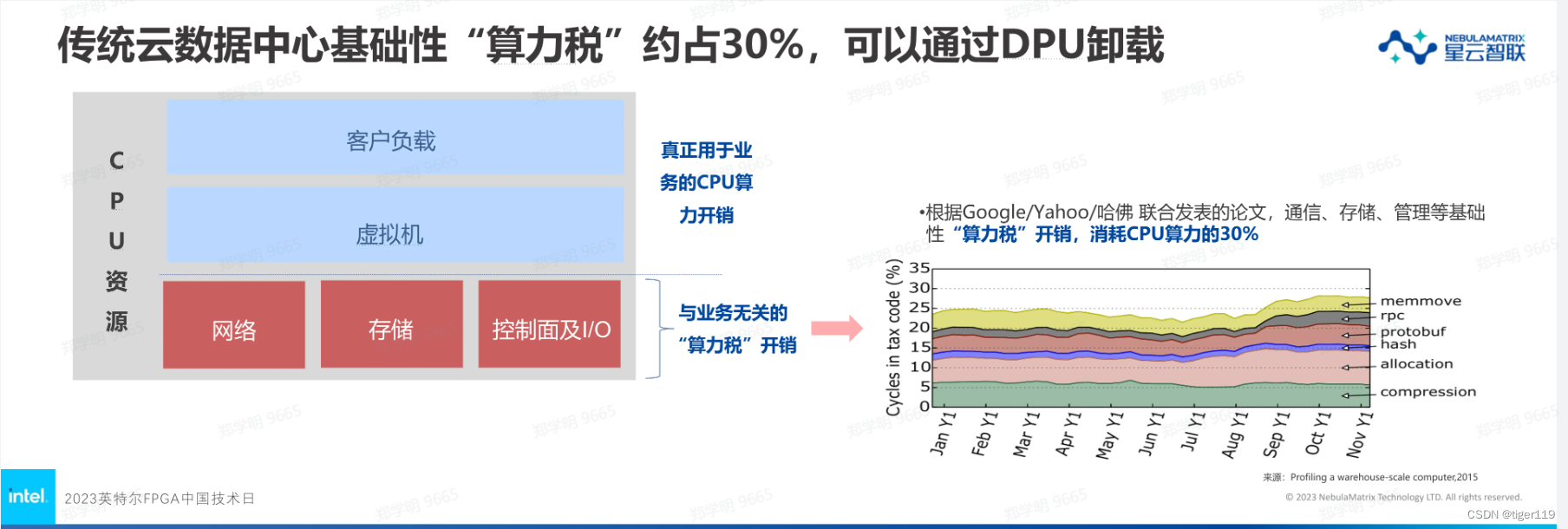

FPGA助力数据中心演进

这是Intel的强项,在持续发展中…… (2015 年,MS 开始 智能网卡,AI加速)

加速包括两方面:

一方面:对于数据中心基础设施加速(计算,存储,网络资源)(用户不可见)

另一方面:应用加速(AI,计算,大数据)

数据中心应用的几个场景

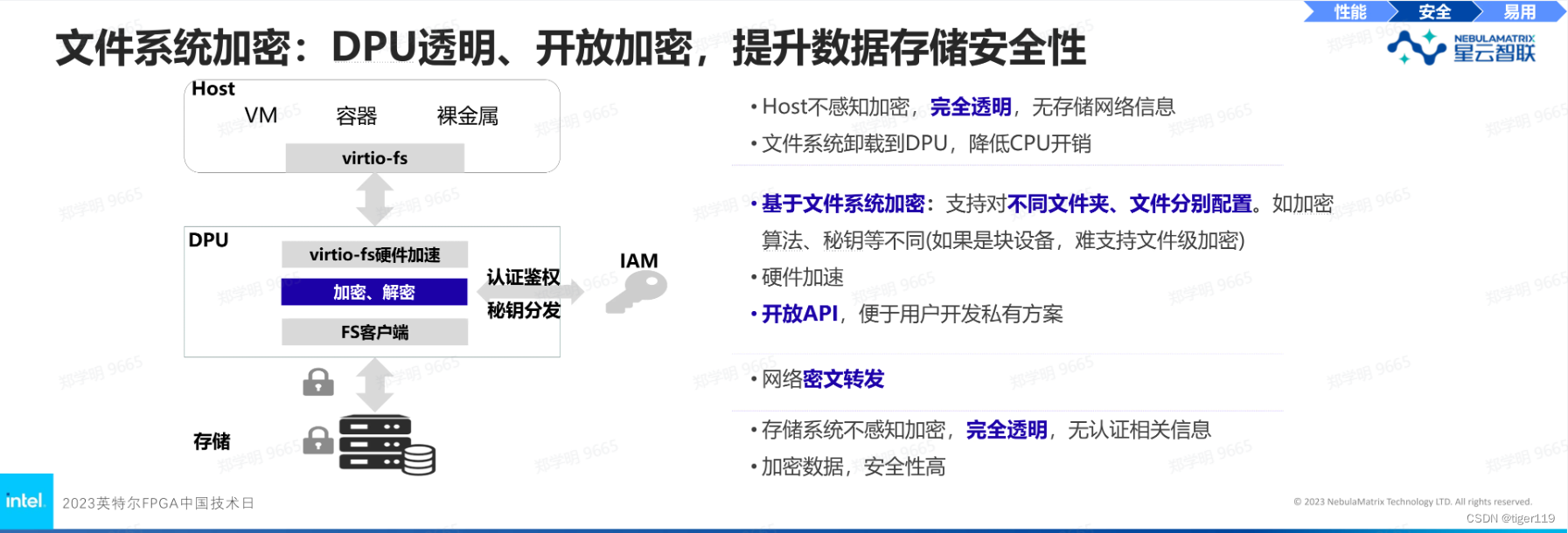

1:计算优化型实例 ——FPGA实现 高效并行运算,网络/存储虚拟化(网络存储,网络防火墙,负载均衡等功能,将网络/安全/存储进行处理) (IPU,DPU,SmartNCard)

2:存储优化——把存储盘进行虚拟化,冗余/容错管理,进行一些运算(加密/压缩),把存储挂在FPGA上来进行管理(数据传输过程中,可以预处理数据)

3:内存优化——这个比较新一点。和硬盘一样,将内存解藕。服务器中的内存容量不可弹性。FPGA进行内存管理(内存扩展,内存池,通过CXL与CPU相连),内存池化(加一个内存盒,内存可动态分配和分收,与存储类似的处理),(增加内存节点,或者GPU的加速节点)。

4:存储阵列,内存池——实际上是把存储和内存虚拟化。变成可弹性使用。

方法一:存储服务器来处理(CPU和网卡)。方法二:FPGA直接挂盘(完成控制和网络传输),没有CPU。

5:存储控制——存储池在异地,需要做控制。冗余运算,分配等处理。

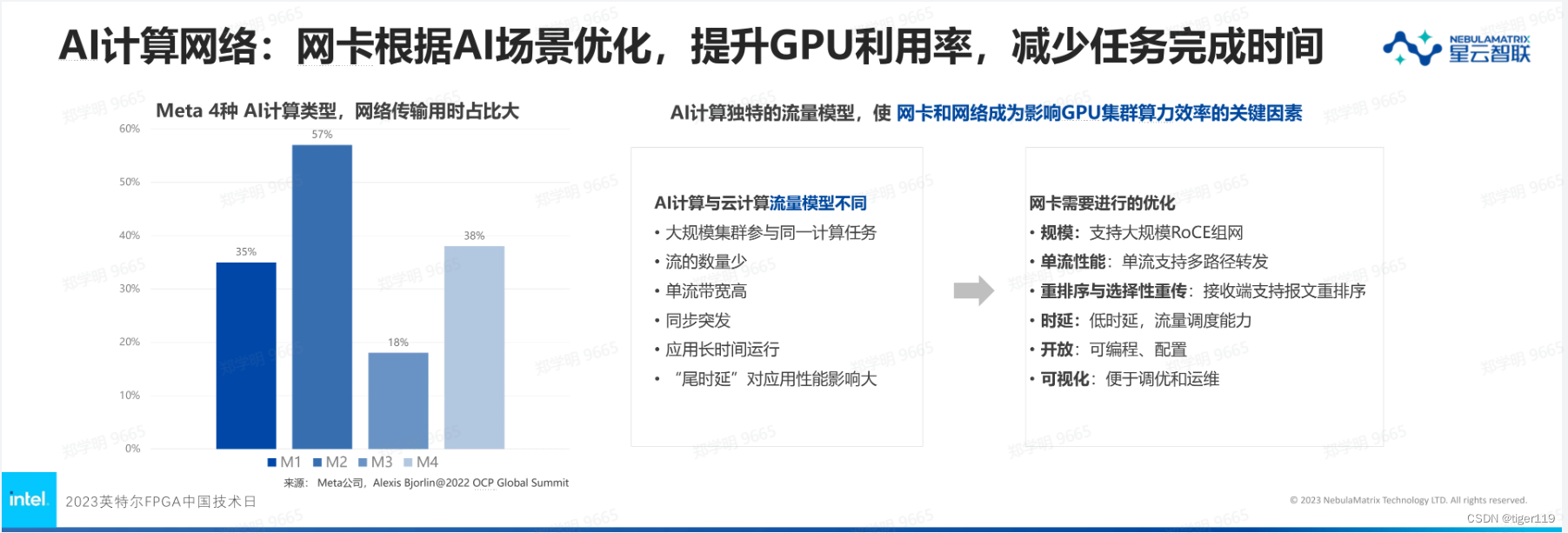

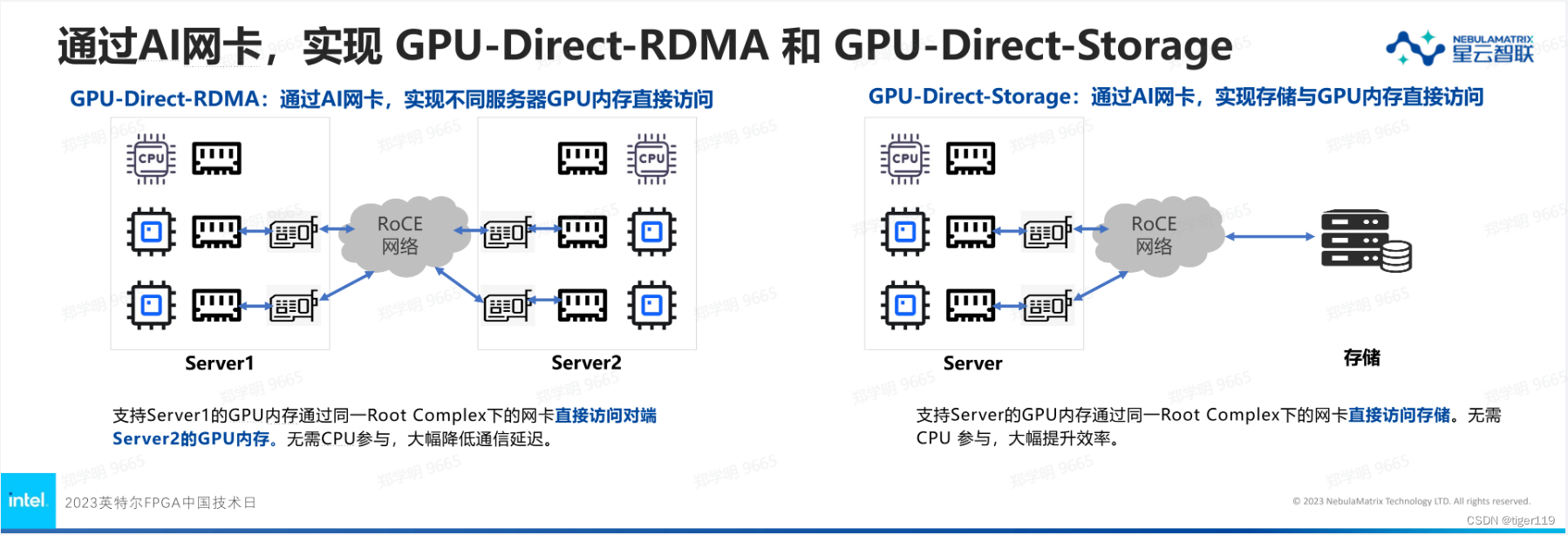

6:AI 应用——完成机器学习,搜索,数据分析等专用的计算。需要IPU,推理,训练(训练大多还是在GPU中完成)。对于GPU的集群管理,可以使用FPGA(服务器与服务器之间的联系)。

实际上,对于数据中心的增强,一直是intel的优势 ,因为它本身还有CPU的优势 ,它可以把CPU和FPGA之间的数据交换和指令交换做得更加极致。

主打低延时和高吞吐量,适用于金融的实时交易领域。

进行实时的机器学习的推理运算。

对内存进行池化,最大化利用,使用CXL优化速度。

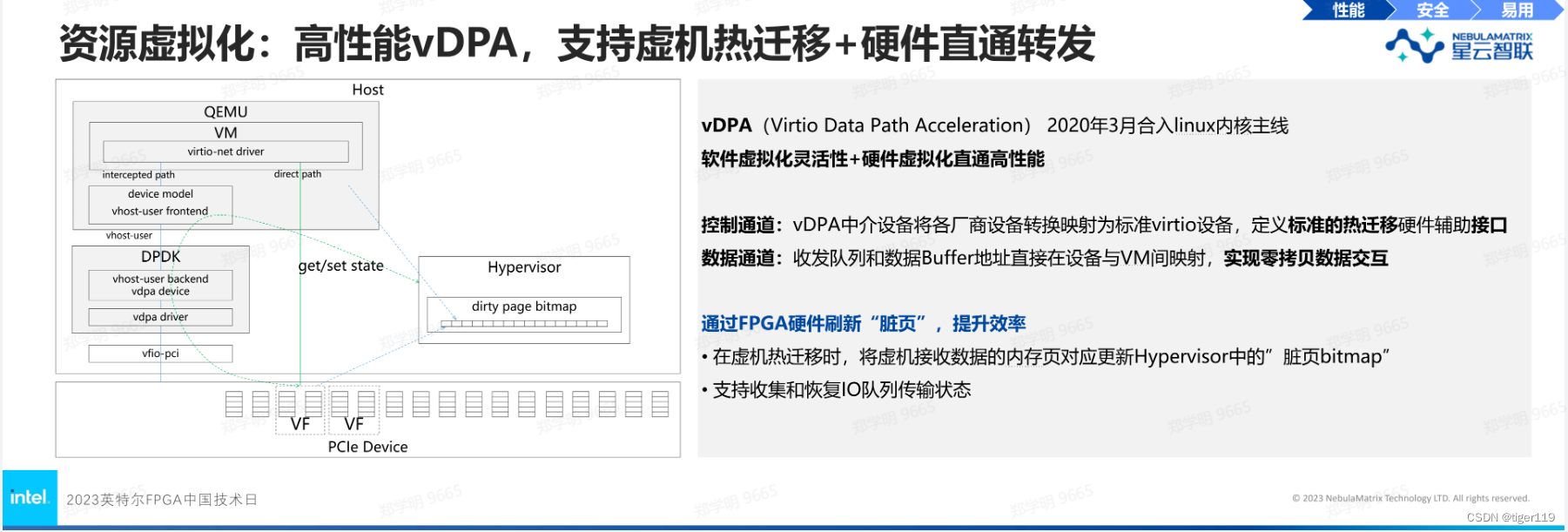

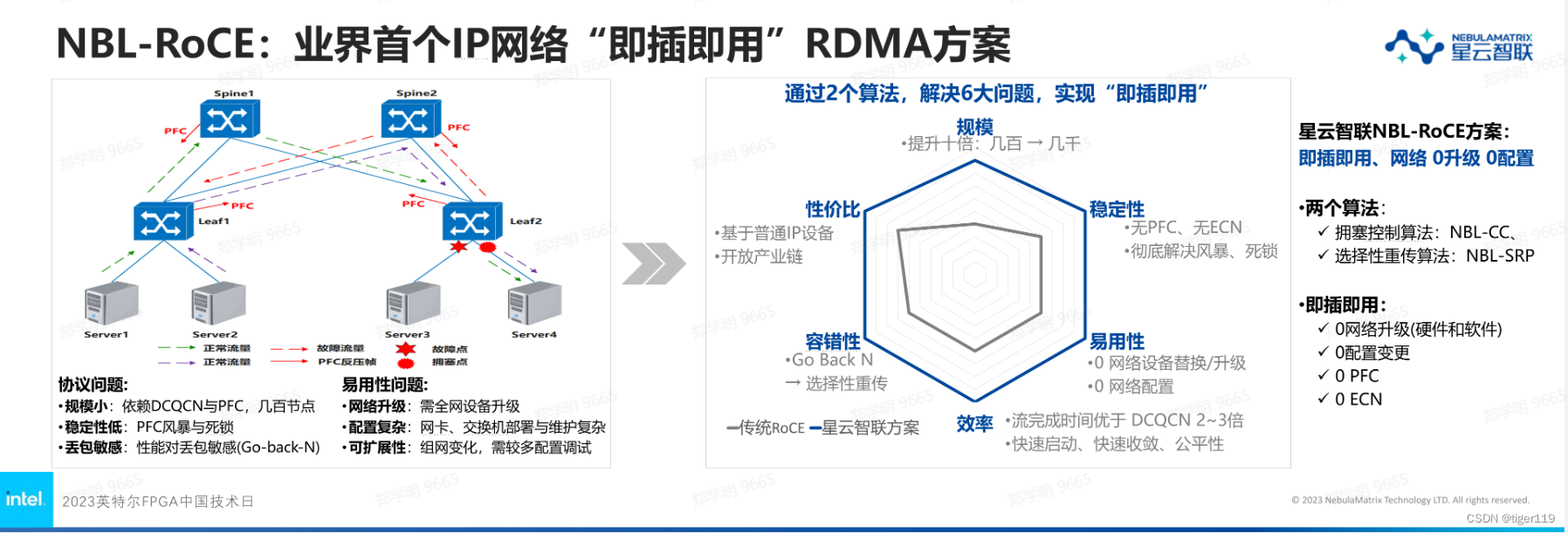

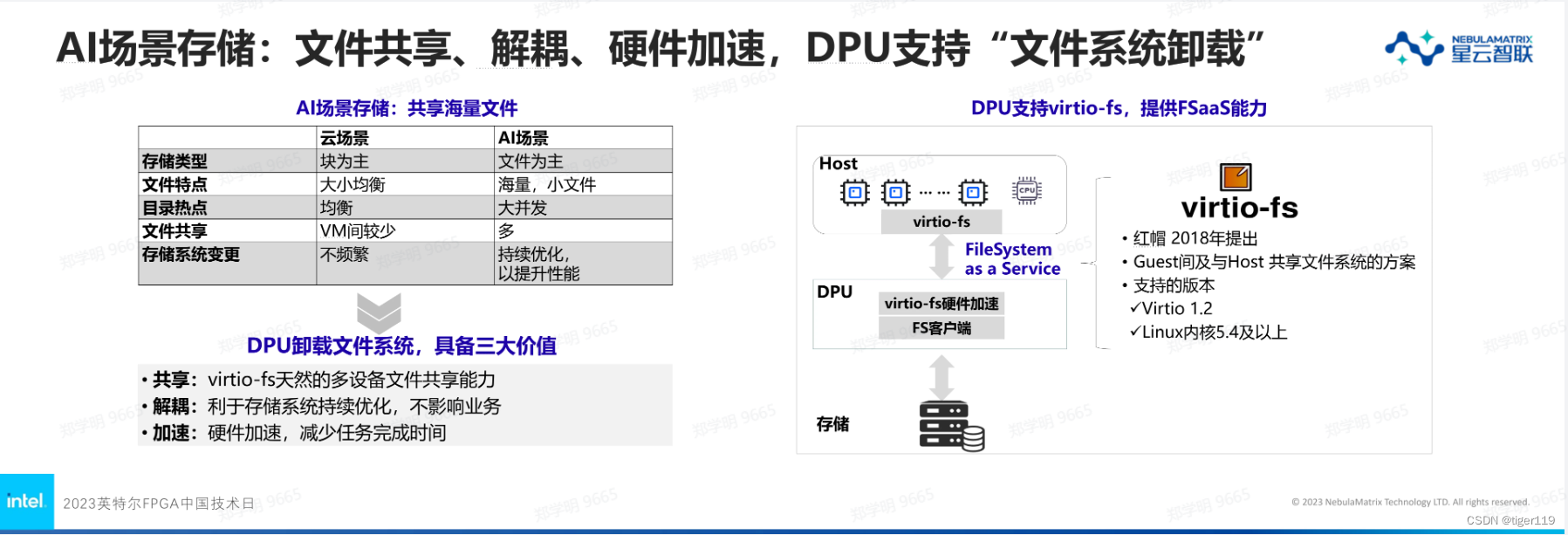

基于FPGA的DPU智能网卡解决方案

这一节更象是广告,主要是介绍星云智联这家公司的产品。

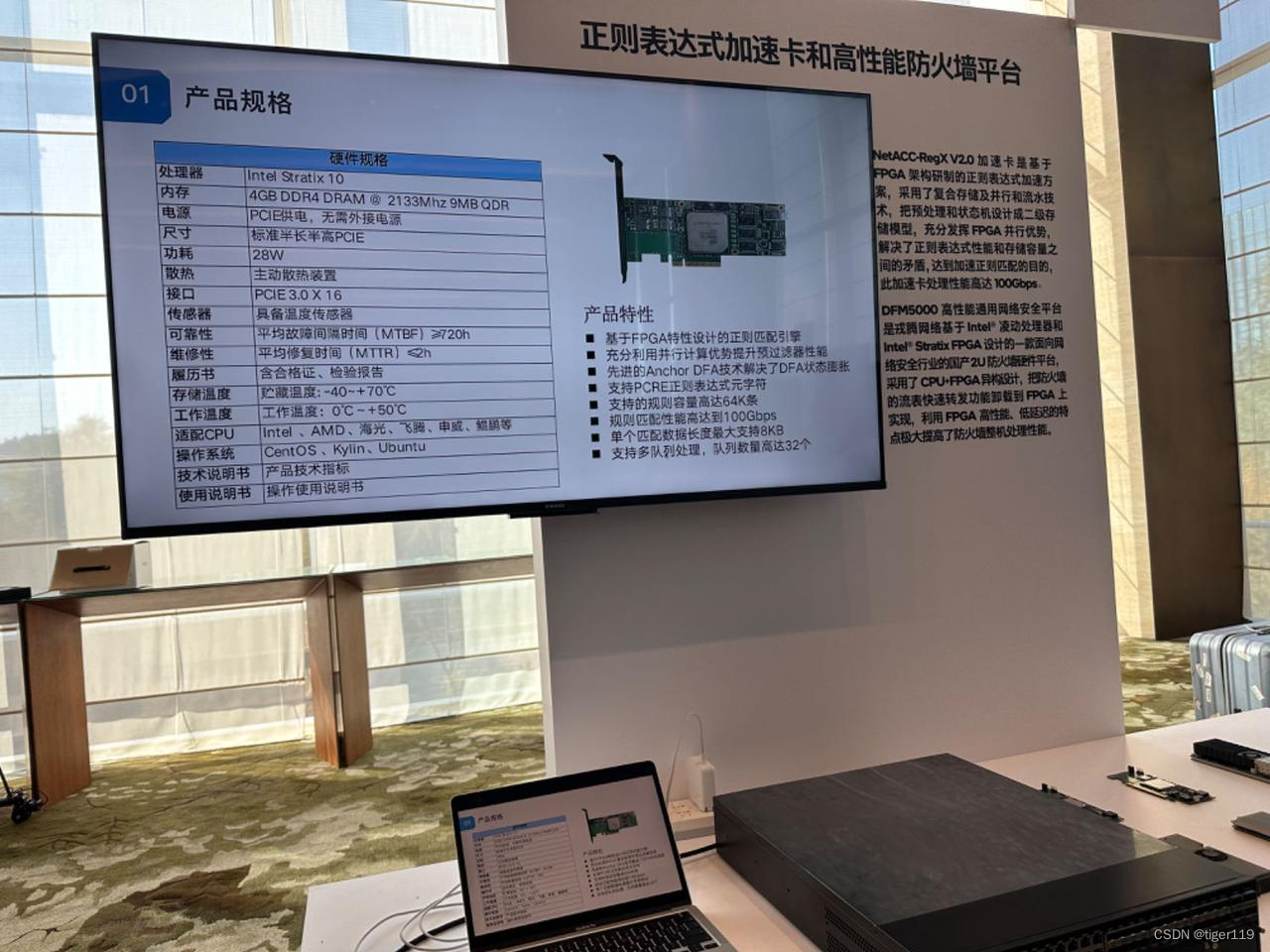

【展示】Net ACC- RegX V2.0 加速卡

功能:用在防火墙方案,DFM5000高性能通用网络安全平台。国产2U防火墙硬件平台

原理:采用复合存储及并行和流水技术,把预处理和状态机设计成二级存储模型,充分利用FPGA并行优势,对正则表达式的运算进行加速,利用FPGA低延迟的特点。

使用 CPU- FPGA异构设计 Intel凌动处理器 和 Intel Stratix FPGA

性能指标:此加速卡处理性能高达100Gbps。意味着可以满足数据中心的安全防火墙的数据吞吐量。

【展示】10G,100G Smart NIC 卡(锐文科技)

支持P4 编程,基于Intel Agilex 推出 200G/400G 智能网卡。虚拟化OvS数据平台卸载。

公司:锐文科技——智能网卡及智能网卡解决方案

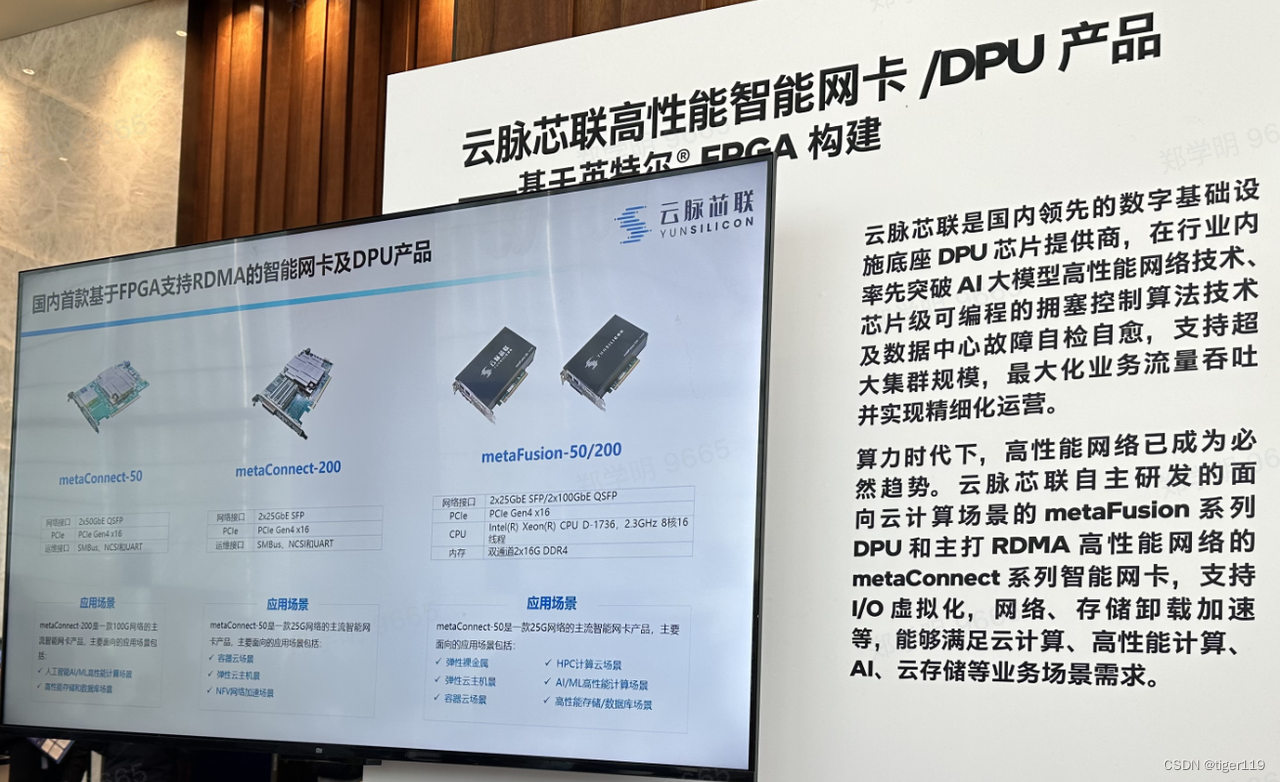

【演示】云脉芯联高性能智能网卡/DPU

【展示】高清IPG网关

这应该是应用到视频会议和其它视频数据高速传输和转换的场景。

IPG网关——协议转换,路由,转发,防火墙安全策略,连接管理……

【展示】800GE IP 演示

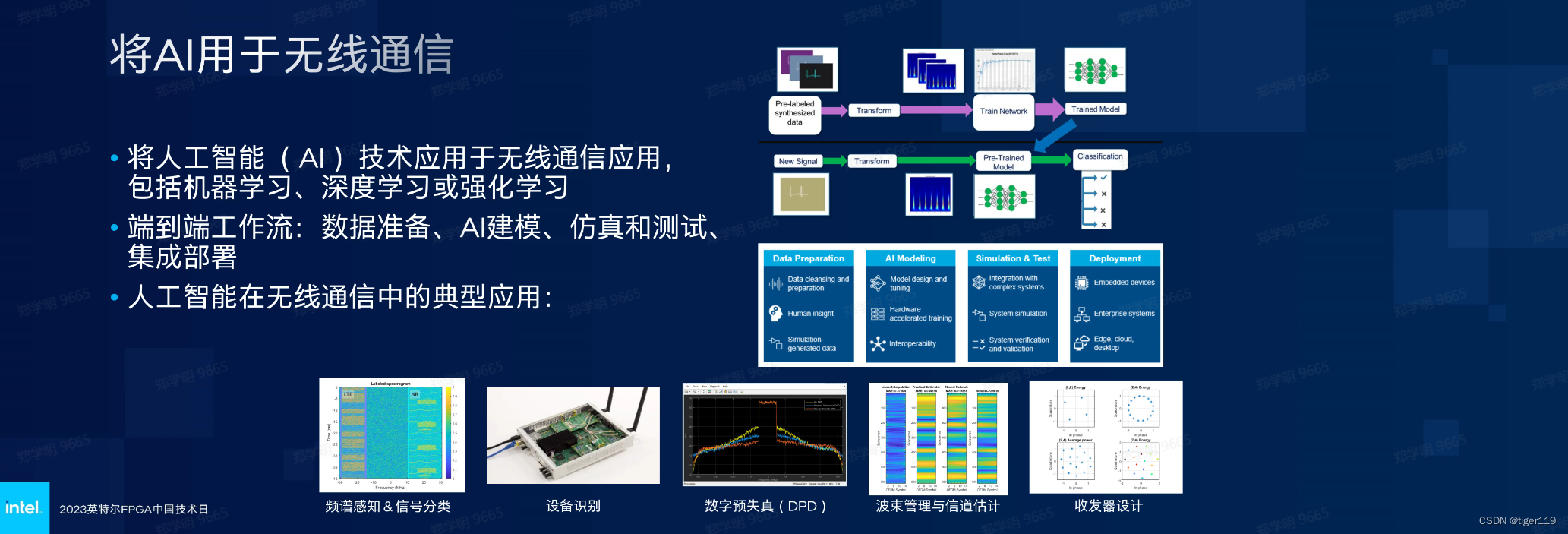

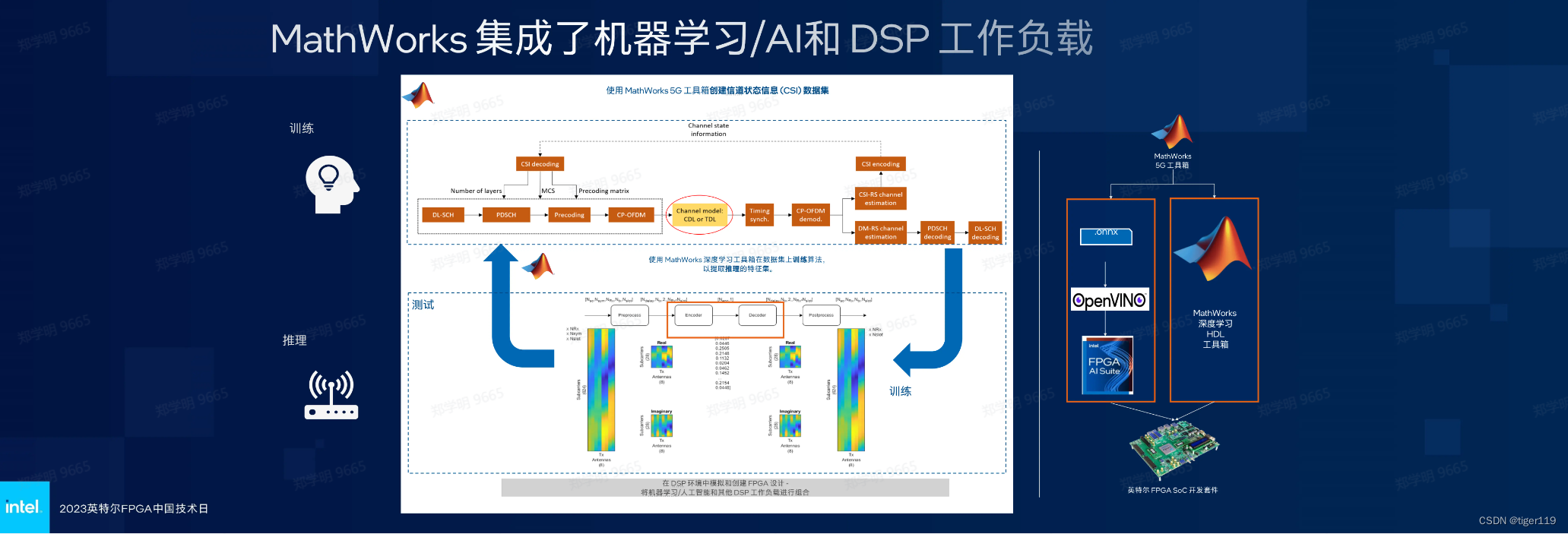

使用AI实现5G RAN CSI 压缩算法

提供端 到端 的工作流—— AI 数据准备,AI建模,仿真,测试,集成/部署

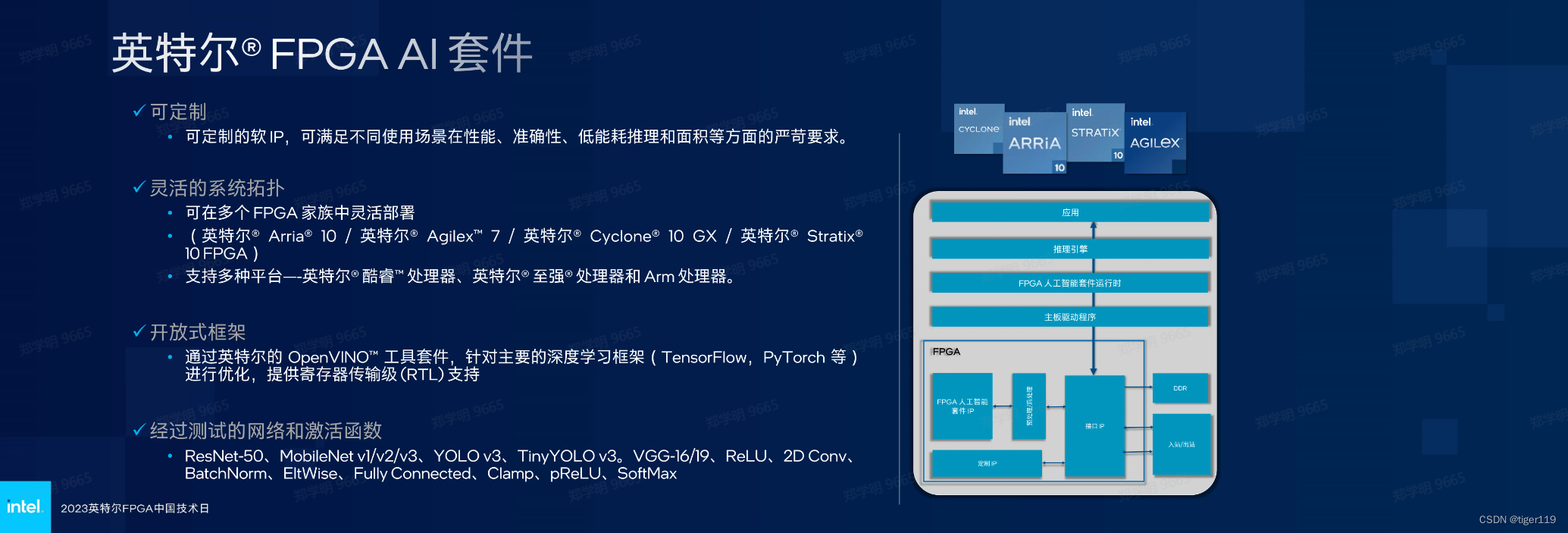

AI套件:

构建——使用已有网络。TensorFlow,Pytorch。

优化——使用OPENVINO进行优化,通用框架,可以异构部署。

部署——可以要求资源限制,生成IP,使用 Quartus进行集成。(DSP Builder也是可以进行预处理,与AI环境进行集成)(也可以部署到CPU上)

可以定制IP(灵活)。

可支持多款FPGA的系列。

开放式框架——支持深度学习框,可进行优化,提供RTL支持。

训练—— 解码, 信道模型,CSI编码 闭环支持。

除了OpenVINO,还可以使用 MathWorks 进行生成和部署。

Mathwork的流程:

提供了IP核(实现了一些基本功能)

基于IP进行简单几行代码的编程(如下)

软件与解决方案分论坛

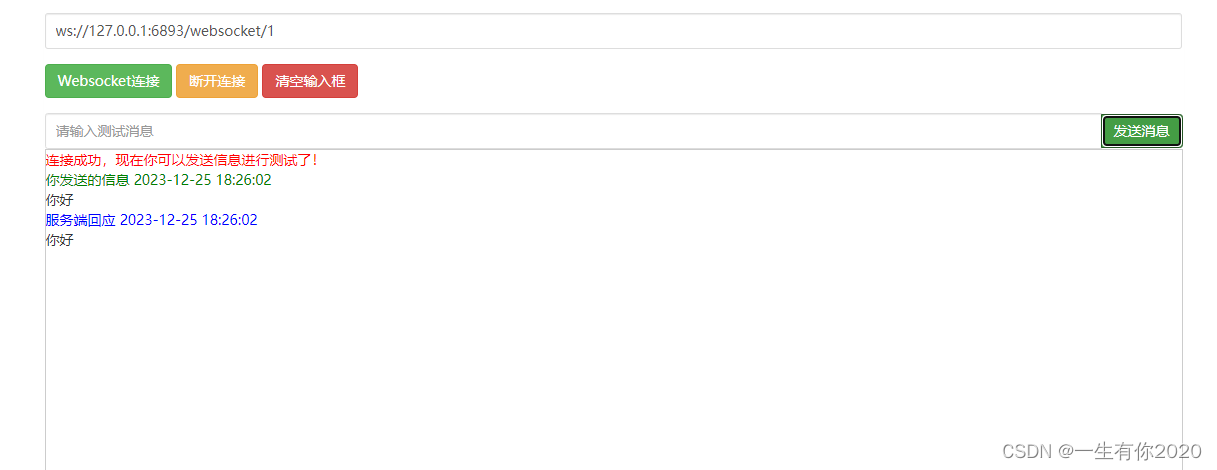

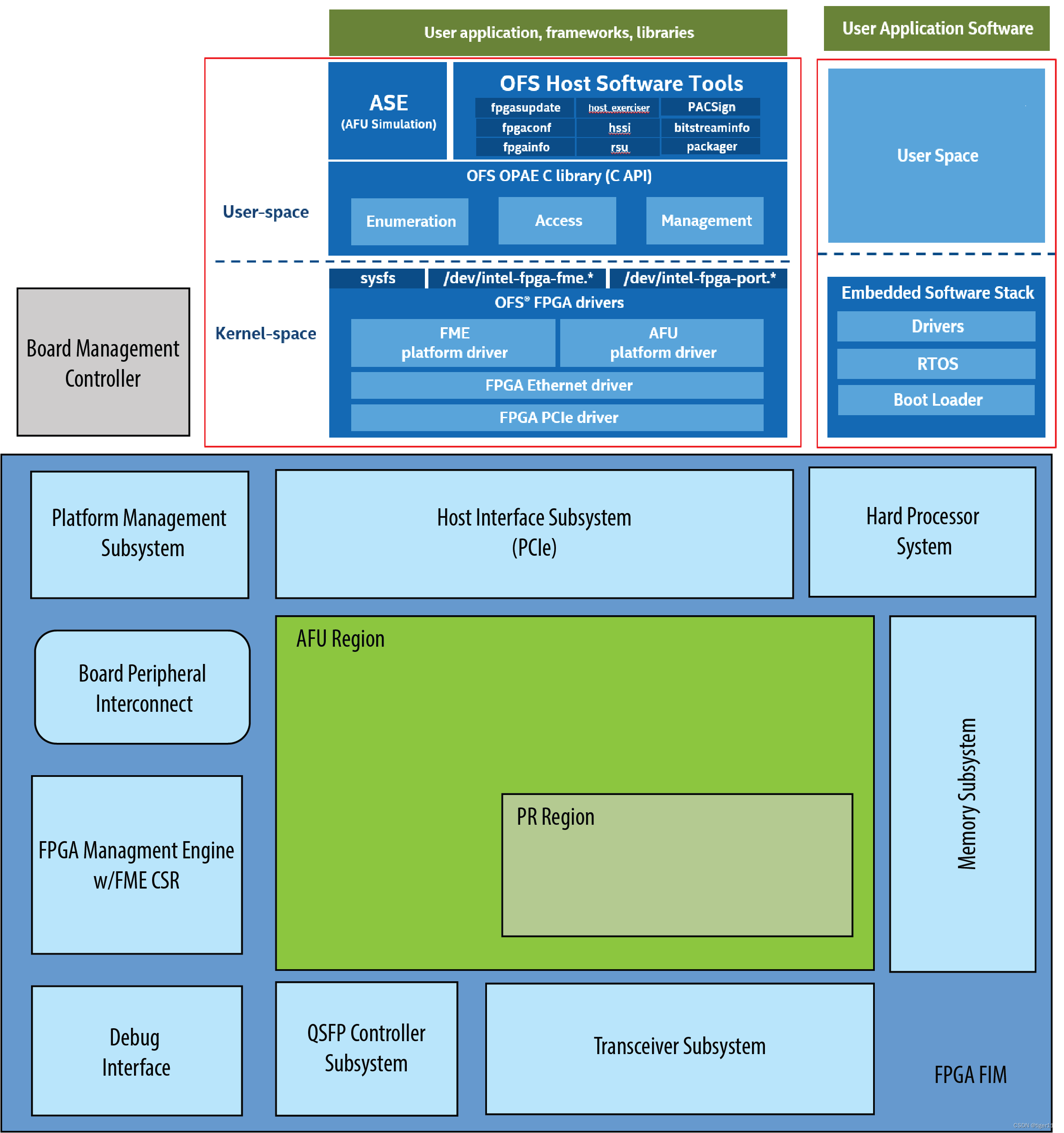

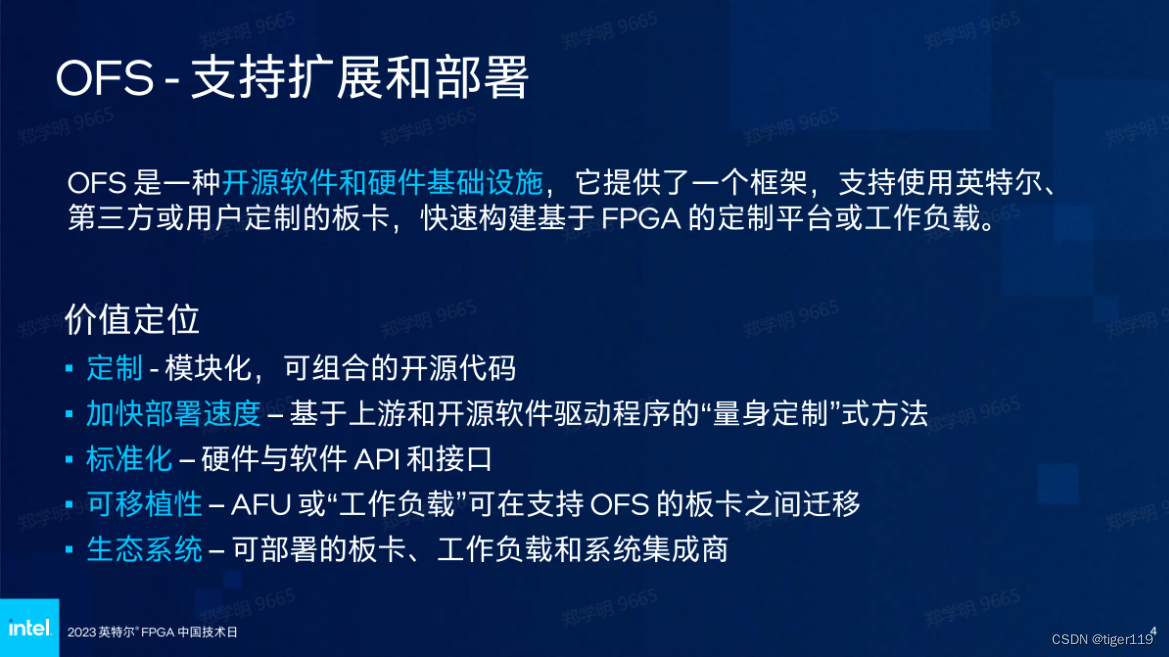

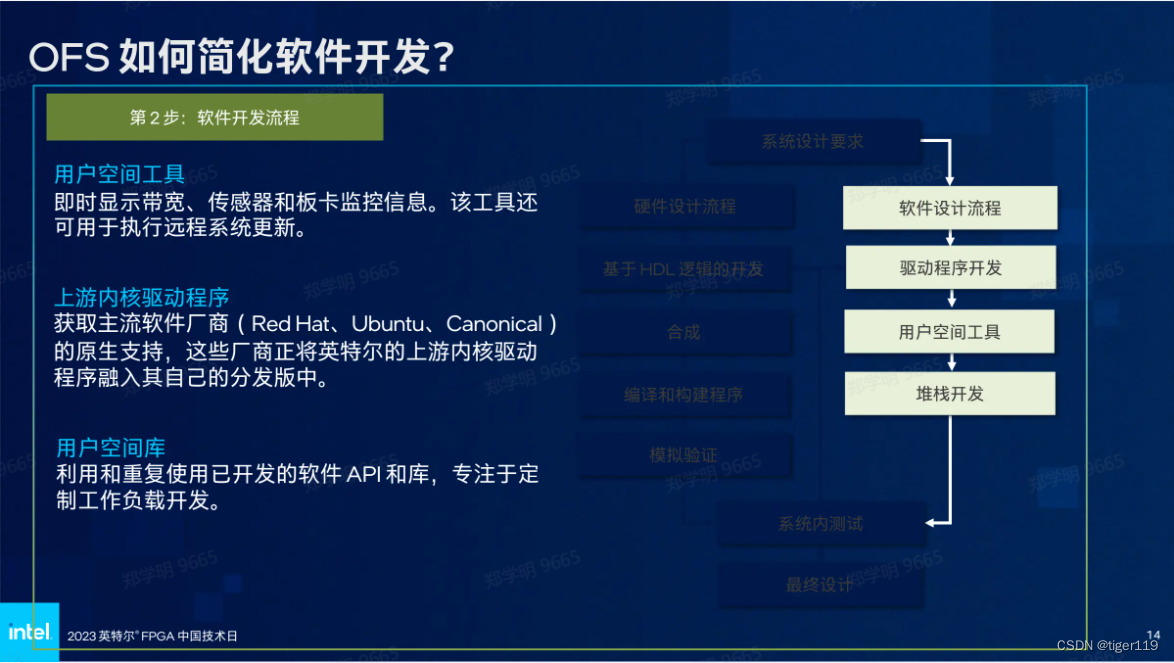

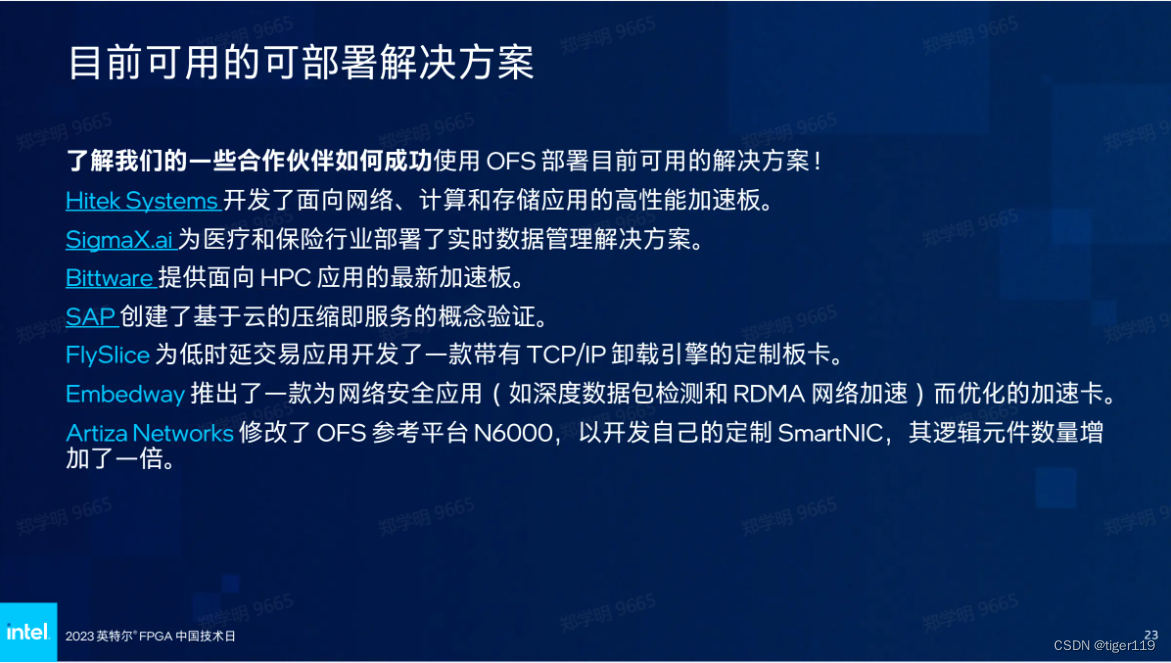

OFS 与 OneAPI 助力加速FPGA应用开发

OFS是什么?是Intel开源的FPGA开发平台。github地址:https://github.com/ofs

支持的硬件除了Intel的芯片,还有一些。并且支持多家的开发板。

硬件开发——RTL编写,仿真,

软件开发——驱动开发。

软硬件协同开发——

这里注意,对OSV操作系统原生支持,指的是intel将驱动的支持直接内置入了常见的操作系统 。用户不需要做相应的驱动开发。

模块化——DDR,以太网,PCIe,HPS,这些都是可选的,可组合的模块。可以构建自已的子系统。不需要对驱动做什么改动。API接口也不需要改动。

从一个器件移到另一个器件,没有什么需要做的工作。

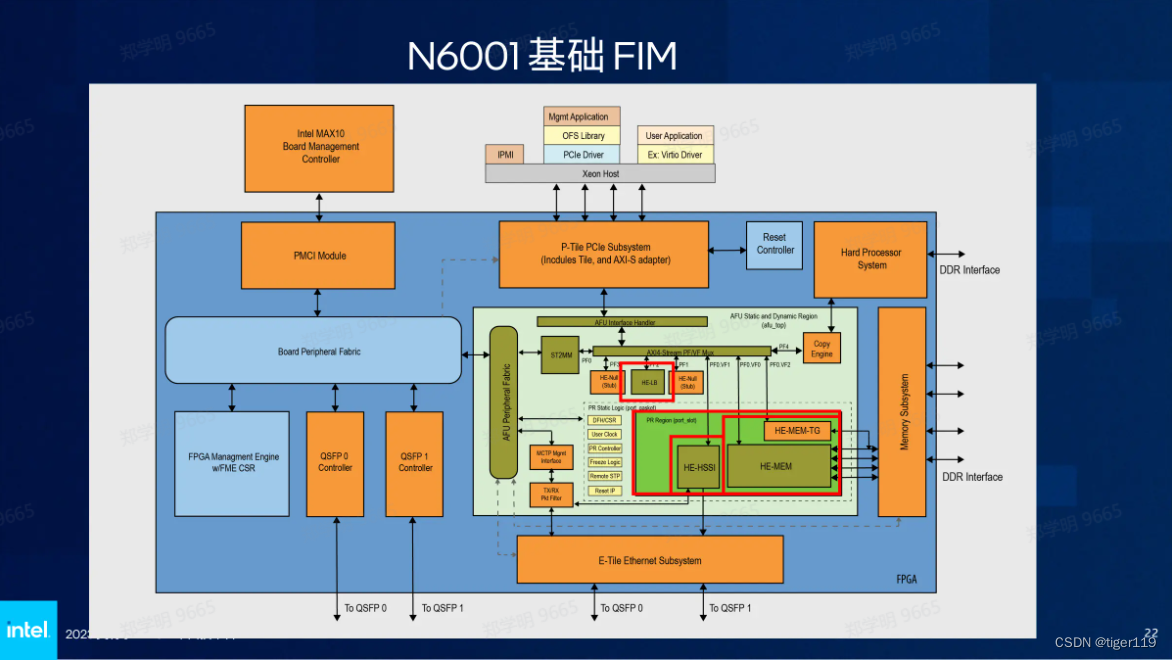

硬件——AFU(应用逻辑),FIM(接口管理,网表文件,时钟管理,接口管理),BMC(远程加载),ASP(在OFS框架下使用OneAPI)

OPAE库——(Open Programmable Acceleration Engine) 库提供了一组抽象的高级API,使得开发者可以更容易地在Intel FPGA上实现和部署加速工作负载,特别是在数据中心环境中

OFS提供了UVM的支持。

第一步:选择硬件平台/器件(根据需求)

第二步:硬件开发

可以定制 FIM——量身定制。

AFU——PR过程

测试程序——主机测试

oneAPI——可以使能相应的工具套件。

使用标准的AIX接口。

第三步:软件开发

内核 驱动程序——OS支持,将驱动直接内置。

用户工具——显示FPGA信息,还可以远程更新

用户空间库——API 和库。

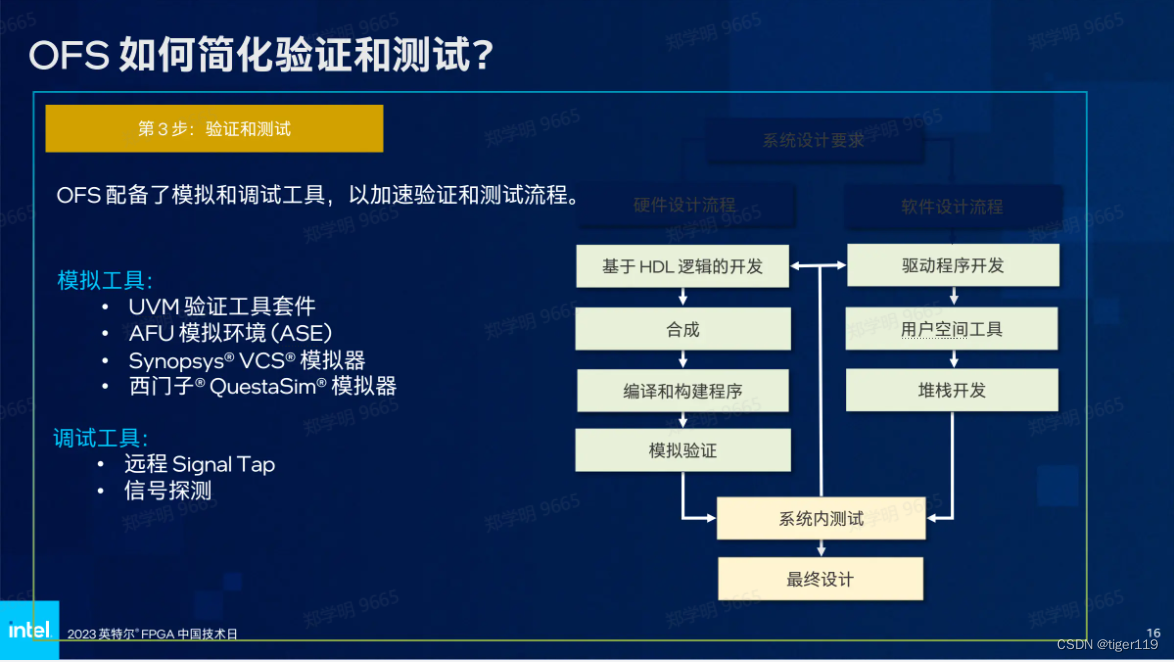

第四步:验证和测试

UVM验证——UVM验证测试工具 (仿真 VCS)

AFU模拟环境——软硬件联调

在线调试工具——Signal Tap等……

行业变化——硬件加速器需求越来越多

这是OFS目前的生态——板卡,工作负载(FAAS,数据管理,金融科技……)

1:CPU,GPU,FPGA工具链打通。

2:使用C++ 开发。

3:支持在线调试。

提供一键加速(进行性能调优,这么神奇!)

可以在不同器件间进行切换。

两条开发路径:

一:OFS 参考平台。N6000,Intel推荐

二:三方板卡

OFS:RTL OneAPI: C++ 需要选择合适的路径。

FIM使用——多个子系统 可以配置/组合

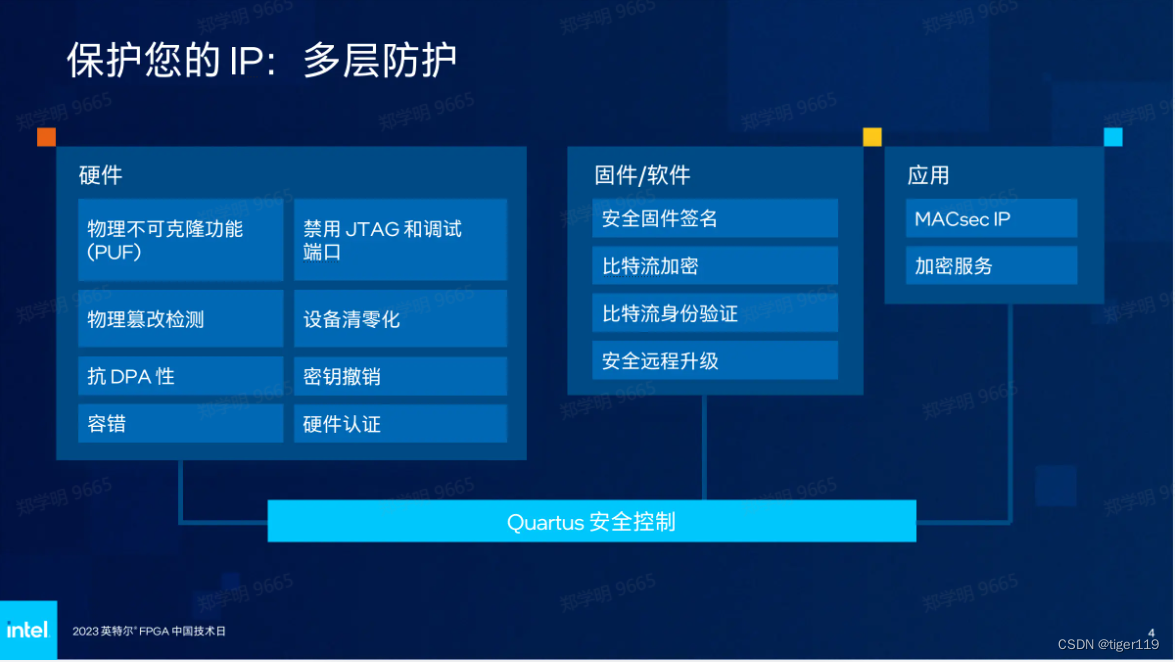

FPGA为系统保驾护航

主要讲信息安全,数据安全。如何对数据进行保护,对抗逆向工程。

实际上Intel提供了很多安全相关的功能,并没有多少人使用,这里想做个推广。

FPGA与数据的关联:chiplet的小芯片架构,导致 内置的IP 的逻辑量越来越大。

SDM——硬核来管理配置,保证安全,相当于一个MCU

PUF——物理不可克隆,实际上是通过物理特性不同来生成唯一标识。

高级BKP——黑钥分配,一种密钥分发机制。具体不清楚。

MACsecIP ——一种新的网络安全协议。

三类防护:

硬件——

软件——主要是添加SDM。签名,加密,身份验证。对Bit流进行签名和验证。

应用——通用的加密服务

SDM:3个MCU做三重表决验证。(安全和配置中心)

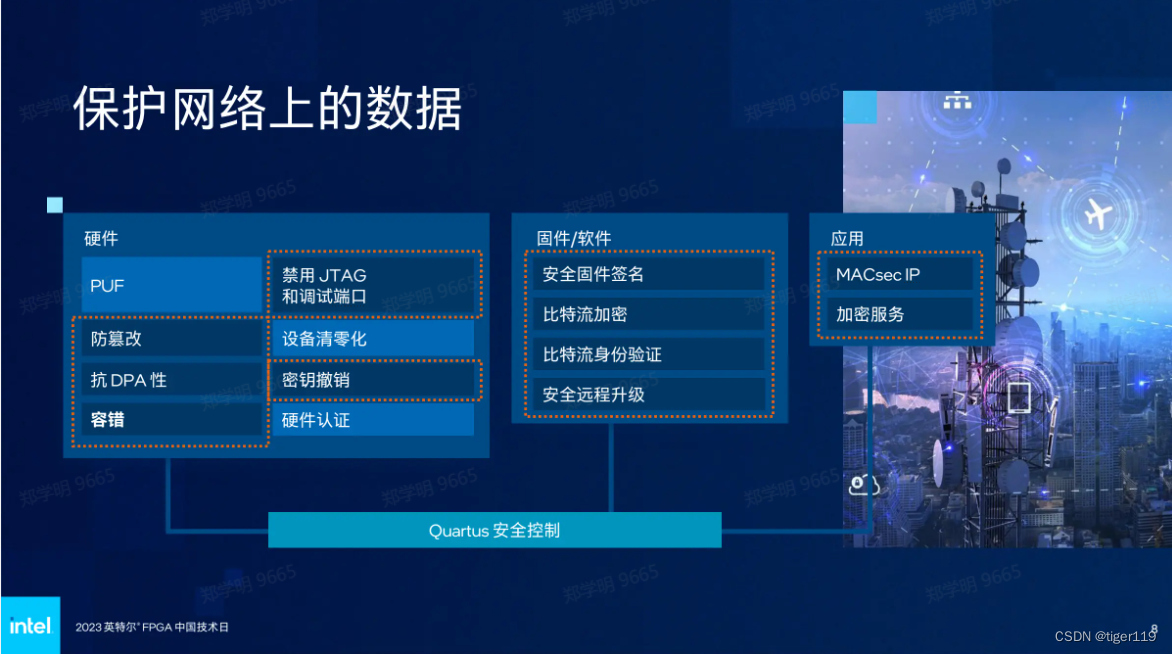

云端 ——偏应用的保护(数据中心,更在意软件的防护)

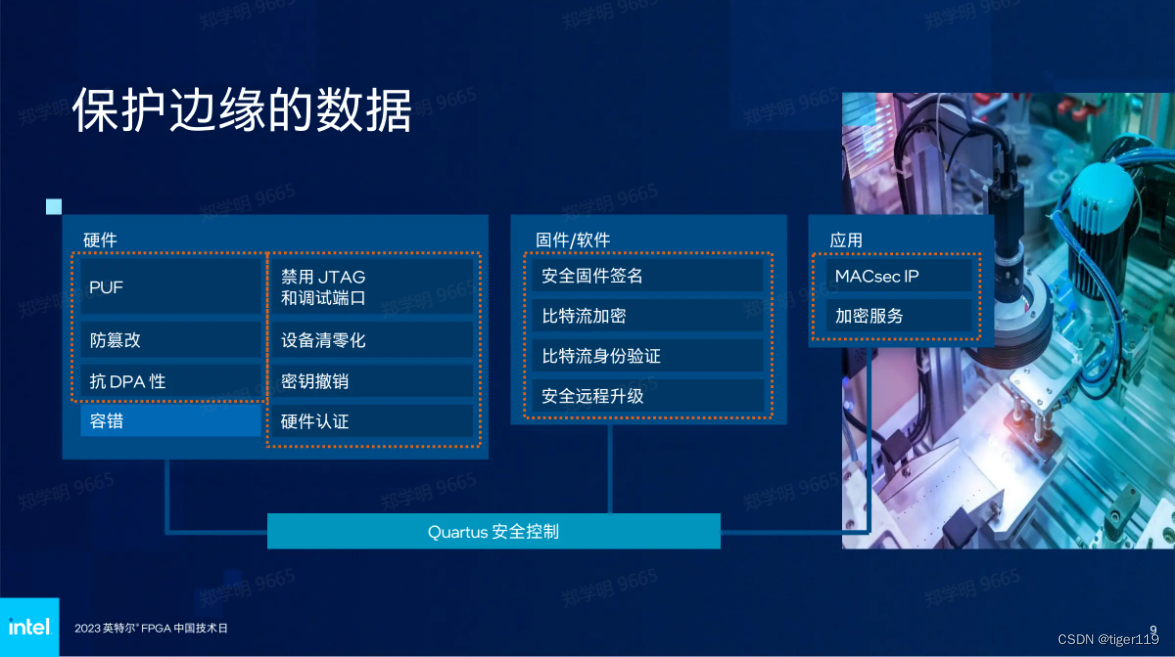

网络——数据传输

边缘数据——更靠近传感器,物联网设备。需要更多的硬件的防护。

从应用的角度,主要的处理方案是:签名 + 身份验证!!!!

随着技术的发展,对安全的影响——AI,量子计算……

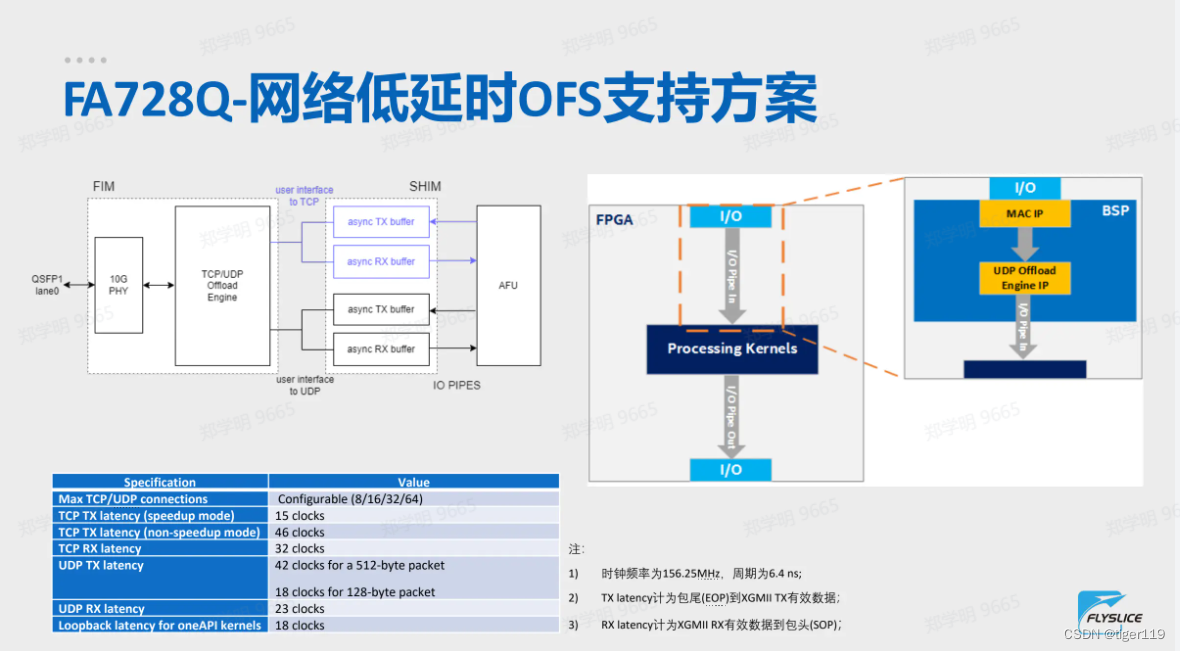

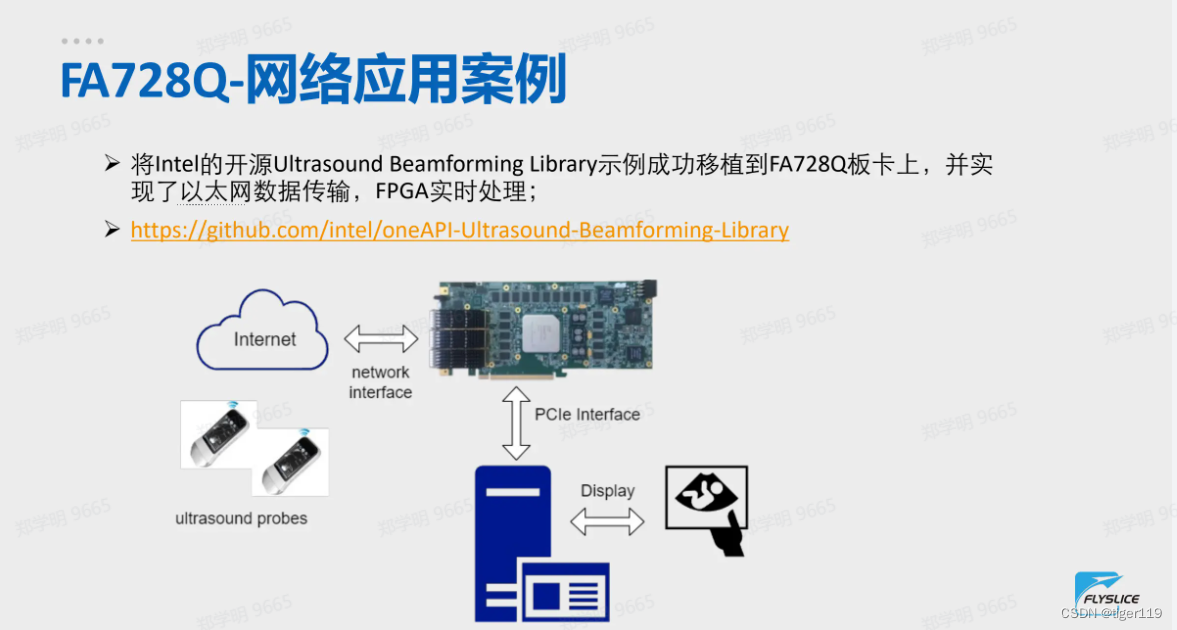

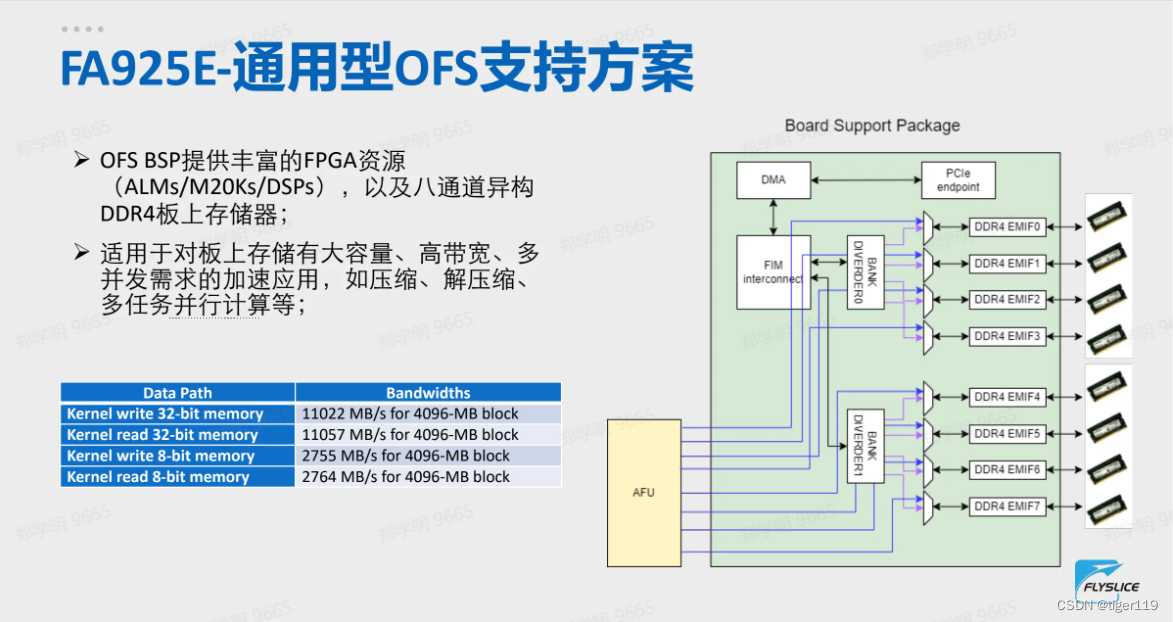

加速卡与OFS解决方案

这又是一个广告(菲数科技)——异构加速应用方案供应商(FPGA的解决方案)

专注于OpenCL,2019年开始试用OFS,

为intel打广告(提供了更多的API,和板卡管理,驱动更完善)

提供了更多的模块(封装了IP,提供了更多的管理模块)

广告开始:菲数提供的板卡。支持openCL的板卡

可替换相应的Intel停产的板卡

适合于通用应用。

这是定制化的方案(如:金融业的需求,低延时)

添加了开源算法

最新版卡,基于最新Agilex系列

DDR是异构的。

支持PCIe5.0,CXL

【展示】Wiswave LSA 1.0

本地存储加速解决方案——PCIe4.0X16,虑拟盘,云原生加密。

芯潮流——珠海公司,专注于高速 SerDes IP 研发,授权及芯片定制化服务,面向数据中心,网络,汽车电子和特联网。

【展示】菲数科技中高端FPGA加速卡

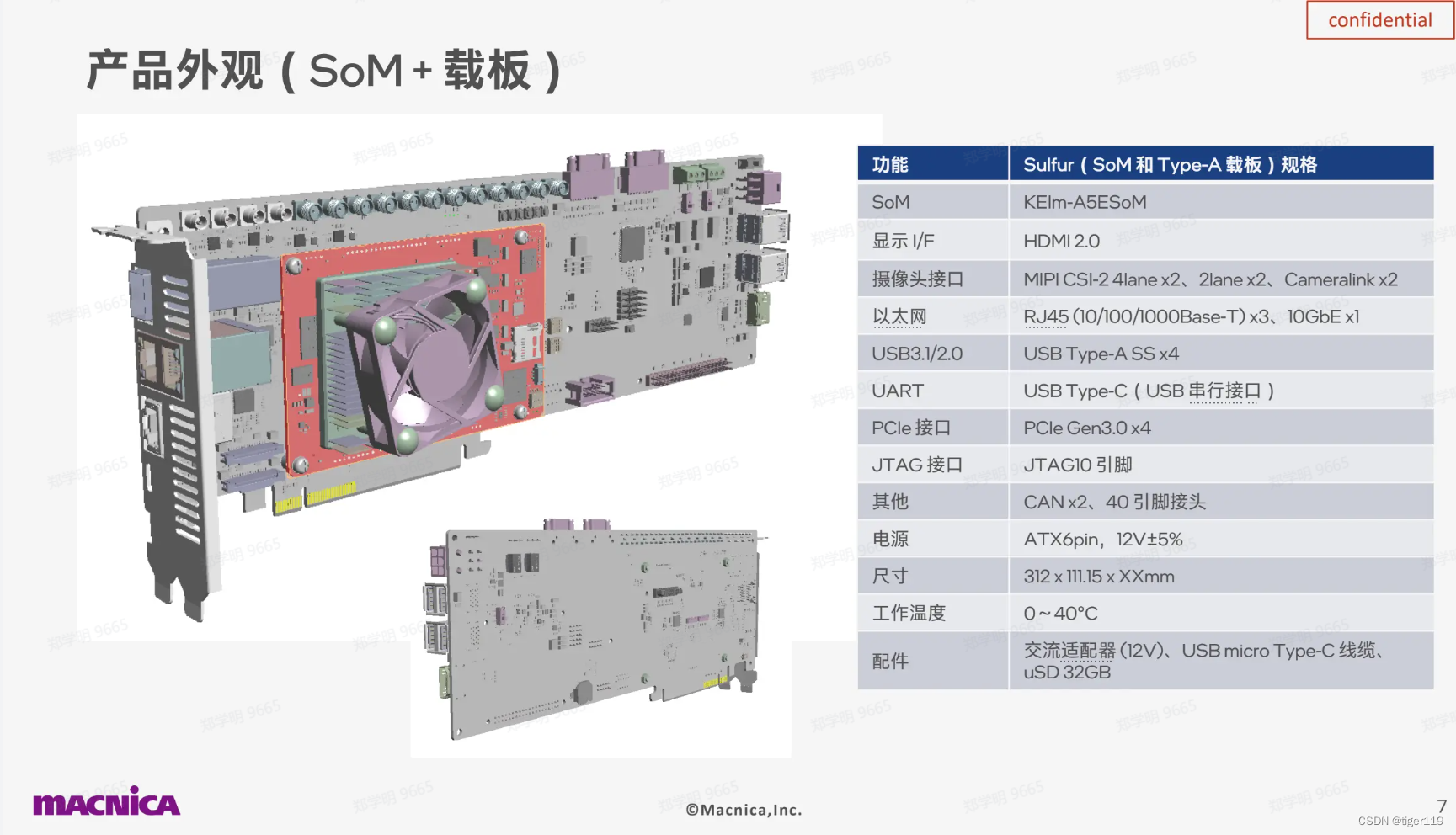

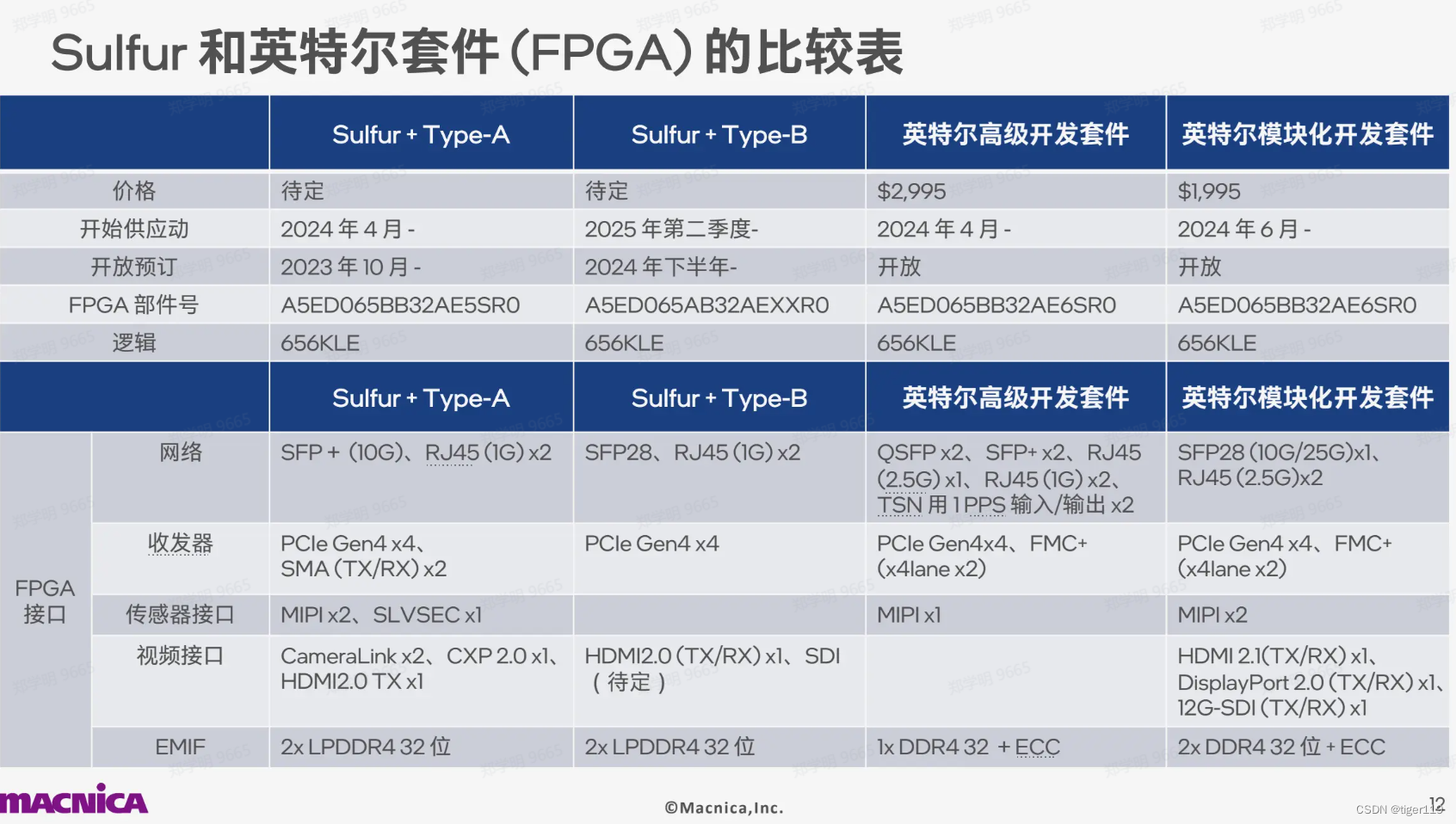

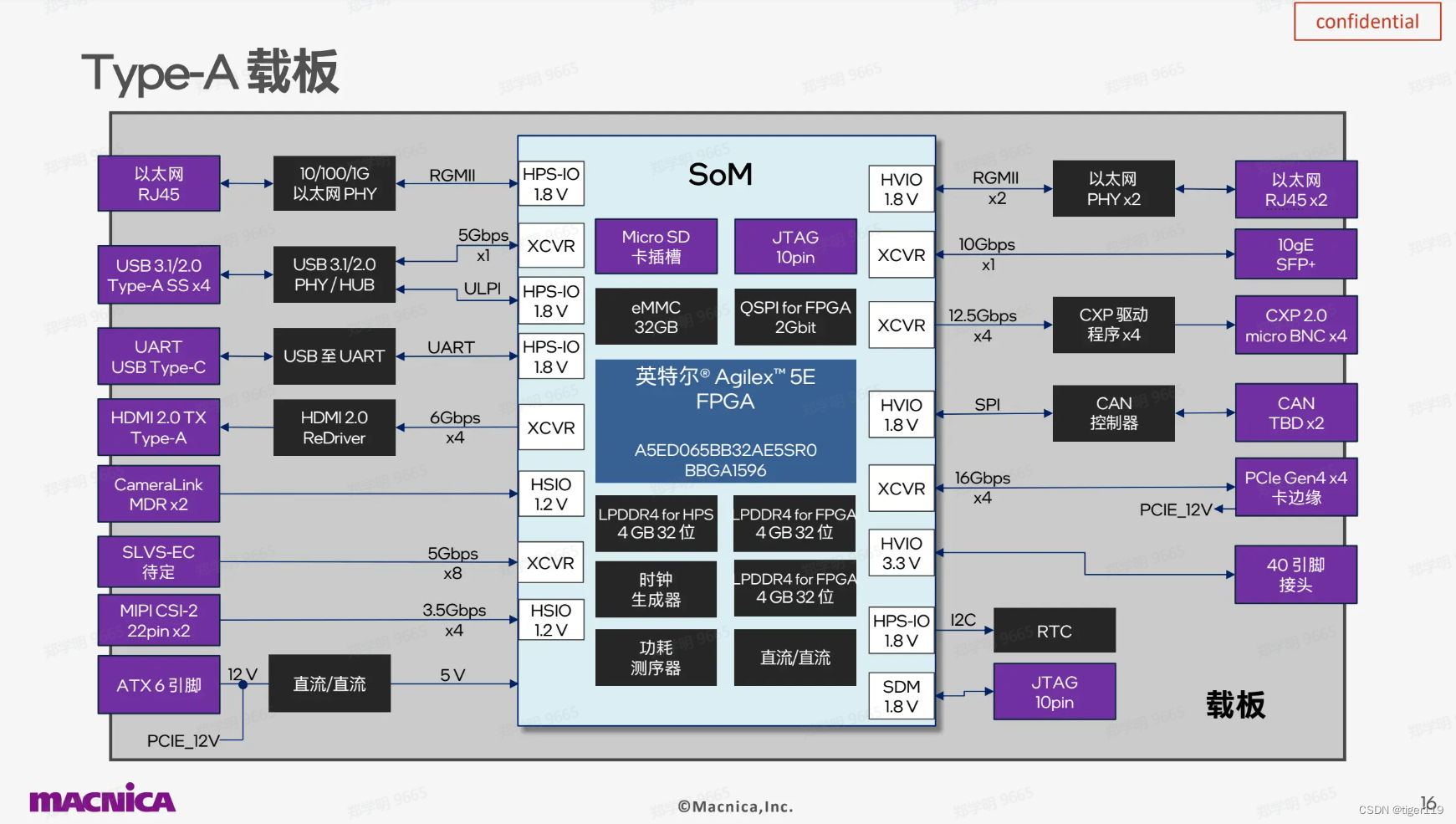

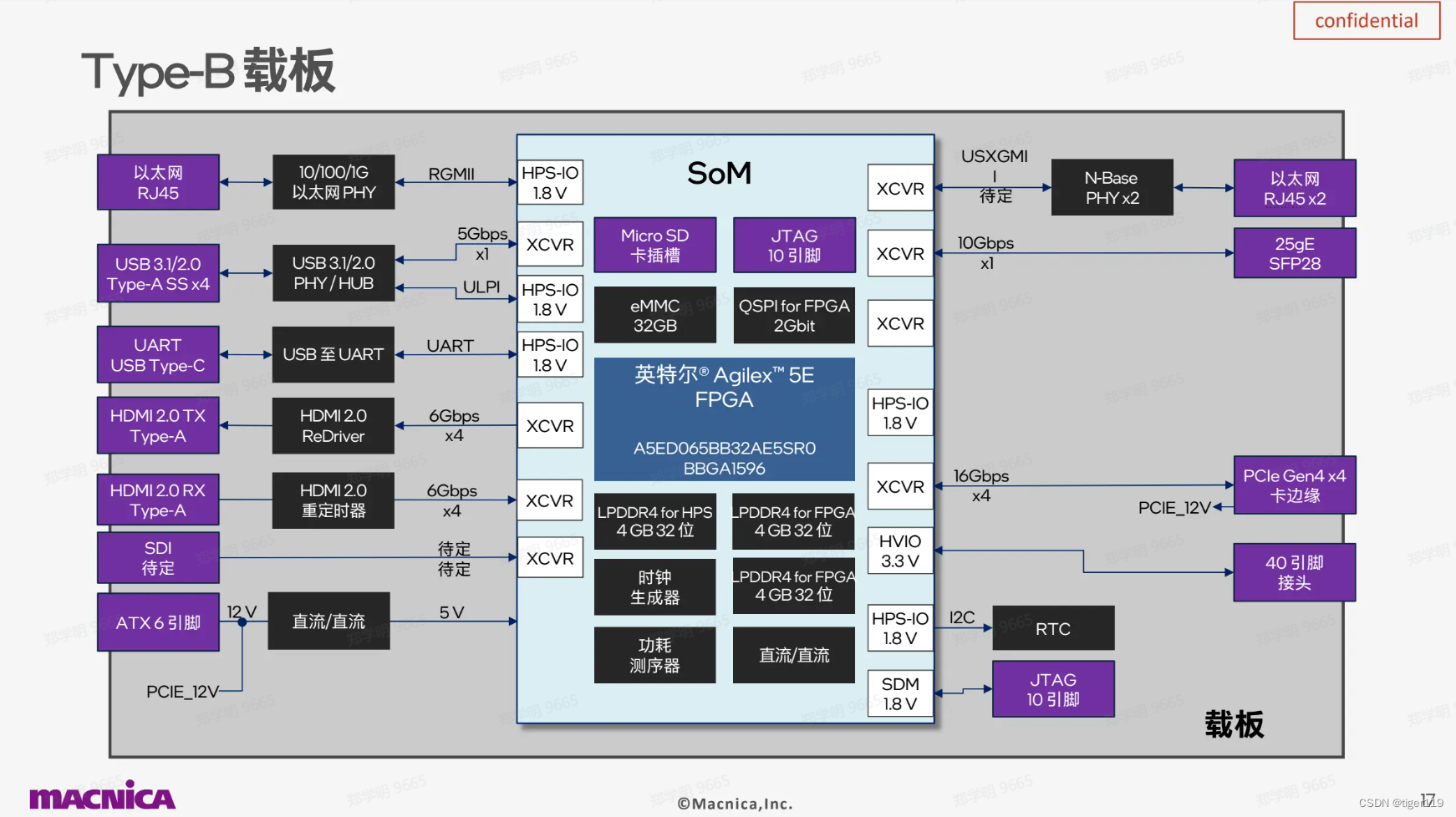

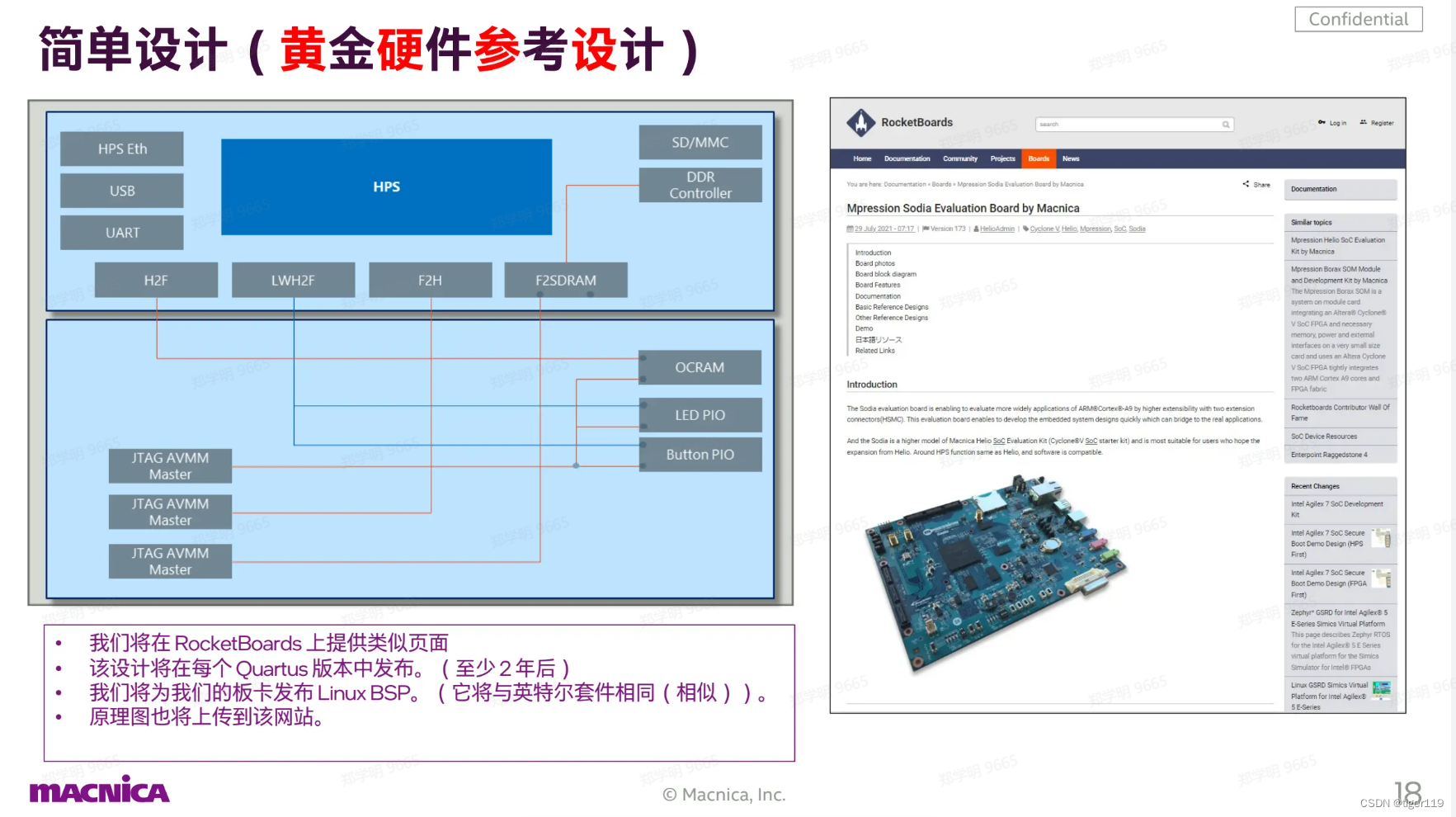

Agilex 5 SOM卡

这实际上是一个大广告,是一个新产品。(骏荣科技)

5 属于中端产品,模块产品主要是使用5系列。

E系列特点——功耗优化。arm用到了A76,支持MIPI接口。

特点:功耗低,性能提升。接口灵活,A55,A76ARM, INTEL 7 制程

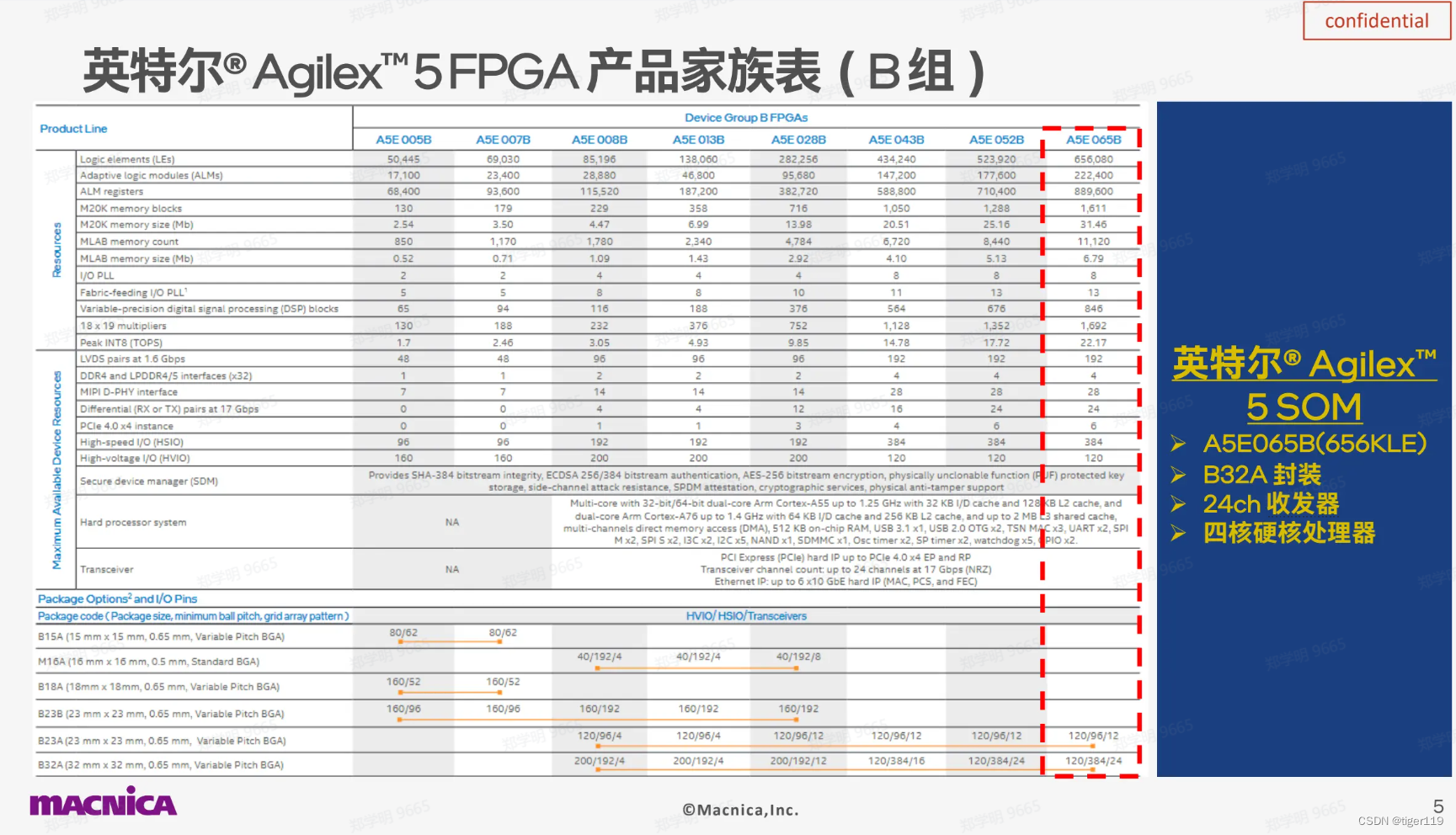

使用656K逻辑容量的B系列,封装 32 * 32

PCIe的卡

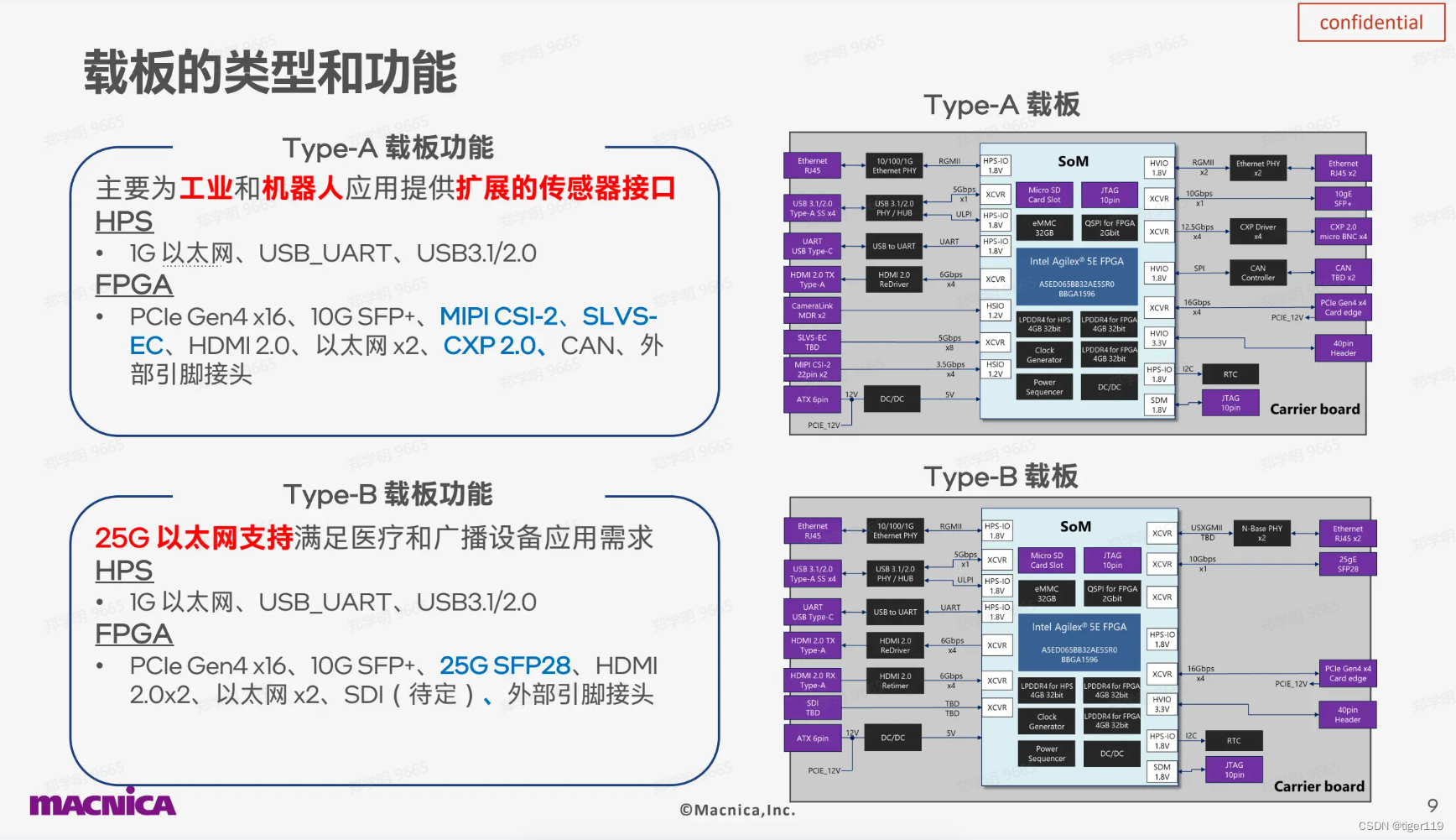

TypeB——面向中高端 。

A——工业,机器人应用 B——光口提升,图像处理

对应intel的芯片配置

支持TSN网络。

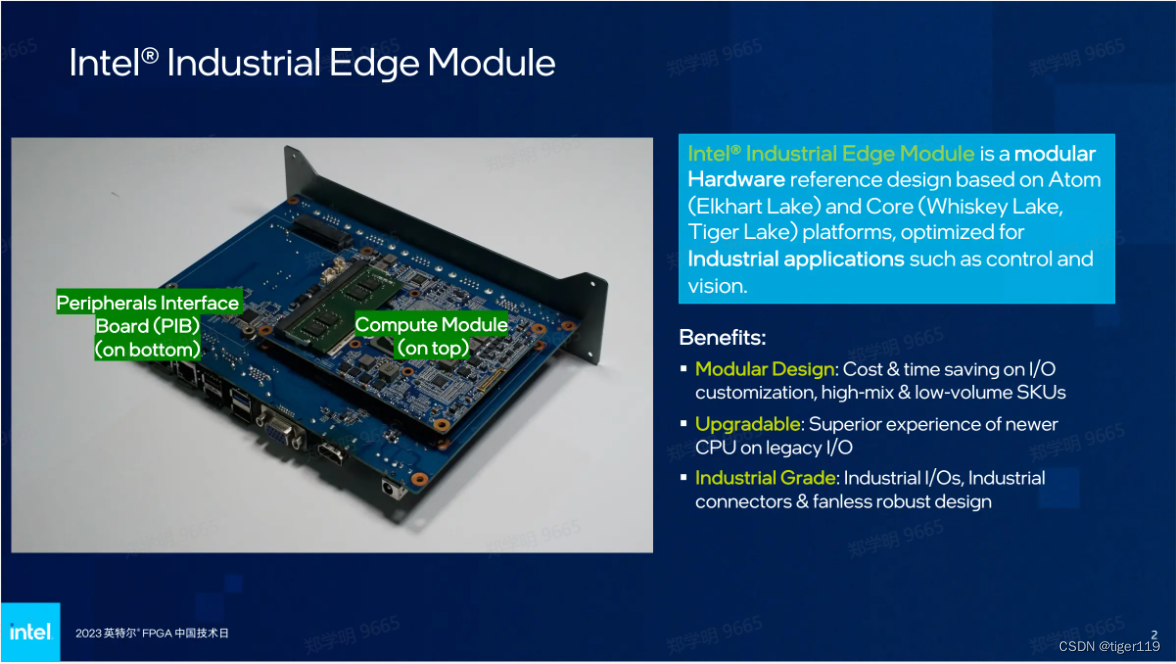

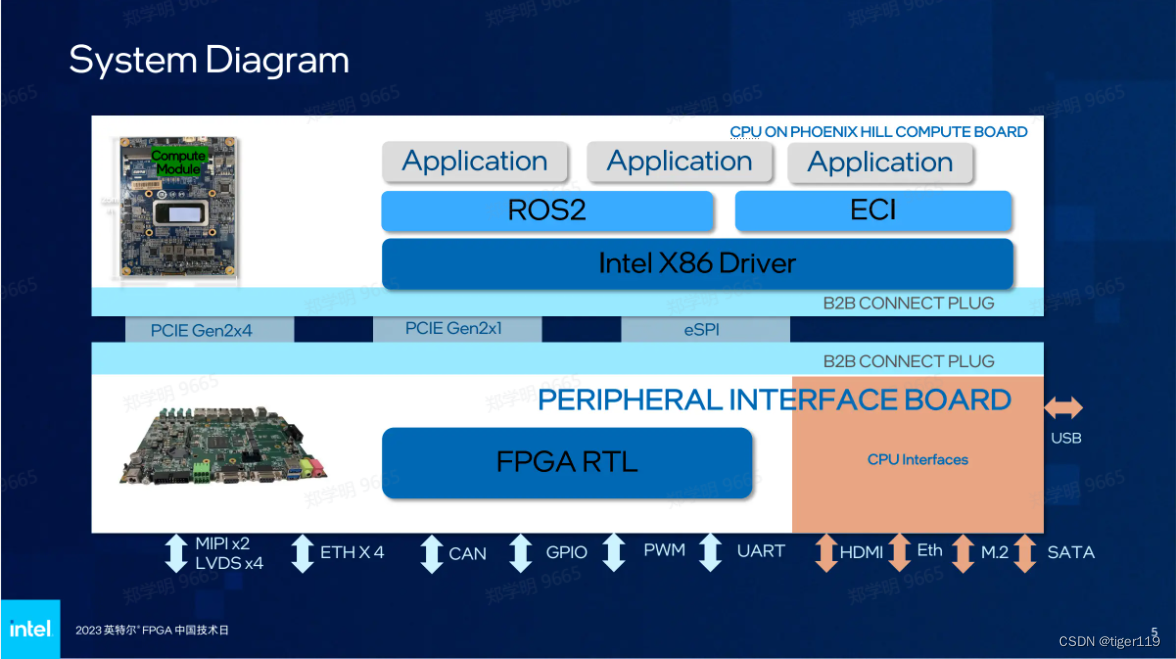

X86+FPGA平台实现传感器融合

工业底版,有X86的片子,有PCIe接口。客户可以自定义,作为工控机的产品,方便定制。

4个LVDS摄像头(可以长线),还有MIPI,有以太网(4组),……

CPU Card在右面,有大量的接口。

适合工业使用。

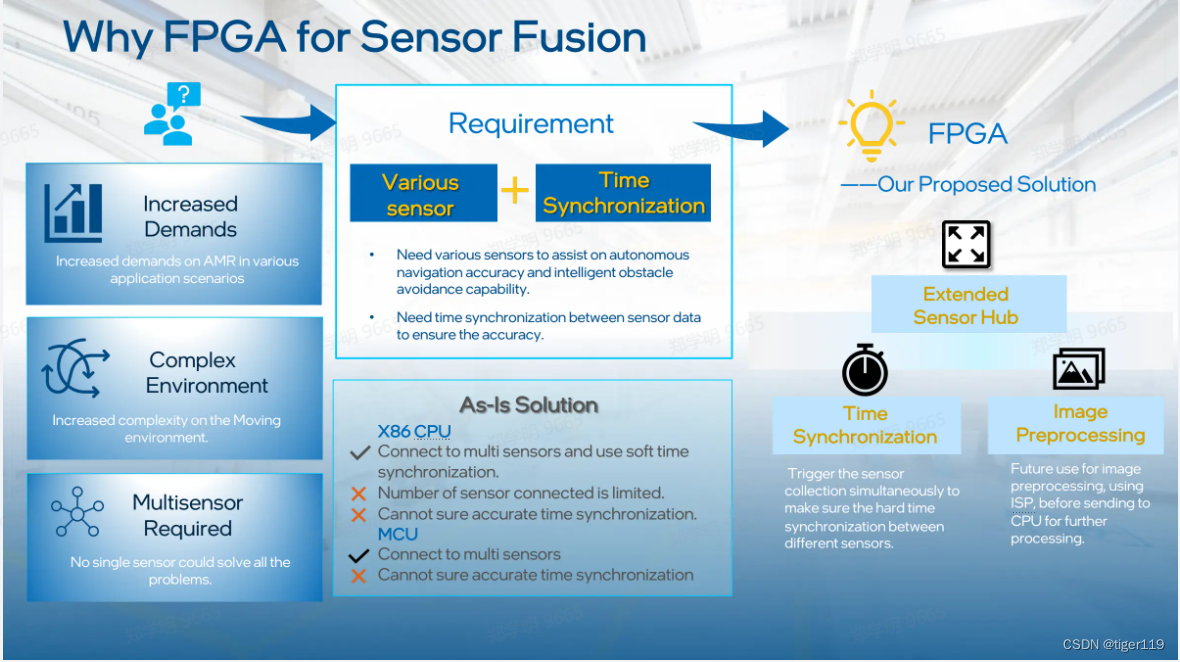

两者结合,FPGA captue data,传给CPU处理。如下是一个感知的应用,然后还可以再控制。

一个小型的中控系统,可以认为是边缘,也可以认为是端。

机器人,工业互联网,机器视觉(AI),控制

感知(取代或增强激光雷达),可以了解细节(通过照片),需要强时间同步保证激光雷达数据和照片数据关联(可以使用)。变成超级传感器,需要处理最好的相位差(10us以下,符合自动驾驶的需求)。

数据上行到PC

FPGA工作——UDP解包(激光雷达数据),控制像机进行拍照(只能由FPGA来指令,10us延时),做到强时间同步。

传送带时间戳的数据,软件进行隔离的处理。

这是一个演示的例子。

差不多大会的内容就这么多了,还是有一定参考价值,当然,我这个整理很乱,也只能做一下参考。

总的来说,国内的FPGA还处于很初级的阶段,也就是纯硬件开发环节,整体水平可能差了5-10年,追赶需要多久,不好说。有很多东西,需要积累,非朝夕之功。但有些错误的路线,我们确实也可以避免,可能弯道超车。通过对 Intel 和 AMD 产品的详细/认真了解。就拿AI来说,Xilinx的 VItis AI 看似红红火火,但其实没啥应用,可以说业绩惨淡,这背后一定是有原因的,可能是技术不成熟,可能是不接地气(和应用没有深入集成),国内的产品在涉足这一块时,应该要认真思考一下,这一定是有机会的。