This standard defines power supply voltage range, dc interface, switching parameter and overshoot/undershoot for high speed low voltage swing terminated NMOS driver family digital circuits with 0.6V supply. The specifications in this standard represent a minimum set of interface specifications for low voltage terminated circuits. Item 180.24.

今天和大家交流交流LPDDR4相比于LPDDR3的差异,感兴趣的机油不妨和楼主一同来学习一下哦~~

Die的设计改进

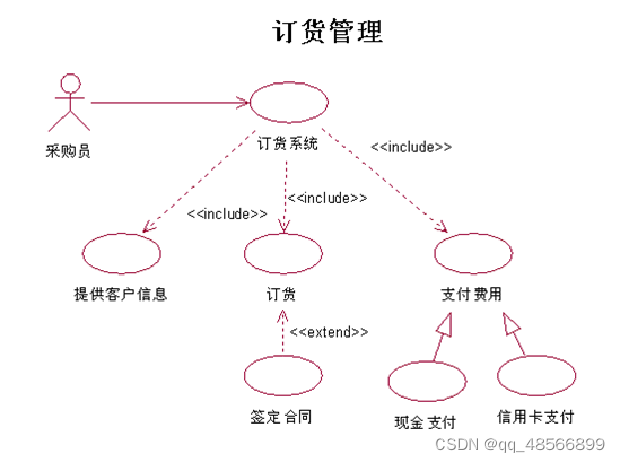

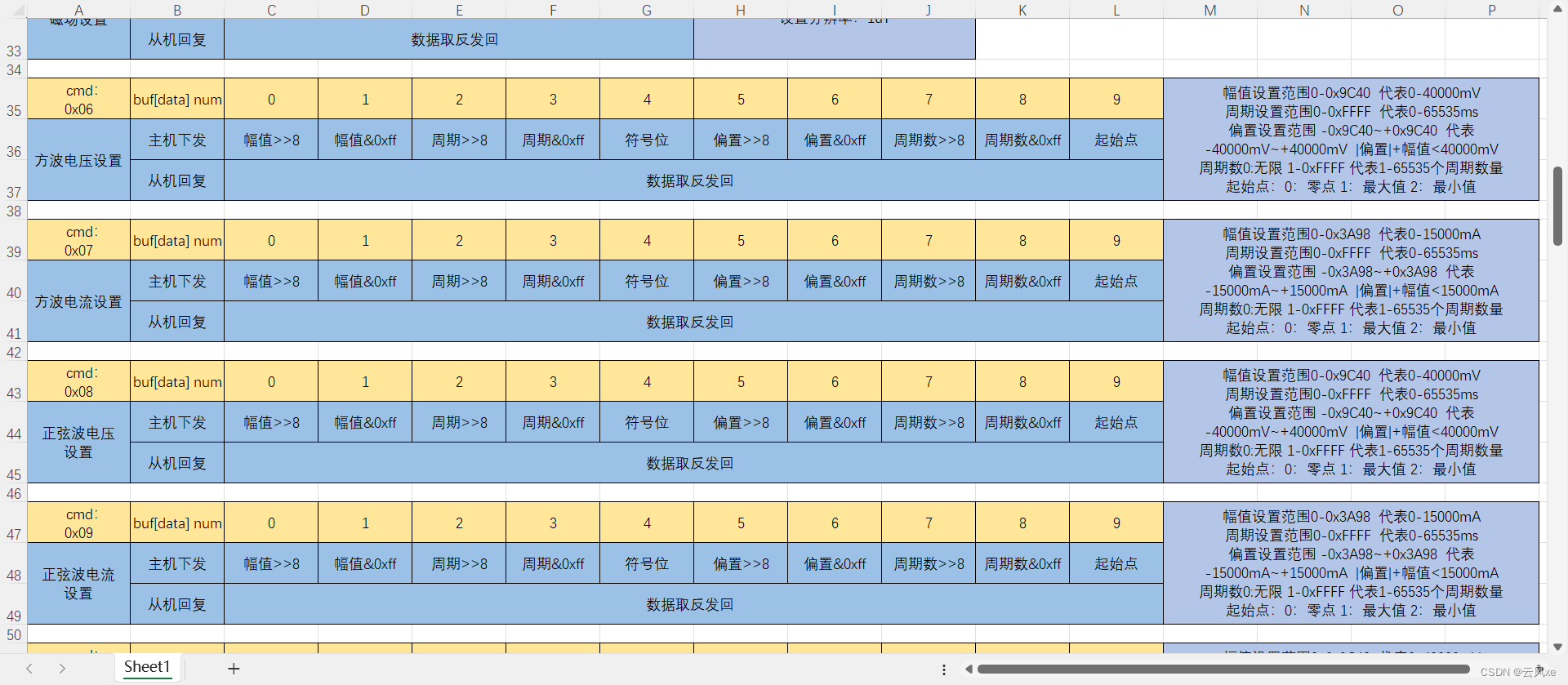

LPDDR4的本质还是DRAM,其基本的存储单元电容井加mos开关的方式并未发生变化。为了获取更快的读写速度,仅仅提升外部的总线吞吐能力是不行的,LPDDR4在die的设计上做了改进优化,来配合外部总线的速度提升。如下是对比LPDDR3的设计方式:

可以看到,die的设计方式已经由之前的单Channel演进为双Channel,并且DQ信号和CA信号的设计位置也做了改进。

更改为双Channel后,同时把CA信号更贴近的置于对应的DQ信号,减少芯片内的不同设计走线长度造成的时延差异。双通道架构缩短了数据信号从存储器阵列到I/O的传送距离,由于存储器上的大部分面积被存储器阵列所占据,翻倍扩大接口面积对总体尺寸的影响微乎其微。

每个channel都有自己独有的CA信号,可以进行并行的操作。所以外部总线速度的提升,内部是主要是依靠更短的时延和更多的并行操作来进行消化。

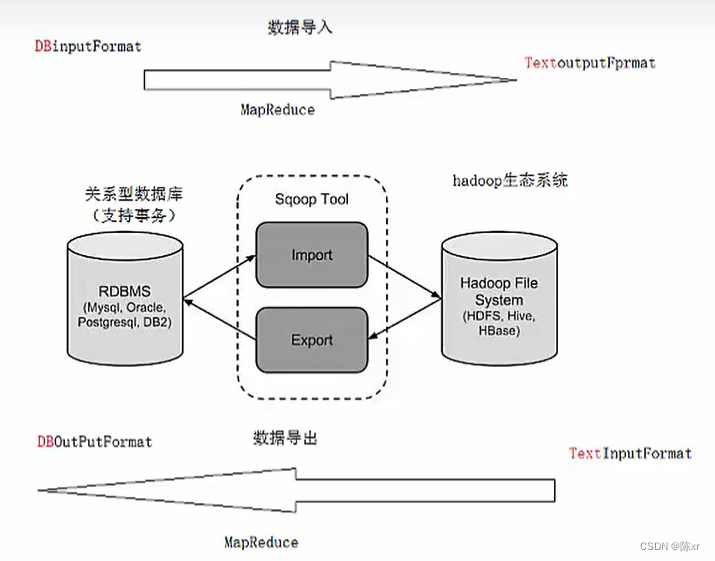

LVSTL的低功耗接口设计

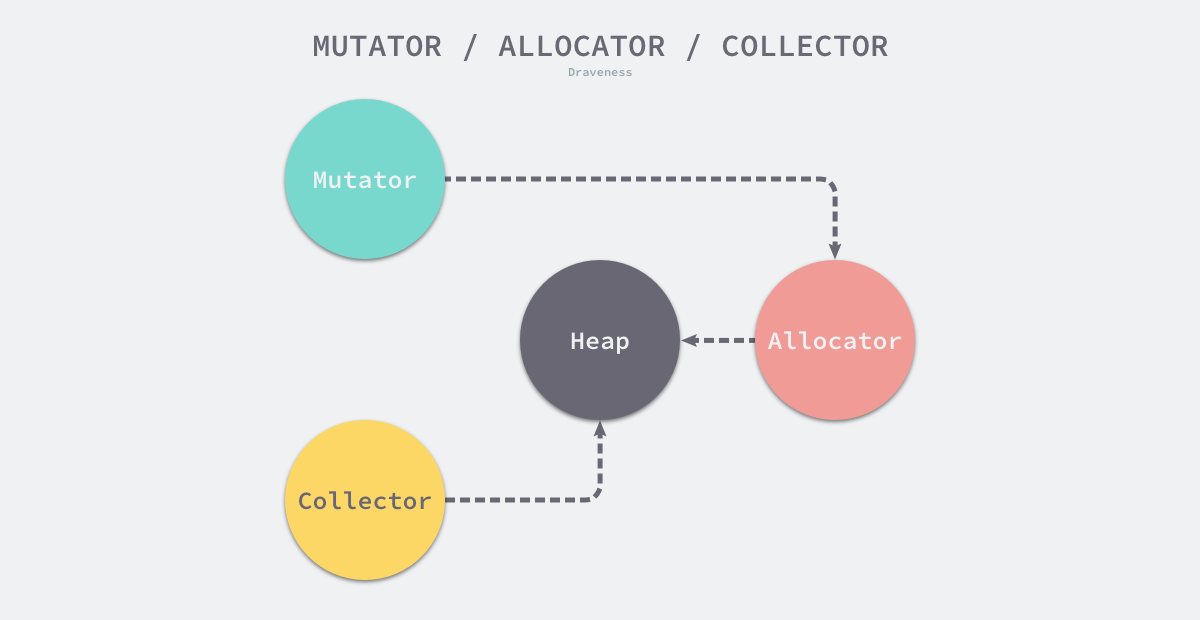

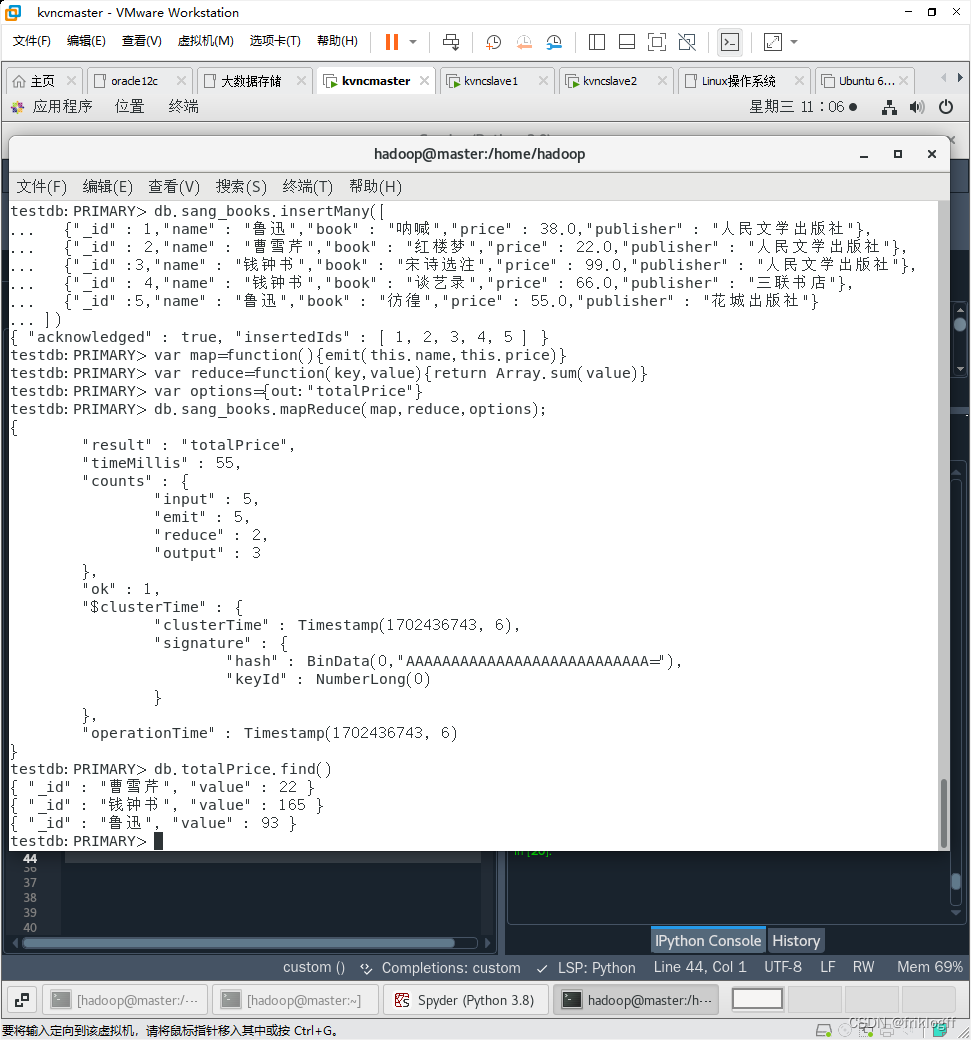

接口扩展到更高的频率将消耗更多的电量,LPDDR4的I/O接口信号发送方式做出重大改变,采用低电压摆动-终止逻辑(LVSTL)方式。LVSTL(Low Voltage Small signal Terminated level), 低电压摆幅终端逻辑。

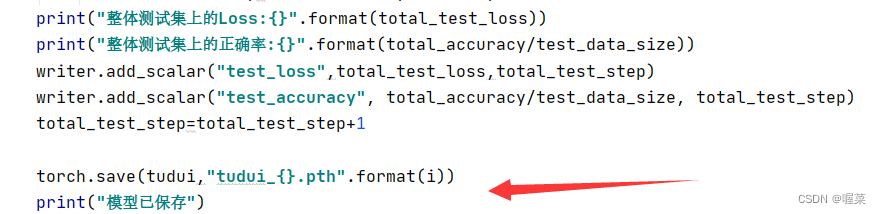

其内部的原理如下图

它由两个NMOS构成了上下拉,信号的摆动电压幅度是可编程控制的,一般控制在VDDQ/2.5~VDDQ/3之间。

下图是与LPDDR3的接口电平的一个对比情况

这个接口还有一个好处,就是在idle状态下,不需要直流电平,所以也不会有电源的消耗。

基于这个LVSTL接口的这两个优点,其接口功耗会明显下降。根据Memory厂家的测试,3.2Gbps的LPDDR4的接口功耗,相当于1.6Gbps的LPDDR3接口功耗,也就是说它的接口功耗下降了一半。

另外操作电压从前代的1.2伏降低到了1.1伏。这样也降低了芯片的工作功耗。

数据翻转功能

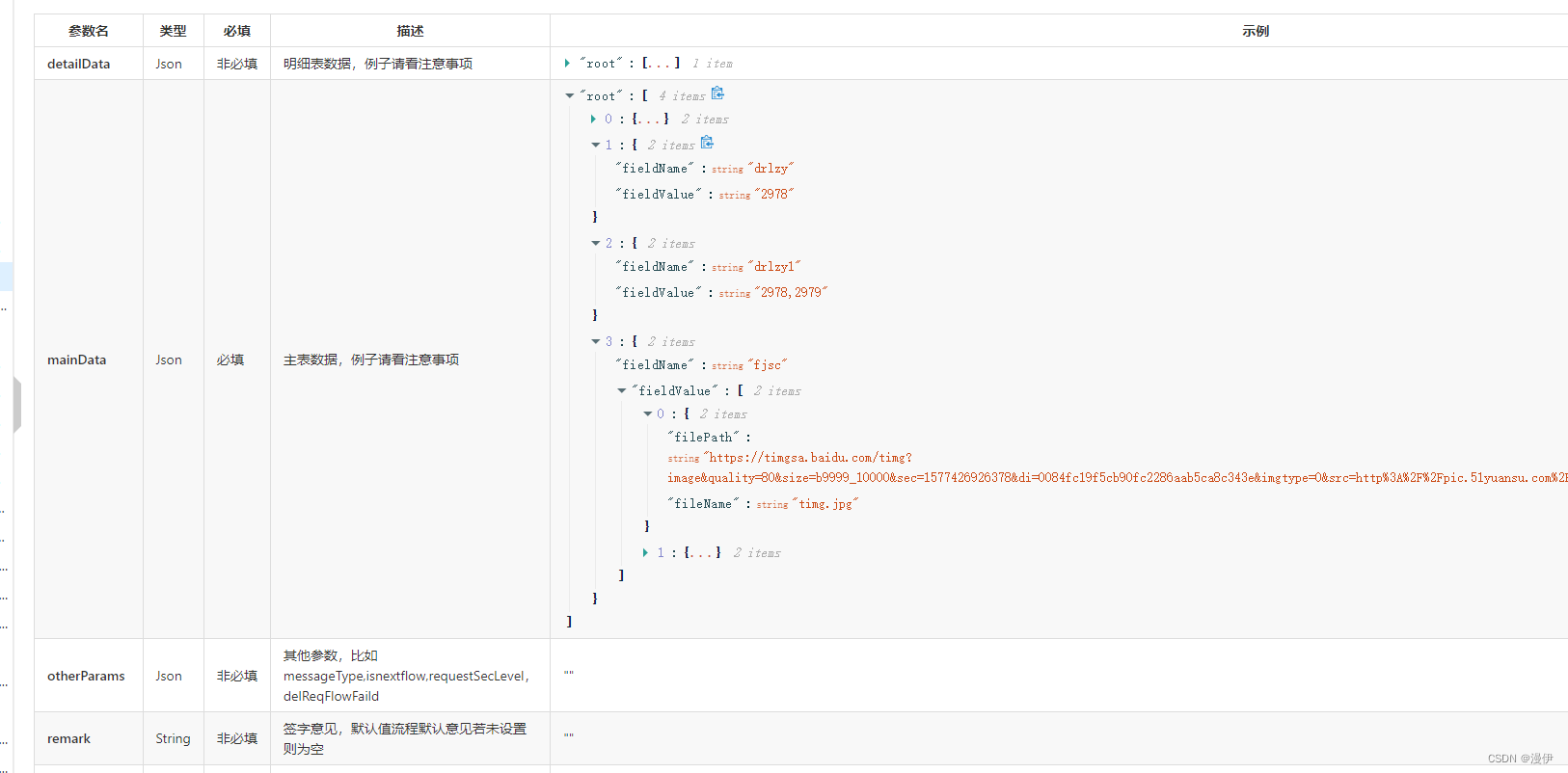

由功能管脚定义可以看到,LPDDR4多了一组DMI[1:0]信号。

在读写操作的时候,LPDDR4支持数据翻转(DBIdc)的功能。这个功能的实现是通过读写的时候控制MR3寄存器的对应位来实现的。这个功能可能会在一些软件的特殊应用场景中使用。

CA的差异

由pin脚定义可以看出,LPDDR4的CA管脚,由之前的10位,减少到了6位。6bit的CA信号仍然包含command 、address和bank的信息。还有一个改变就是CA不再像LPDDR3那样支持DDR的模式,而只是SDR的模式。所以这样看起来,其CA的效率相对于LPDDR3有所下降,考虑到接口速度上的提升,总体来说跟LPDDR3持平。

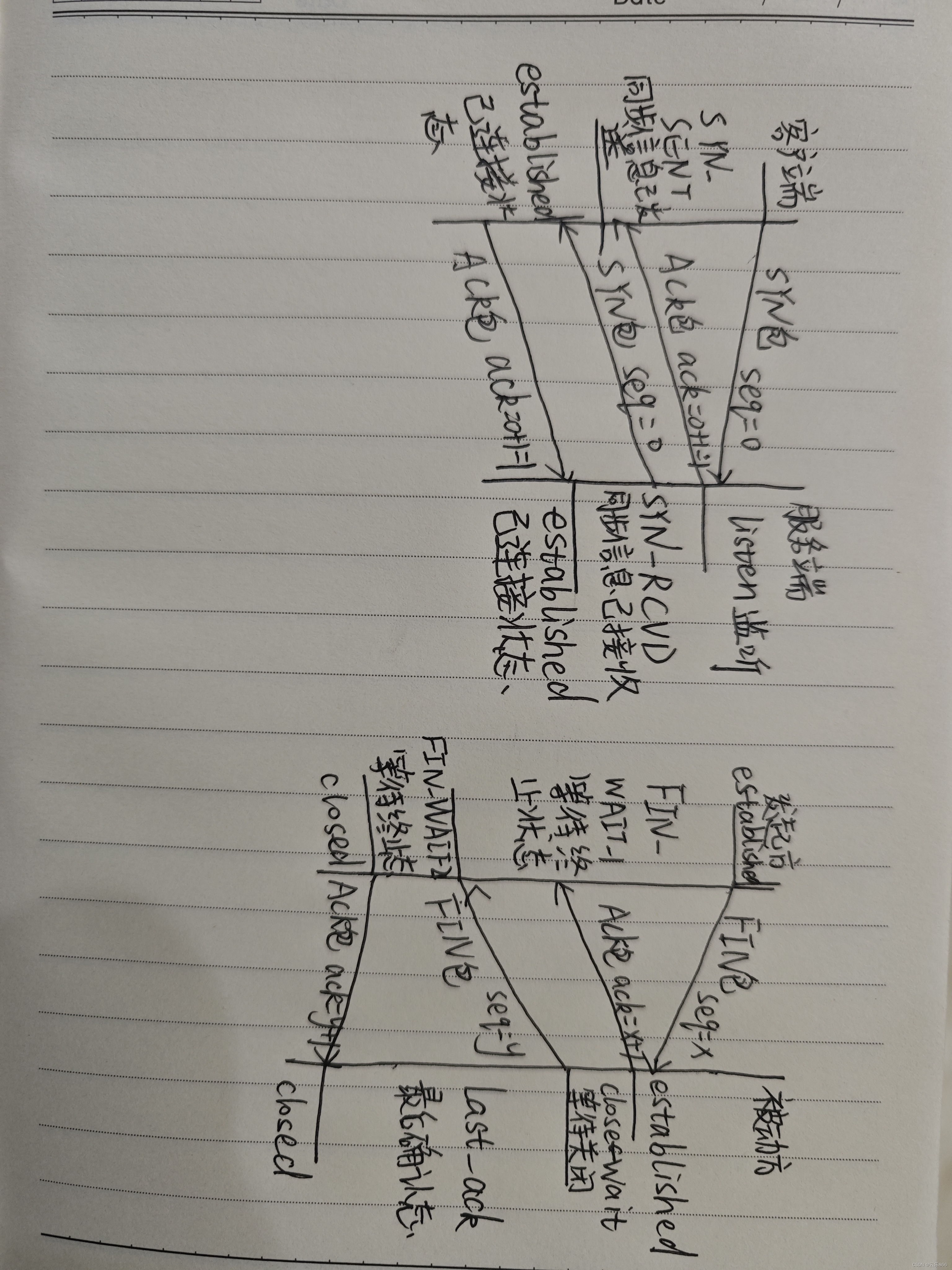

LPDDR4也包含类似LPDDR3的一个CA training的过程,不同的是LPDDR4采用的是CBT(command bus training)的方式,在这种方式中,会进行VrefCa,CLK对CS,CLK对CA的时序调整。

新增带有ECC校验功能的写命令

LPDDR3的读写操作都不带有校验功能。为了提高读写的可靠性,LPDDR4里新增了一种带有ECC校验功能的写命令(masked write command)。实际上这种带校验的写命令,是在cell内部做了个read-modify-write的动作。所以这种写操作的效率要比正常的写操作要低。

快捷方便的频率切换功能FSP功能

FSP(frequency set point)功能支持两个预设的工作频率之间的快速切换。

正常如果做频率切换的话,因为涉及不同频率的training出来的不同的值,相关寄存器会需要做重新的写入。而FSP功能通俗的说就是已经把两个预置工作频率的寄存器的值都备份好了,只要一个指令就能完成快速的完成切换。

A new approach to signaling

Recognizing that extending the LPDDR3 interface to higher frequencies would consume too much power, the JEDEC committee decided to implement a significant change in LPDDR4’s I/O signaling to low-voltage swing-terminated logic (LVSTL). LPDDR4’s LVSTL I/O signaling voltage of 367 or 440mV is less than 50% the I/O voltage swing of LPDDR3. This reduces power while enabling high-frequency operation. In addition, by using Vssq termination and data bus inversion (DBI), termination power can be minimized since any I/O signal driving a “0” consumes no termination power.

Several other steps were taken to save power. The operating voltage was reduced from the 1.2V of previous generations to 1.1V. Also, the standard was specifically designed to enable power-efficient operation at a wide range of frequencies. The I/O can operate in un-terminated mode at low frequencies with a reduced voltage swing, and the standard allows rapid switching between operating points so the lower frequency operation can be used whenever possible.

This rapid switching is enabled by the addition of frequency set points (FSPs). LPDDR4 specifies two FSPs, which are copies of all the DRAM registers that store operating parameters which might need to be changed for operation at two different frequencies. Once both operating frequencies are trained and the parameters stored in each of the two corresponding FSPs, switching between the frequencies can be accomplished by a single mode register write. This reduces the latency for frequency changes, and enables the system to operate at the optimal speed for the workload more often.

“It supports end-user flexibility,” noted Vuong. “Some designers like to run their devices as fast as they can and then put them to sleep. Others like to run at lower frequencies – and lower power – when possible. A process might take a little longer but that’s a trade-off they’re willing to make. We designed LPDDR4 to be flexible enough to allow the end-user to decide what they want to do.” With that flexibility comes superior performance – an LPDDR4 device, at a similar data rate, will consume less power than an LPDDR3 device.

Key specifications include:

- Two-channel architecture

- Internal Vref supplies for CA and DQ

- Data Bus Inversion (DBI-DC)

- ODT for CA and DQ

- I/O throughput: 3200 MT/s, rising to 4266 MT/s

- Signaling voltage: 367mV or 440mV

- Operating voltage: 1.1V

- Pre-fetch size: 32B per channel

- Topology: Point to point, PoP, MCP

- Max I/O capacitance: 1.3pF

- Write leveling

- 6-pin SDR CA bus CA training (12 pins per two channels)

- As with previous low-power DRAM generations, LPDDR4 does not require a delay-locked loop (DLL) or phase-locked loop (PLL)

LPDDR4 Workshop

To facilitate understanding and adoption of the LPDDR4 standard, JEDEC is hosting an LPDDR4 Workshop in Santa Clara, CA on September 23, 2014. For online registration and agenda information visit: http://www.jedec.org/LPDDR4-ca-2014.

About JEDEC

JEDEC is the global leader in the development of standards for the microelectronics industry. Thousands of volunteers representing nearly 300 member companies work together in 50 JEDEC committees to meet the needs of every segment of the industry, manufacturers and consumers alike. The publications and standards generated by JEDEC committees are accepted throughout the world. All JEDEC standards are available for free download from the JEDEC website. For more information, visit www.jedec.org.