0,需求

用查找表设计实现一个正弦波形发生器

寻址的位宽是10位,数据量是1024个,输出的数据是16位

1,需求分析

数据量是1024个:

x = linspace(0,2*pi,1024)

输出数据是16位:

y范围:0~2^16 -1 = 0~65535

y =( sin(x)+1)*65535/2

寻址的位宽是10位

输入是0~1023 1023 占用10位

操作步骤

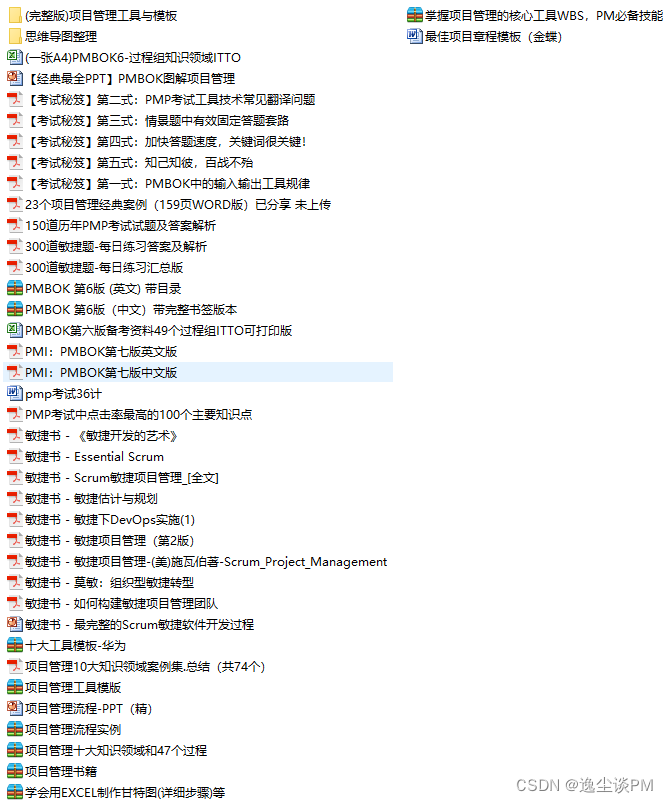

1,使用matlab 生成数据,制作sin_rom.coe文件

x = linspace(0,2*pi,1024);

y =floor( (sin(x)+1)*(65535/2));

plot(x,y);

format long g

filesize = size(y,2);

fileID = fopen('sin_rom.txt','w');

for i= 1:filesize

fprintf(fileID,'%d\n',y(i));

end

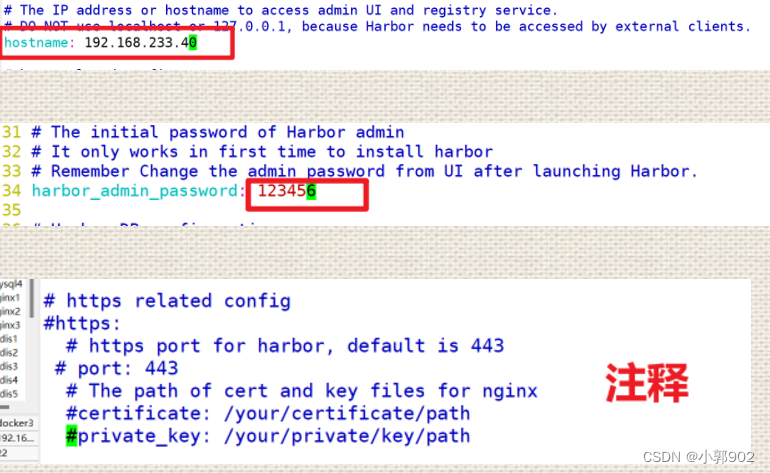

2,打开vivado,制作ROM原语

这里要注意一下,只要在IP中勾选了Primitives Output Register,那么就意味着你会延时两个时钟周期输出数据,在Summary中也可查看

3,生成原语例化文件,供程序调用

vlg_design

/

/*

用查找表设计实现一个正弦波形发生器

寻址的位宽是10位,数据量是1024个,输出的数据是16位

y = linspace(0,65535,1024)

*/

/

`timescale 1ns/1ps

module vlg_design(

input i_clk,

input i_rst_n,

input i_en,

input[9:0] i_data,

output o_vld, //有效信号

output[15:0] o_data

);

//

//o_vld是i_en两个时钟周期的延时

reg[1:0] r_vld;

always@(posedge i_clk)

if(!i_rst_n) r_vld <= 'b00;

else r_vld <= {r_vld[0],i_en};

assign o_vld = r_vld[1];

//IP ROM_LUT

blk_mem_gen_0 your_instance_name (

.clka(i_clk), // input wire clka

.addra(i_data), // input wire [9 : 0] addra

.douta(o_data) // output wire [15 : 0] douta

);

endmoduletestbench_top

`timescale 1ns/1ps

module testbench_top();

//参数定义

`define CLK_PERIORD 20

//接口申明

reg i_clk;

reg i_rst_n;

reg i_en;

reg[9:0] i_data;

wire o_vld; //有效信号

wire[15:0] o_data;

vlg_design vlg_design_inst (

.i_clk(i_clk),

.i_rst_n(i_rst_n),

.i_en(i_en),

.i_data(i_data),

.o_vld(o_vld),

.o_data(o_data)

);

integer i;

initial begin

i_en <= 0;

i_clk <= 0;

i_rst_n <= 0;

i_data <= 0;

#2000;

i_rst_n <= 1;

end

always #(`CLK_PERIORD/2) i_clk = ~i_clk;

//产生激励

initial begin

@(posedge i_clk);

@(posedge i_rst_n);

i_en <= 1;

@(posedge i_clk);

for (i = 1;i <= 1024;i = i+1) begin

i_data <= i;

@(posedge i_clk);

end

@(posedge i_clk);

i_en <= 0;

#50_000;

$stop;

end

//实时显示

always@(posedge i_clk) begin

if(o_vld) $display("%d",o_data);

else ;

end

endmodule

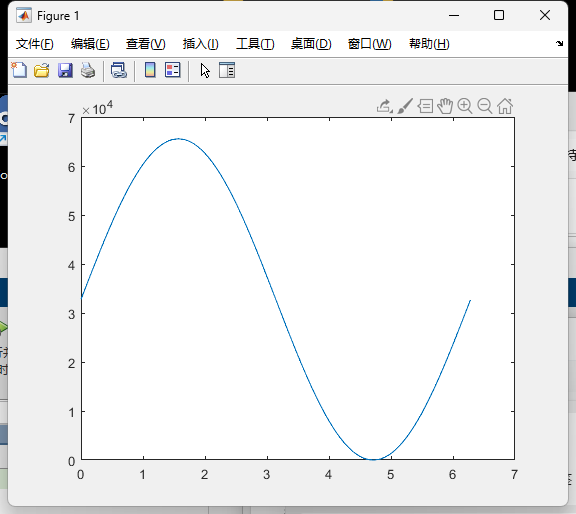

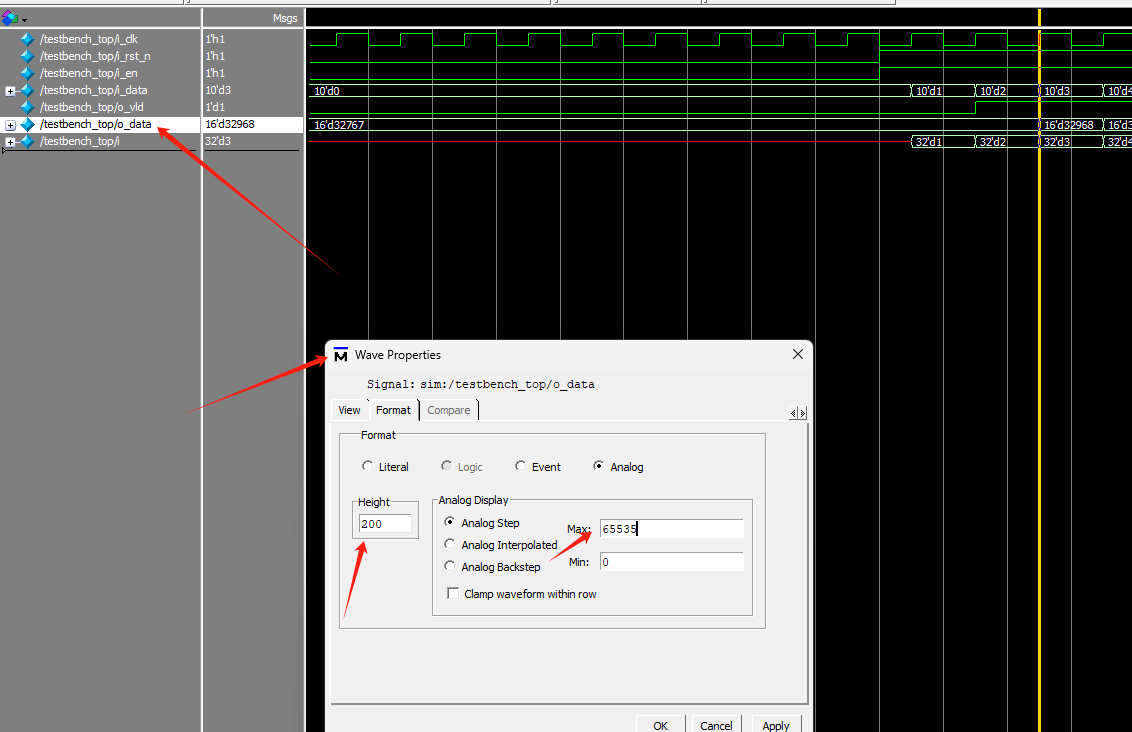

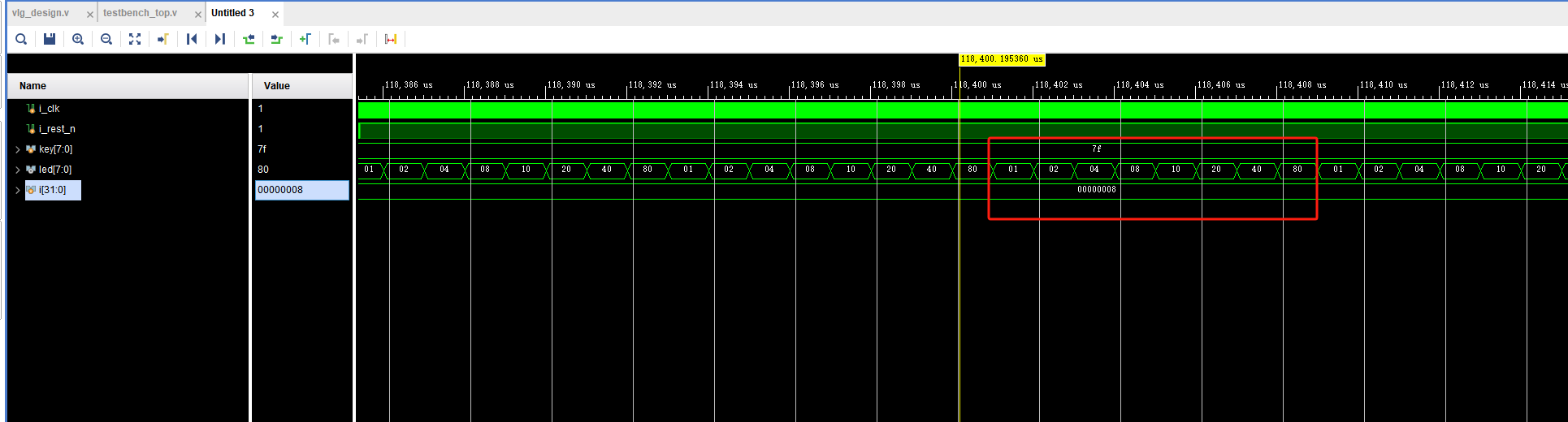

4,仿真验证输出

5,仿真波形展开,模拟输出正弦波效果

右击属性

![[C/C++]——内存管理](https://img-blog.csdnimg.cn/direct/fdd7b7a367954f80bb612199918efc9e.png)