TIMING-19 : ODDR 上的生成时钟波形反相

生成时钟 <clock_name> 的波形与传入时钟 <clock_name> 的波形相比呈反相。

描述

前向时钟端口上的生成时钟应定义为与传入时钟相关。 DRC 警告报告称 , 通过对比传入源时钟发现 , 前向时钟端口上的生成时钟具有无效的波形( 例如 , 波形反向 ) 。这可能导致硬件故障 , 因为与前向时钟关联的端口的时序分析与器件上所发生的操作不匹配。

解决方案

修改 create_generated_clock 约束以定义与传入时钟定义匹配的正确波形。

TIMING-20 : 未设置时钟的锁存器

无法正确分析锁存器 <cell_name> , 因为时序时钟无法访问其控制管脚 <pin_name> 。

描述

此 DRC 报告的是不受时序时钟约束的锁存器单元列表 , 这会影响生成的时序分析。强烈建议正确定义所有时钟以实现最大范围的时序路径覆盖, 并保证最高的准确性。否则后果可能导致时序分析覆盖范围不完整 , 从而导致硬件故障。

解决方案

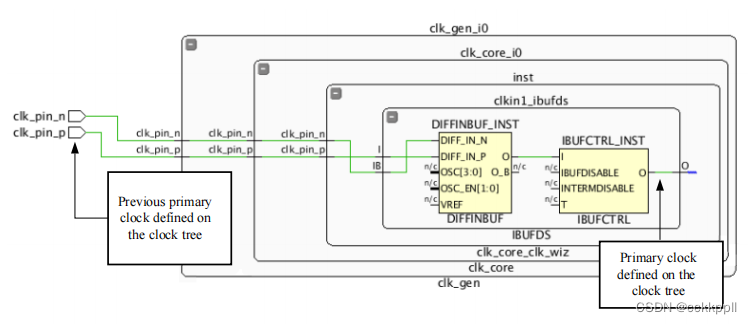

解决办法是在时钟树的源端创建基准时钟或生成时钟 , 以驱动锁存器单元上未约束的控制管脚。

TIMING-21 : MMCM 上的 COMPENSATION 属性无效

MMCM <cell_name> 包含的与其反馈回路连接相关的 COMPENSATION 属性值无效。如果反馈回路连接至 FPGA外部, 该属性应设置为 EXTERNAL 。如果反馈回路位于 FPGA 内部 , 该属性应设置为 ZHOLD 。

描述

MMCM 补偿模式用于定义为输出时钟的延迟补偿配置 MMCM 反馈的方式。根据 MMCM 用例 , 反馈路径应与特定拓扑结构相匹配。此 DRC 警告报告称 MMCM 用例的拓扑结构与 COMPENSATION 属性值不匹配。这可能导致硬件中因时序分析不匹配而出现意外行为。

解决方案

建议在设计中 , 将 MMCM 的 COMPENSATION 属性的默认值 AUTO 保留不变。 Vivado IDE 将在电路拓扑结构上自动选择相应的补偿值。

TIMING-22 : MMCM 上缺少外部延迟

MMCM <cell_name> 具有外部反馈回路 , 但在 FBOUT 与 FBIN 之间未指定任何外部延迟。建议在连接到具有外部反馈回路的 FBOUT 管脚和 FBIN 管脚的 2 个端口之间使用 set_external_delay 指定外部延迟。

描述

如果反馈板载走线与外部组件的走线相匹配 , 那么可配置 MMCM 以进行外部纠偏。在计算 MMCM 补偿延迟时会使用外部延迟值。这可能导致硬件故障( 在 I/O 路径上尤其如此 ), 因为 MMCM 补偿的时序分析与器件上所发生的操作不匹配。

解决方案

在外部反馈输入和输出端口之间为已定义的外部走线延迟添加 set_external_delay 约束。

示例

set_external_delay -from <output_port> -to <input_port>

<external_delay_value>

TIMING-23 : 发现组合循环

在组合路径上已检测到时序循环。在 <cell_name1> 与 <cell_name2> 之间已禁用时序弧 , 以中断时序循环。

描述

组合逻辑的输出回馈到其输入 , 从而生成时序循环时 , 就会创建组合时序循环。此循环会无限循环相同路径运行且无法定时, 从而导致周期数徒然增加。为解决时序循环 , Vivado IDE 会禁用循环中的单元上的时序弧 (timing arc) 。

解决方案

如果您不想创建组合反馈回路 , 请通过修改设计源文件 (RTL) 来纠正问题。但由于本应使用时序循环 , 因此请使用set_disable_timing 命令在最合理位置 ( 通常为反馈路径处 ) 中断时序循环 , 而不是交由 Vivado 时序在随机位置将其中断。

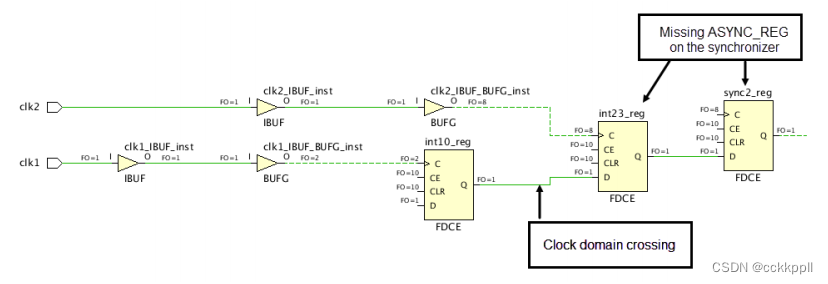

TIMING-24 : 仅最大延迟数据路径已被覆盖

时钟 <clock_name> 和 <clock_name> 之间的 set_clock_groups 或 set_false_path 覆盖了

set_max_delay -datapath_only ( 。不建议覆盖 set_max_delay -datapath_only 约束。将时钟之间的 set_clock_groups 或 set_false_path 替换为点对点 set_false_path 约束。

描述

仅当 set_max_delay -datapath_only 约束被时钟间的 set_clock_groups 或 set_false_path 约束所覆盖时, 才会出现此 DRC 警告。如果点对点 set_false_path 约束覆盖 set_max_delay -datapath_only 约束 ,那么将不会生成此 DRC 。

解决方案

解决方案是将时钟之间的 set_clock_groups 或 set_false_path 替换为点对点伪路径约束 , 以避免错误覆盖set_max_delay -datapath_only 约束。

![实用篇 | 3D建模中Blender软件的下载及使用[图文详情]](https://img-blog.csdnimg.cn/direct/1829aeb716fd4041b889a6e207ec007e.png)