在测控竞赛项目中,数据采集与处理的速度和精度往往是决定项目成败的关键因素。FPGA(现场可编程门阵列)以其并行处理能力和低延迟特性,成为实现高速数据采集与处理的理想选择。本文将探讨基于FPGA的高速数据采集与处理系统的设计与实现,并提供相应的代码示例。

1. 引言

FPGA是一种灵活的硬件平台,可以通过硬件描述语言(如VHDL或Verilog)编程来实现定制的逻辑电路。在测控竞赛项目中,FPGA可以用于实现高速数据采集、实时信号处理、数据压缩等功能。

2. FPGA在测控系统中的应用优势

- 高速并行处理:FPGA可以同时处理多个数据通道,实现高速数据采集。

- 低延迟:FPGA的数据处理延迟远低于微控制器和CPU。

- 可定制性:FPGA可以根据项目需求定制硬件逻辑,优化性能。

- 灵活性:FPGA的逻辑可以重新编程,适应不同的应用场景。

3. 系统设计

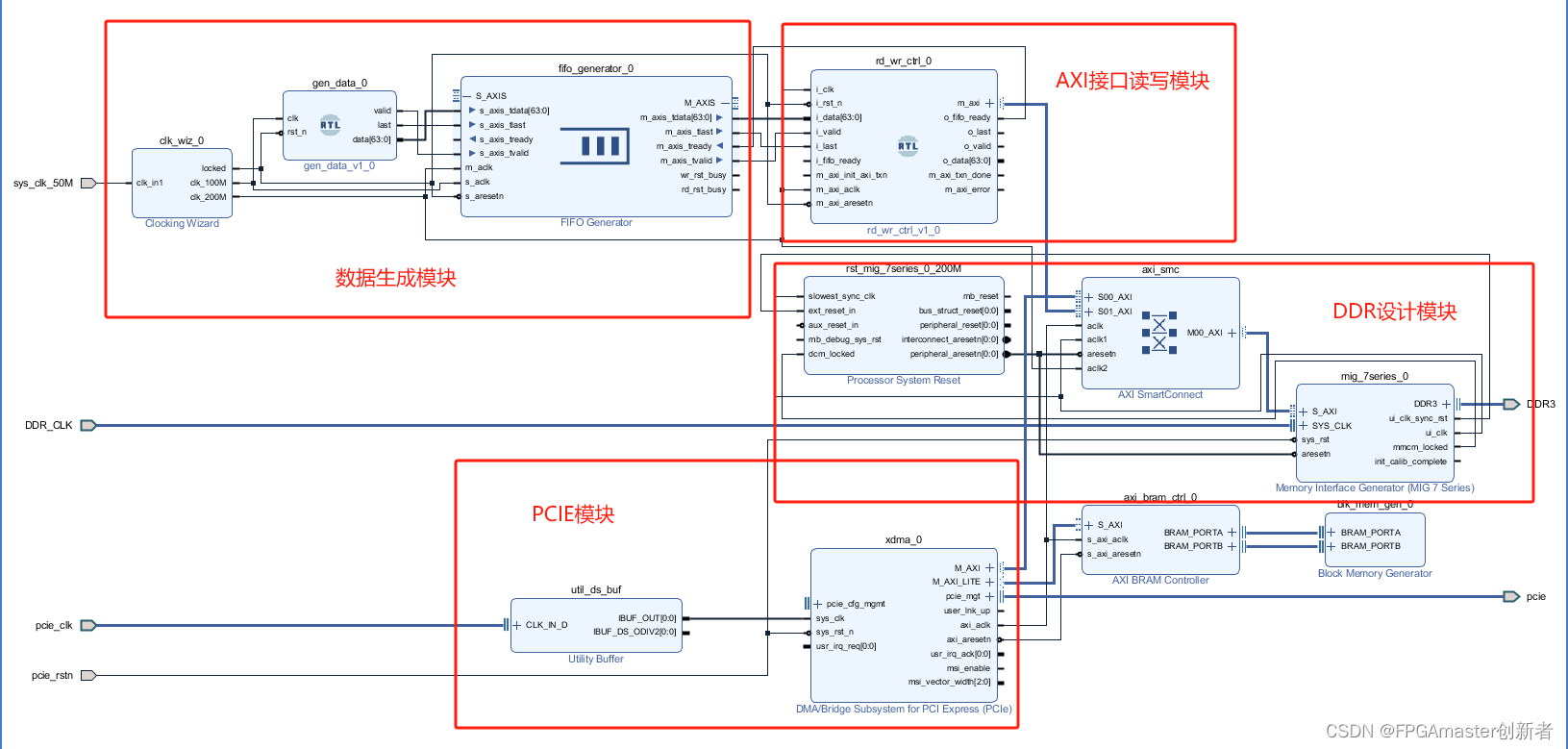

3.1 硬件设计

- FPGA选择:根据数据采集的速度和复杂度选择合适的FPGA芯片。

- 数据采集接口:设计ADC(模拟/数字转换器)与FPGA的接口电路。

- 信号调理:设计必要的信号调理电路,如放大、滤波等。

- 数据输出:设计FPGA与外部存储器或微控制器的数据通信接口。

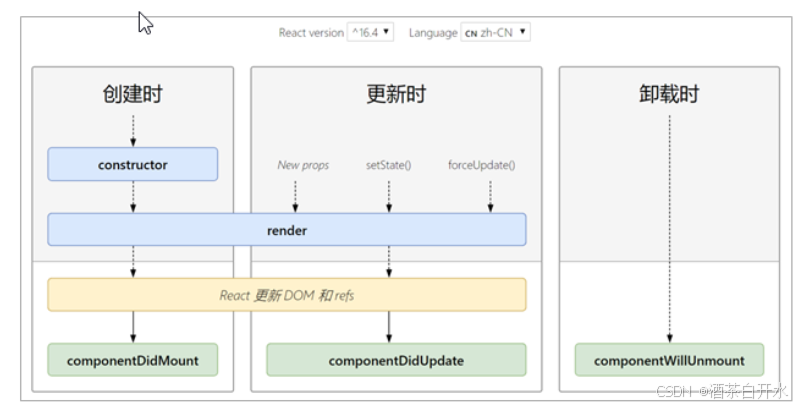

3.2 软件设计

- FPGA编程:使用VHDL或Verilog编写数据采集和处理的逻辑。

- 接口驱动:编写与FPGA通信的接口驱动程序。

- 数据处理软件:开发用于处理FPGA输出数据的软件。

4. FPGA数据采集系统实现

4.1 FPGA端设计

以下是一个简化的Verilog代码示例,用于实现FPGA端的数据采集:

module data_acquisition(

input clk, // FPGA时钟信号

input rst_n, // 复位信号

input [N-1:0] analog_signal, // N位模拟信号输入

output reg [M-1:0] digital_data // M位数字数据输出

);

reg [M-1:0] sample_data; // 采样数据寄存器

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin

sample_data <= 0;

end else begin

// 在每个时钟上升沿采样模拟信号

sample_data <= analog_signal;

end

end

// 将采样数据转换为数字数据的逻辑(示例中省略具体转换过程)

convert_to_digital(sampling_data, digital_data);

endmodule

4.2 微控制器端设计

以下是STM32微控制器与FPGA通信的示例代码:

#include "stm32f10x.h"

void SPI_Init(void) {

SPI_InitTypeDef SPI_InitStructure;

GPIO_InitTypeDef GPIO_InitStructure;

RCC_APB2PeriphClockCmd(RCC_APB2Periph_SPI1 | RCC_APB2Periph_GPIOA, ENABLE);

// 配置SPI1的MISO、MOSI和SCK引脚

GPIO_InitStructure.GPIO_Pin = GPIO_Pin_5 | GPIO_Pin_6 | GPIO_Pin_7;

GPIO_InitStructure.GPIO_Mode = GPIO_Mode_AF_PP;

GPIO_InitStructure.GPIO_Speed = GPIO_Speed_50MHz;

GPIO_Init(GPIOA, &GPIO_InitStructure);

// 配置SPI参数

SPI_InitStructure.SPI_Direction = SPI_Direction_2Lines_FullDuplex;

SPI_InitStructure.SPI_Mode = SPI_Mode_Master;

SPI_InitStructure.SPI_DataSize = SPI_DataSize_8b;

SPI_InitStructure.SPI_CPOL = SPI_CPOL_Low;

SPI_InitStructure.SPI_CPHA = SPI_CPHA_1Edge;

SPI_InitStructure.SPI_NSS = SPI_NSS_Soft;

SPI_InitStructure.SPI_BaudRatePrescaler = SPI_BaudRatePrescaler_16;

SPI_InitStructure.SPI_FirstBit = SPI_FirstBit_MSB;

SPI_InitStructure.SPI_CRCPolynomial = 7;

SPI_Init(SPI1, &SPI_InitStructure);

SPI_Cmd(SPI1, ENABLE);

}

uint8_t SPI_ReceiveData(void) {

SPI_I2S_SendData(SPI1, 0xFF); // 发送任意数据以开始接收

while(SPI_I2S_GetFlagStatus(SPI1, SPI_I2S_FLAG_RXNE) == RESET);

return SPI_I2S_ReceiveData(SPI1);

}

int main(void) {

SPI_Init();

while (1) {

uint8_t data = SPI_ReceiveData();

// 处理从FPGA接收的数据

}

}

5. 性能优化

- 并行处理:设计时充分利用FPGA的并行处理能力。

- 流水线技术:使用流水线技术提高数据处理速度。

- 资源优化:合理分配FPGA资源,如查找表(LUTs)、寄存器等。

6. 结论

基于FPGA的高速数据采集与处理系统在测控竞赛项目中具有显著优势。通过精心设计的硬件逻辑和软件程序,可以实现高性能的数据采集和实时处理。

7. 参考文献

- Xilinx Inc. (2019). FPGA Design and Implementation.

- Intel Corporation. (2020). FPGAs for High-Speed Data Acquisition.

✅作者简介:热爱科研的嵌入式开发者,修心和技术同步精进

❤欢迎关注我的知乎:对error视而不见

代码获取、问题探讨及文章转载可私信。

☁ 愿你的生命中有够多的云翳,来造就一个美丽的黄昏。

🍎获取更多嵌入式资料可点击链接进群领取,谢谢支持!👇