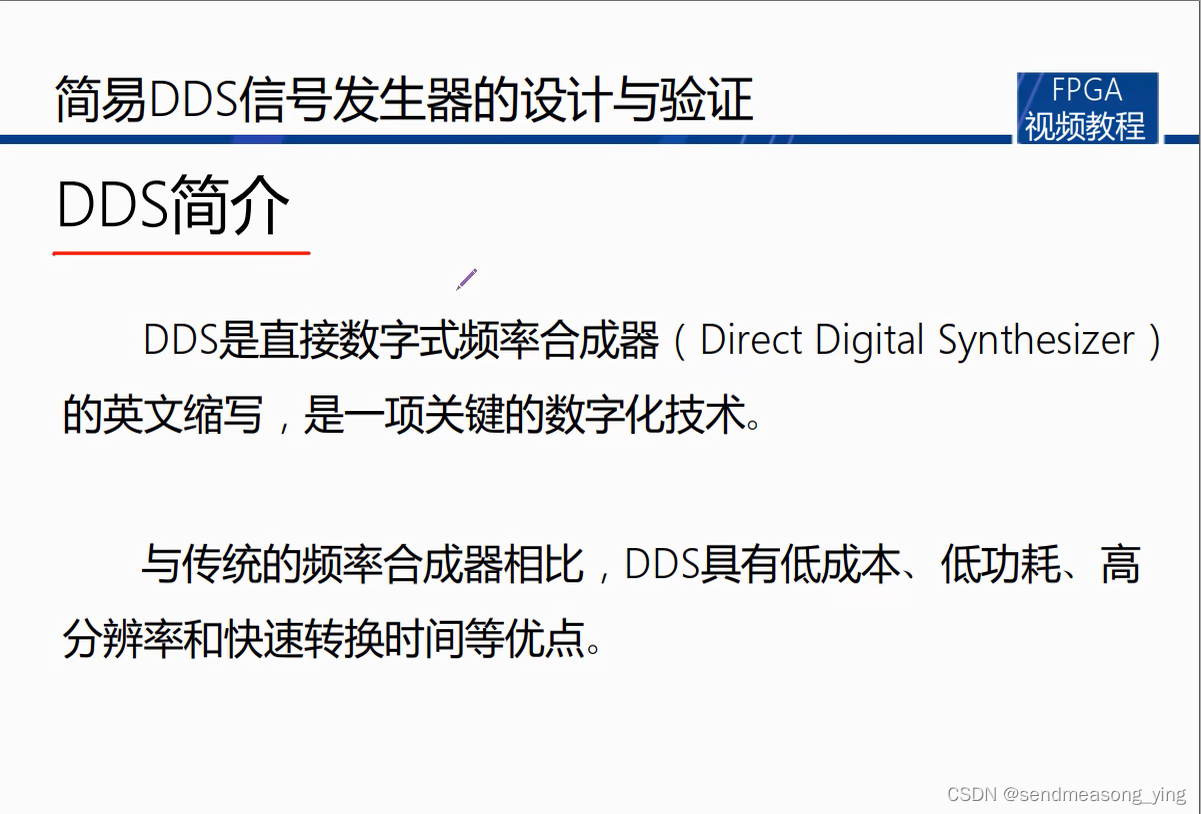

(1)VIO ip核:

VIO:虚拟输入/输出(Virtual Input/Output),可以实时监测和驱动FPGA内部信号,在线调试时,vivado软件会提供一个VIO操作界面。可以修改输出,使得待测模块的输入信号发生变化,也可以监测待测模块输出到VIO ip核内的信号。

(2)VIO调用过程:

(3)dds_core模块Verilog代码(仿真时,将VIO ip核注释掉,实际上板验证时取消注释):

module dds_core

(

input clk ,

input reset_n ,

input [3:0] wave_selcet ,

output [7:0] data_out

);

wire [31:0] fword ;

wire [11:0] pword ;

reg [13:0] addr ;

reg [31:0] r_fword ;

reg [11:0] r_pword ;

reg [31:0] fre_acc ;

/*

Fout = ford * Fclk / 2 ^ 32;

则 ford = Fout * 2^32 / Fclk;

Fclk = 50_000_000;

ford = Fout * 85.89934592

如果想要输出一个1MHz的正弦波则设置fword = 85899346

*/

/* vio_fword vio_fword_inst (

.clk (clk), // input wire clk

.probe_out0 (fword) // output wire [31 : 0] probe_out0

); */

assign fword = 32'd85899346;

//频率控制字、相位控制字的同步寄存器

always@(posedge clk)begin

r_fword <= fword;

r_pword <= pword;

end

//相位设定为0,不进行相位的相加

assign pword = 12'd0;

always@(posedge clk or negedge reset_n)

if(!reset_n)

fre_acc <= 32'd0;

else

fre_acc <= fre_acc + r_fword;

always@(posedge clk or negedge reset_n)

if(!reset_n)

addr <= 14'd0;

else begin

case(wave_selcet)

4'b1000: addr <= {2'b00,(fre_acc[31:20] + pword)};

4'b0100: addr <= {2'b01,(fre_acc[31:20] + pword)};

4'b0010: addr <= {2'b10,(fre_acc[31:20] + pword)};

4'b0001: addr <= {2'b11,(fre_acc[31:20] + pword)};

default: addr <= {2'b00,(fre_acc[31:20] + pword)};

endcase

end

rom_8x16384_sin_squ_tri_saw rom_8x16384_sin_squ_tri_saw_inst (

.clka (clk) , // input wire clka

.addra (addr) , // input wire [13 : 0] addra

.douta (data_out) // output wire [7 : 0] douta

);

endmodule

(4)dds_core模块仿真代码:

`timescale 1ns / 1ps

module dds_core_tb;

reg clk ;

reg reset_n ;

reg [3:0] wave_selcet ;

wire [7:0] data_out ;

initial clk = 1'd1;

always #10 clk = ~clk;

initial begin

reset_n <= 1'd0;

wave_selcet <= 4'b1000;

#150;

reset_n <= 1'd1;

#10000; //正弦波

wave_selcet <= 4'b0100;

#10000; //方波

wave_selcet <= 4'b0010;

#10000; //三角波

wave_selcet <= 4'b0001;

#10000; //锯齿波

wave_selcet <= 4'b1000;

#10000; //正弦波

$stop;

end

dds_core dds_core_inst

(

.clk (clk ),

.reset_n (reset_n ),

.wave_selcet (wave_selcet),

.data_out (data_out )

);

endmodule

(5)仿真波形:

![[SUCTF 2018]GetShell](https://i-blog.csdnimg.cn/direct/1db800820f734d96b69e98cb0afd2821.png)