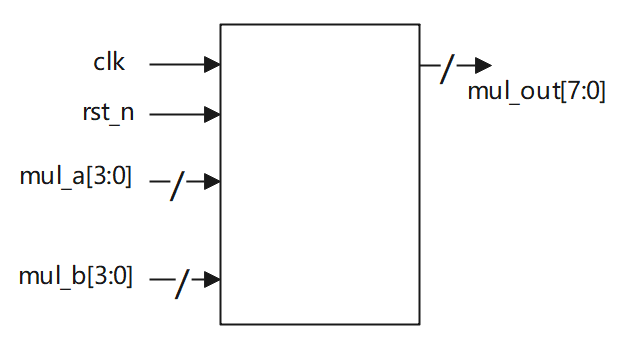

1. 设计要求

设计要求:输入为两个64bit位宽的操作数(PLUS_A和PLUS_B)。为了达到较快的时钟频率,每两级触发器之间只能实现16bit位宽的加法。该如何实现这个加法。

要求每个时钟周期都有一个操作数输入,一个操作数输出。

题目意思是:比如我当前的时钟频率为500M(2ns),支持2ns时钟频率的最大位宽加法为16bit(位宽越大,组合逻辑越多,消耗时间越多),而目前有两个64bit位宽的操作数需要相加,所以我需要设计一个流水线,在保证500M时钟频率的情况下实现数据相加。

我们的方法是:用四级流水线,每一级实现16bit数据相加,那么4级就可以实现64bit数据加法。

2. 补充

流水线:从工厂引申出来的,每个人分工合作,每个人只负责某一部分的工作。做流水线最重要的是要划分好每个人负责的部分。尽量每个人负责完成的部分时间一样。所以物品就可以一直同步往前走。

对应到电路就是划分时序,每两个触发器之间的逻辑时间尽量一样。

在刚开始的时候会有一个响应时间,响应时间指,从上电到第一个数据开始有的时间(我们需要等第一个数据出来了,后续数据就会按照流水线依次出来)

3. 设计代码

按照图中时序,写下对应代码即可

4. 仿真代码和波形