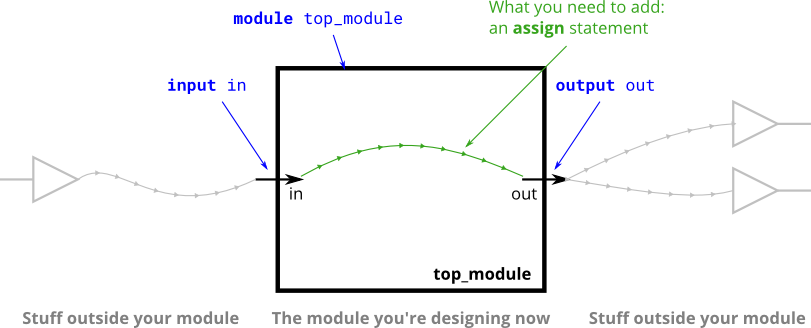

在Verilog中,wire类型是一种用于连接模块内部或模块之间的信号的数据类型。wire类型用于表示硬件中的物理连线,它可以传输任何类型的值(如0、1、高阻态z等),但它在任何给定的时间点上只能有一个确定的值。

wire类型通常用于以下几种情况:

连续赋值(Continuous Assignment):使用

assign语句将表达式的值赋给wire类型的信号。这是wire最常见的用途之一,因为它能够模拟硬件中信号线之间的直接连接。模块端口(Module Ports):在定义模块时,输入(input)和输出(output)端口默认是

wire类型的,除非显式地声明为其他类型(如reg,但reg通常不用于模块端口)。非阻塞赋值(Non-blocking Assignments)的例外:虽然

reg类型通常与过程块(如always块)中的非阻塞赋值(<=)一起使用,但在某些特殊情况下(如连续赋值或任务/函数内部),wire类型也可以用于非阻塞赋值,但这通常不是标准做法。三态逻辑(Tri-state Logic):

wire类型可以表示三态逻辑,即除了0和1之外,还可以表示高阻态(z)。这在模拟具有三态输出的硬件(如某些类型的缓冲器或选择器)时非常有用。线网(Net)与寄存器(Register)的区别:在Verilog中,

wire和reg是两种基本的数据类型,它们代表了硬件中的两种不同类型的存储元素。wire代表线网,它是物理连接的抽象,用于在模块之间或模块内部传递信号。而reg则用于在过程块中存储临时值,尽管其名称可能让人误解为寄存器,但实际上它在硬件实现中可能并不对应物理寄存器。线网类型的扩展:除了基本的

wire类型外,Verilog还提供了其他几种线网类型,如tri(三态线网)、triand(三态与门线网)、trior(三态或门线网)、trireg(三态寄存器线网)等,这些类型提供了对三态逻辑和特殊逻辑功能的支持。

总的来说,wire是Verilog中用于表示硬件中物理连接的一种基本数据类型,它在连续赋值和模块端口等场景中发挥着重要作用。

![CTF-Web习题:[HFCTF2021]Unsetme](https://i-blog.csdnimg.cn/direct/c0b99da98c694c0e860198d606c3a2a0.png)

![[CP_AUTOSAR]_分层软件架构_接口之通信模块交互介绍](https://i-blog.csdnimg.cn/direct/cf810dc56d0d4933aaaee16dcb33a7cb.png#pic_center)