1、什么是亚稳态?

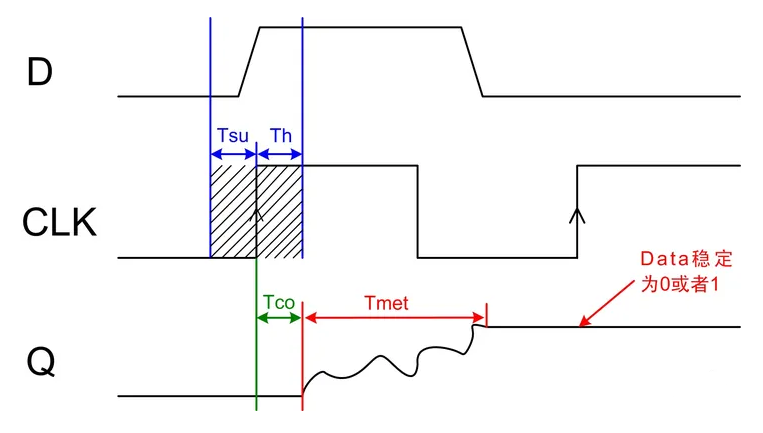

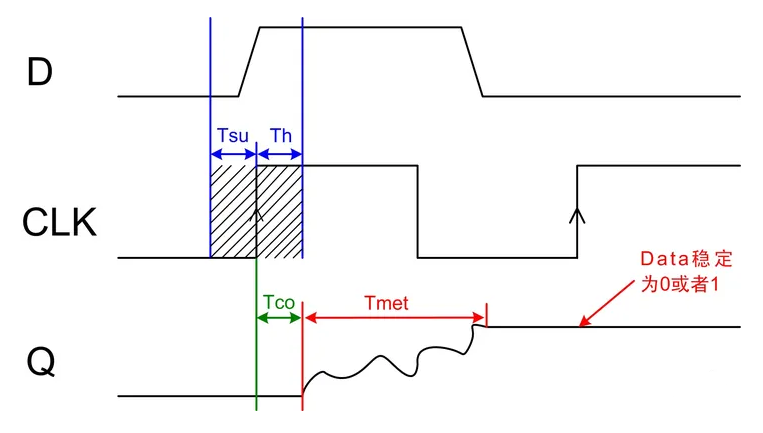

在数字电路中,如果数据传输时不满足触发器FF的建立时间要求Tsu和保持时间要求Th,就可能产生亚稳态(Metastability),此时触发器的输出端(Q端)在有效时钟沿之后比较长的一段时间都会处于不确定的状态(在0和1之间振荡),而不是等于数据输入端(D端)的值。这个时间称为决断时间Tmet(resolution time)。决断时间之后输出端将稳定到0或1上,具体是0还是1是随机的,与输入没有必然的关系。

</

在数字电路中,如果数据传输时不满足触发器FF的建立时间要求Tsu和保持时间要求Th,就可能产生亚稳态(Metastability),此时触发器的输出端(Q端)在有效时钟沿之后比较长的一段时间都会处于不确定的状态(在0和1之间振荡),而不是等于数据输入端(D端)的值。这个时间称为决断时间Tmet(resolution time)。决断时间之后输出端将稳定到0或1上,具体是0还是1是随机的,与输入没有必然的关系。

</