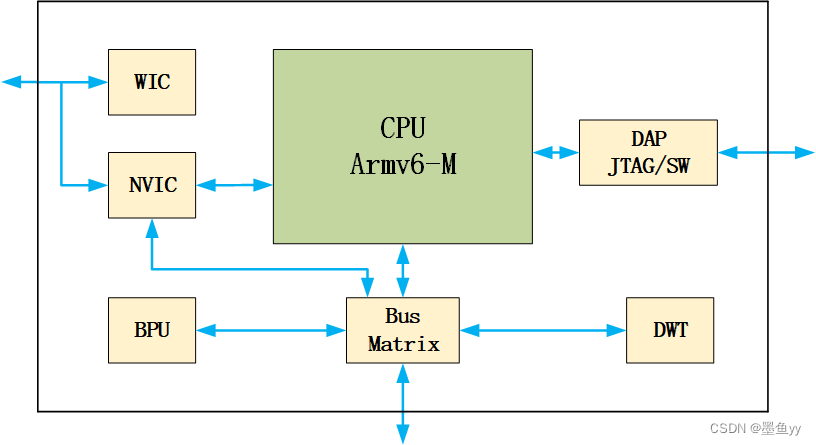

概要

Cortex-M0处理器具有非常小的面积、低功耗和最少的代码,使开发人员能够以8位的价格实现32位的性能,从而绕过了16位的设备。处理器的超低门数使其能够部署在模拟和混合信号设备中。

M0内核框图

M0内核寄存器解释

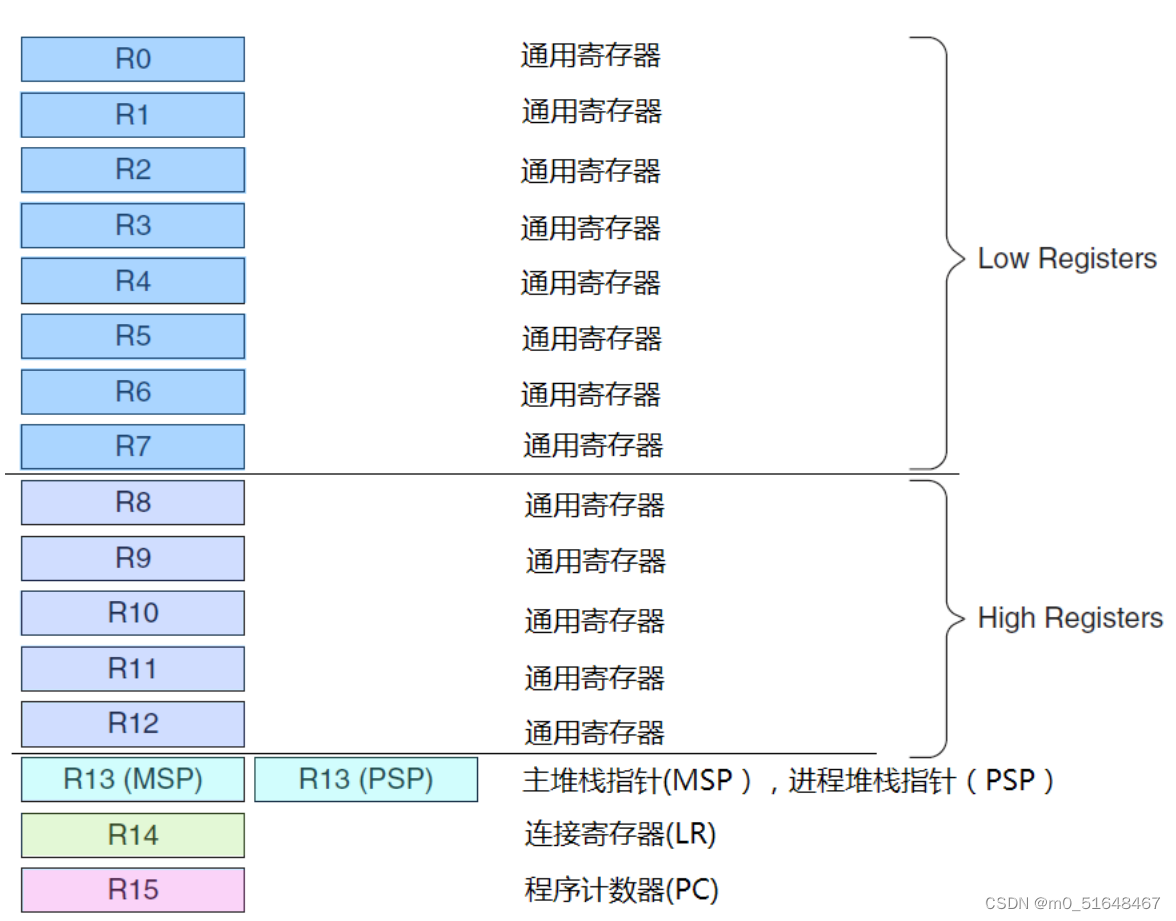

Cortex-M0处理器拥有R0-R15的寄存器组以及3个特殊功能寄存器。

| R0-R7 | 低位的通用寄存器 | 绝大数16位的Thumb 指令只能访问这些寄存器 |

| R8-R12 | 高位的通用寄存器 | 32位的Thumb指令可以访问R0-R12所有寄存器 |

| SP(R13) | 堆栈指针 | 由CONTRCL寄存器中BIT[1]控制要使用的堆栈指针

|

| LR(R14) | 连接寄存器 | 它存储子程序、函数调用和异常的返回地址 |

| PC(R15) | 程序计数寄存器 | 程序运行的实时地址 |

| PSR | 程序状态字寄存器 | 由APSR、IPSR、EPSR三个寄存器组成,可以单独访问,也可以同时访问 APSR BIT[31]: N 负数标志 BIT[30]: Z 0标志 BIT[29]: C 进位/借位标志 BIT[28]: V 溢出标志 EPSR BIT[24]: T Thumb状态标志 IPSR BIT[5:0]: 中断标志 其中APSR可读可写,其他只能读 |

| PRIMASK | 中断屏蔽寄存器 | BIT[0]用于屏蔽(除NMI)所有的中断,该位置1时有效。 |

| CONTRCL | 控制寄存器 | BIT[1]用于控制SP指针使用情况 |

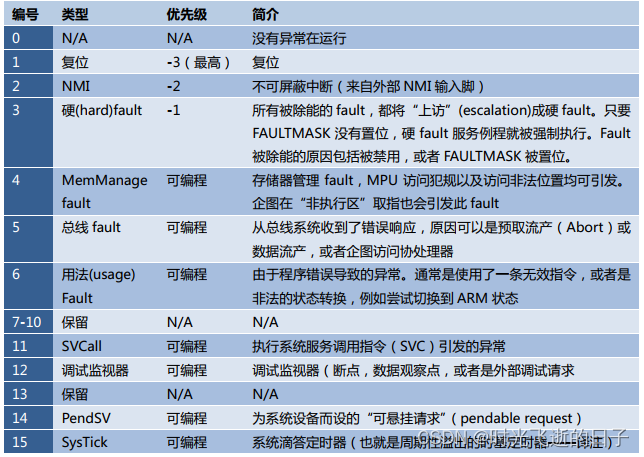

补充说明IPSR寄存器的详细解释(未写的表示保留):

| BIT[5:0] | Function |

| 0 | 线程模式,无中断产生 |

| 2 | NMI,不可屏蔽中断 |

| 3 | HardFault |

| 11 | SVCall |

| 14 | PendCall |

| 15 | SysTick |

| 16-47 | IRQ0-IRQ31 |