一.什么是状态机?

想象一下你正在玩一个电子游戏,角色有多种状态,比如“行走”、“跳跃”、“攻击”等。每当你按下不同的按键或者满足某些条件时,角色的状态就会改变,并执行与该状态对应的动作。这就是状态机的一个简单例子。

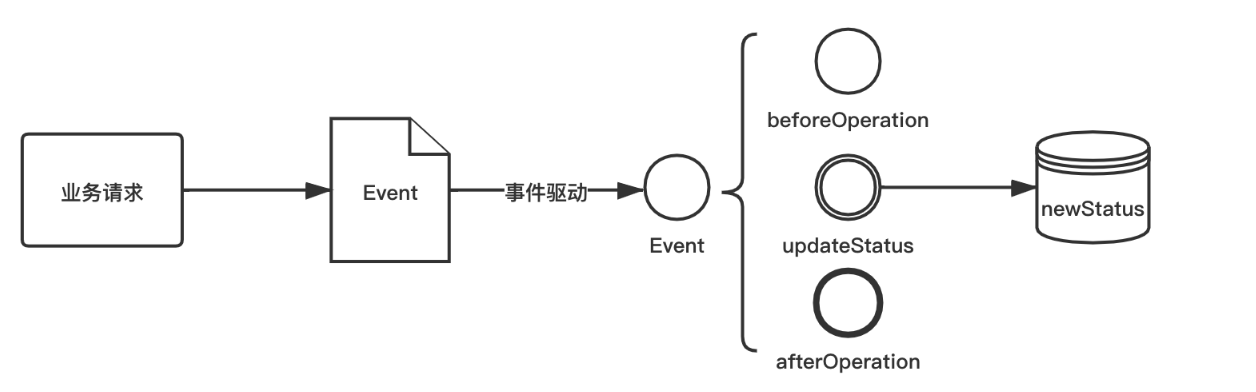

在FPGA设计中,状态机也有类似的作用。它根据输入信号和当前状态,决定下一个状态,并执行与该状态相关的操作。这些操作可以是控制某个外设、处理数据、或者改变其他模块的状态等。

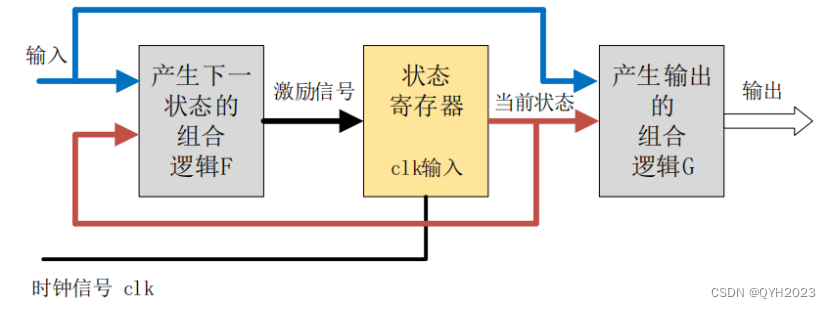

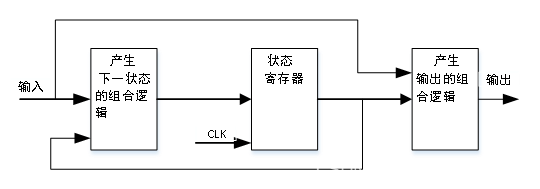

二.状态机的基本结构

状态机通常包括以下几个部分:

- 当前状态:表示状态机当前所处的状态。

- 输入信号:来自外部或其他模块的信号,用于触发状态转换。

- 状态转换逻辑:根据当前状态和输入信号,决定下一个状态。

- 输出动作:与每个状态相关的操作或响应。

三.状态机的类型

根据状态转换的方式,状态机可以分为两种类型:

- 有限状态机(Finite State Machine, FSM):只有有限个状态,并且状态之间的转换是确定的。这是最常见的状态机类型。

- 无限状态机:理论上可以有无限个状态,但在实际应用中,通常会通过一些手段将其转化为有限状态机来处理。

四.如何设计状态机?

可参考FPGA状态机(一段式、二段式、三段式)、摩尔型(Moore)和米勒型(Mealy)

• Moore 状态机:组合逻辑的输出只取决于当前状态,而与输入状态无关。

• Mealy 状态机:输出不仅取决于当前状态,还取决于输入状态。

设计状态机时,通常需要考虑以下几个步骤:

- 定义状态:明确状态机需要处理的所有可能状态。

- 定义输入和输出:确定哪些信号可以作为输入来触发状态转换,以及每个状态需要执行的输出动作。

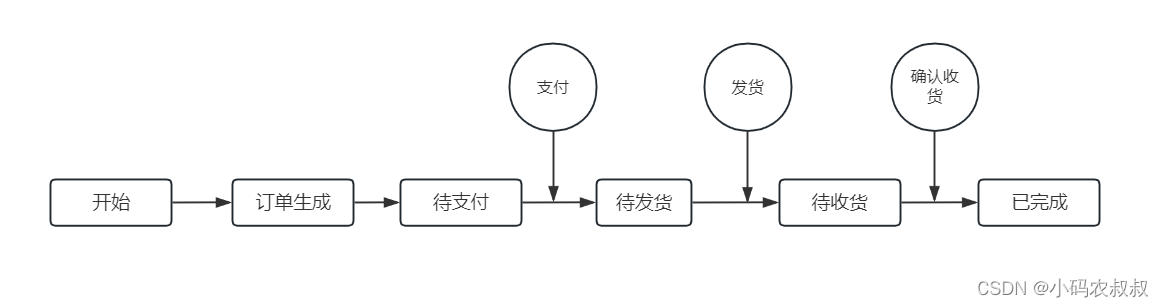

- 绘制状态转换图:使用图形化的方式表示状态之间的转换关系。

- 编写代码:使用硬件描述语言(如VHDL或Verilog)编写状态机的代码。

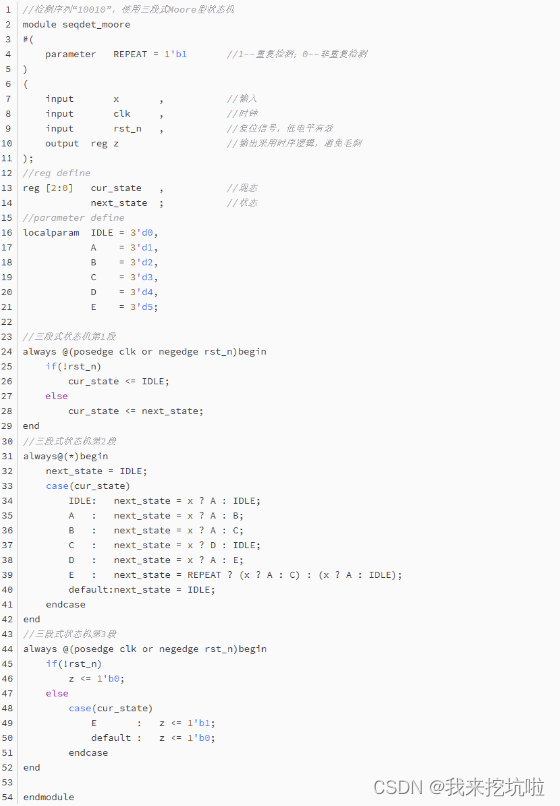

(1)Moore 状态机

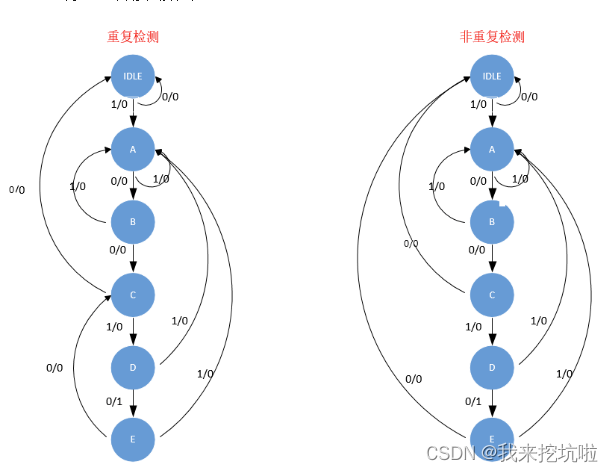

1.定义状态,输入输出

• IDLE:初始状态,对输入的码流进行检测,若为1则跳转到状态A,则为0保留在该状态

• A: 对输入的码流进行检测,若为0则跳转到状态B(10),则为1保留在该状态

• B: 对输入的码流进行检测,若为0则跳转到状态C(100),则为1则跳转到状态A(101)

• C: 对输入的码流进行检测,若为1则跳转到状态D(1001),则为0则跳转到状态IDLE(1000)

• D: 对输入的码流进行检测,若为0则跳转到状态E(10010),则为1则跳转到状态A(10011)

• E: 此时已经成功检测到了序列”10010“,可以拉高输出。

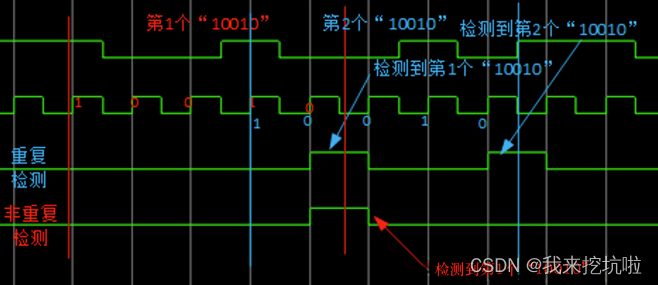

• 重复检测:然后对输入的码流进行检测,若为0则跳转到状态C(100_100,后面的100可视为新的一轮检测),则为1则跳转到状态A(10010_1)

• 非重复检测:然后对输入的码流进行检测,若为0则跳转到状态IDLE(10010_0,后面的100不可视为新的一轮检测),则为1则跳转到状态A(10010_1)

2.绘制状态转换图

3.代码

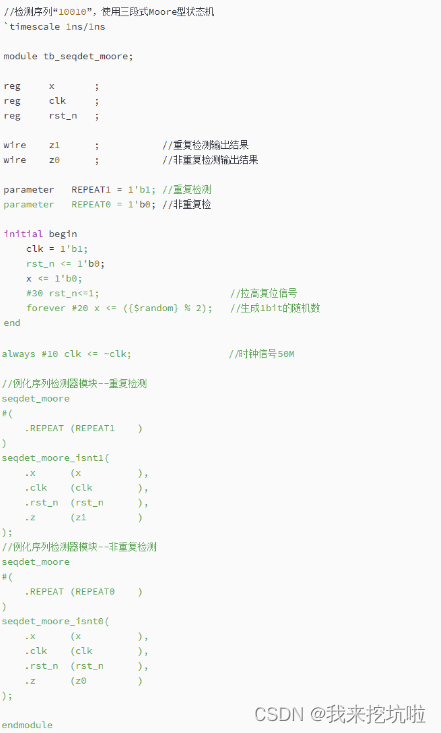

4.测试代码

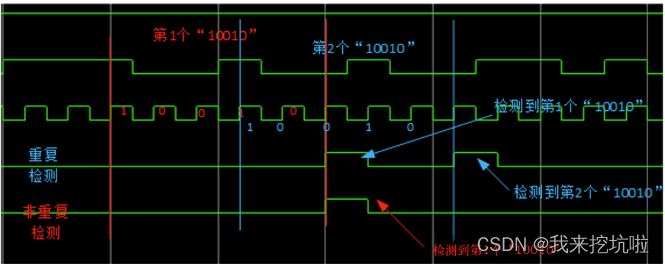

5.时序分析

(2)Mealy 状态机

Mealy 状态机的输出不仅取决于当前状态,还取决于输入状态。所以在检测到序列”1001“后,若下一个输入为0则会拉高输出;若下一个输入为1则无输出。

1.定义状态,输入输出

• IDLE:初始状态,对输入的码流进行检测,若为1则跳转到状态A,则为0保留在该状态

• A:对输入的码流进行检测,若为0则跳转到状态B(10),则为1保留在该状态

• B:对输入的码流进行检测,若为0则跳转到状态C(100),则为1则跳转到状态A(101)

• C:对输入的码流进行检测,若为1则跳转到状态D(1001),则为0则跳转到状态IDLE(1000)

• D:对输入的码流进行检测,则为1则跳转到状态A(10011);若为0则成功检测到了序列”10010“,可以拉高输出。

重复检测:则跳转到状态E(100_10,后面的10可视为新的一轮检测)

非重复检测:则跳转到状态IDLE(10010_,开始新的一轮检测)

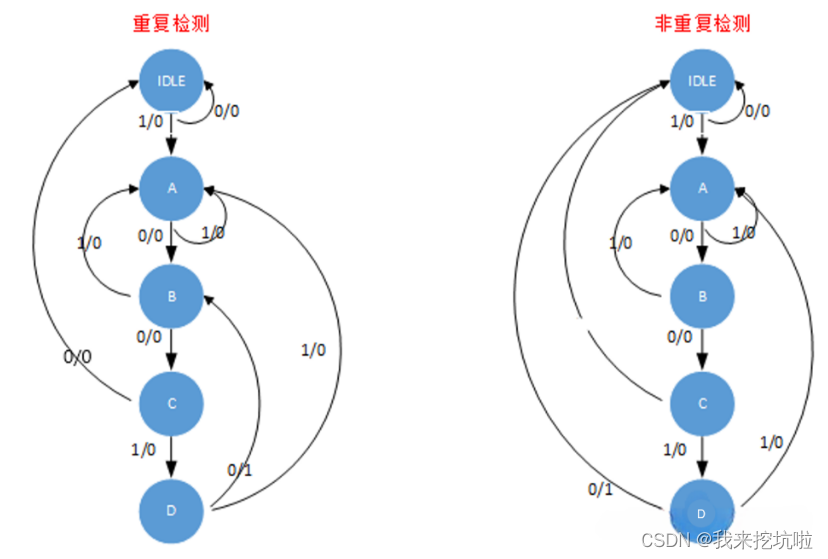

2.绘制状态转换图

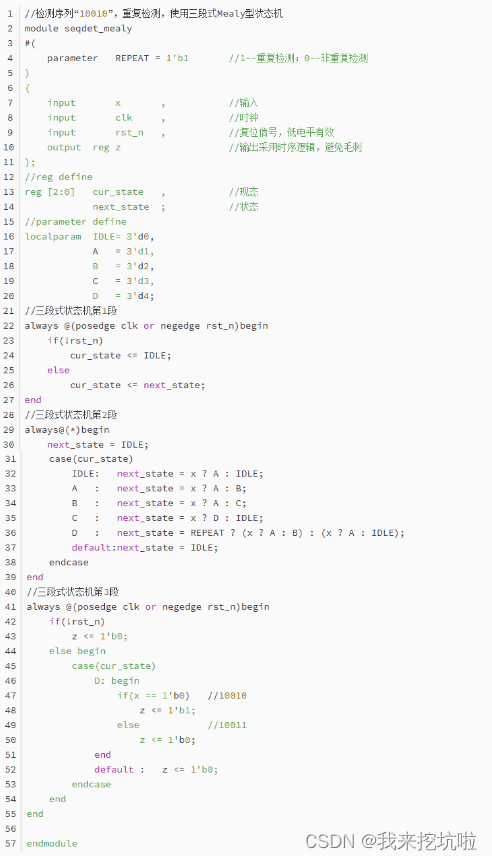

3.代码

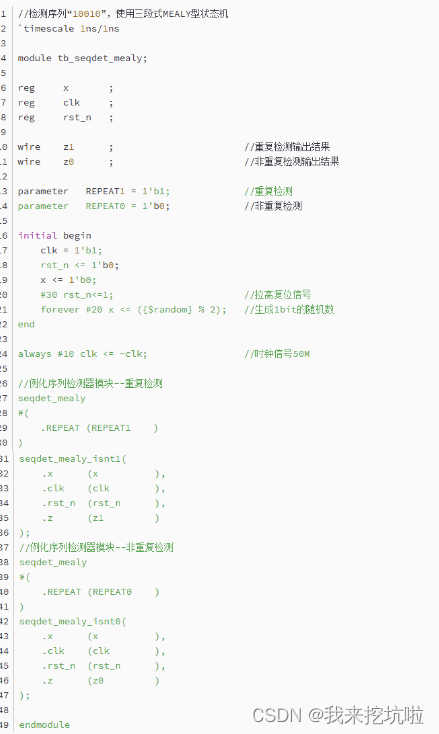

4.测试代码

5.时序分析

五.状态机的优势

使用状态机进行FPGA设计有以下几个优势:

- 结构清晰:状态机将复杂的逻辑划分为多个简单的状态,使得设计更加清晰易懂。

- 可维护性高:当需要修改或添加功能时,只需要修改相应的状态或状态转换逻辑即可。

- 可靠性高:状态机能够确保在特定条件下执行正确的操作,减少了出错的可能性。

六.总结

状态机是FPGA设计中一个非常重要的概念。它通过将复杂的逻辑划分为多个简单的状态,使得设计更加清晰、可维护且可靠。希望本文的介绍能够让你对FPGA中的状态机有更深入的了解。

![[less配置]vue2引入less](https://img-blog.csdnimg.cn/direct/665cac543e7f44bfb28b585c8b92283e.png)