1.generate用法

generate是物理上的展开,在compile时完成展开。

e.g.把array里面的每一项放入scale:

wire [7:0] array [0:7];

wire [8*8-1 :0]scale;

generate

genvar gen_x;

for(gen_x =0; gen_x <8; gen_x =gen_x +1)begin:gen_scale

assign scale[gen_x*8 +:8] = array[gen_x];//gen_x=0,从0往上8个bit

end//有*但是不用乘法器,compile时展开8遍

endgenerate//把array的8个8bit数放入[63:0]scale

2.例子:做2个16x16矩阵的减法。(对应位相减)

wire clk, rstn;

reg [7:0] a [15:0][15:0];

reg [7:0] b [15:0][15:0];

reg [8:0] sub [15:0][15:0];//减要考虑到结果为负,加1bit作为符号位。物理上会放置256个8bit减法器

generate

genvar gen_x,gen_y;

for(gen_y =0; gen_y <16; gen_y =gen_y +1)begin :gen_sub_y//sim可以不取名,compile要取

for(gen_x =0; gen_x <16; gen_x =gen_x +1)begin :gen_sub_x

always @(posedge clk or negative rstn)begin

if(!rstn)

sub[gen_y][gen_x] <= 'd0;

else

sub[gen_y][gen_x] <= {1'b0, a[gen_y][gen_x]} - {1'b0,b[gen_y][gen_x]};

end

end

end

endgenerate

3.parameter:让IP方便配置不通应用

module myadd(a,b,sum);

parameter DWIDTH = 8;

input wire [DWIDTH-1 :0]a ,b;

output wire [DWIDTH :0] sum;

assign sum = {1'b0,a} + {1'b0,b};

endmodule

module top();

wire [8:0] a9,b9;

wire [9:0] sum10;

wire [12:0] a13,b13;

wire [13:0] sum14;

myadd #(.DWIDTH(9))u_add9b(

.a(a9),

.b(b9),

.sum(sum10));

myadd #(.DWIDTH(13))u_add13b(

.a(a13),

.b(b13),

.sum(sum14));

endmodule

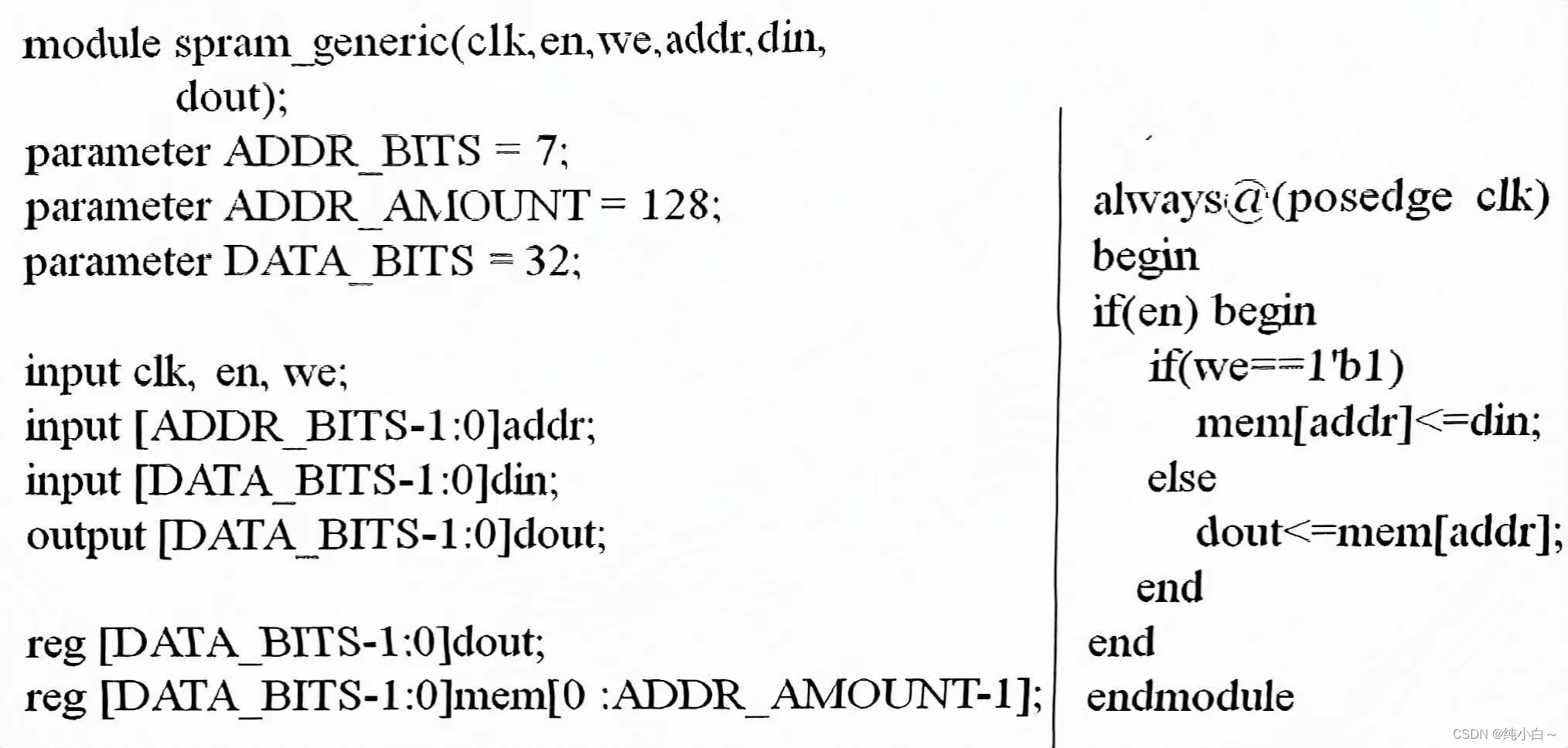

4.参数化SP-SRAM模型

FPGA工具自动推断这是个ram,但是asic就不行,它必须要用memory compile生成,因为不知道工艺库(28nm or 40nm, tsmc台积电 or smic中芯国际)

5.为什么要定义阻塞赋值,非阻塞赋值?

硬件行为本身是并行的,而CPU是串行行为,为了用串行行为去仿真并行行为,规定了阻塞/非阻塞赋值。

可综合Verilog建议:

定义成reg的组合逻辑,用=赋值;

定义成reg的时序逻辑,用<=赋值。

详细参考

Pattern输出给DUT的信号最好不要跟clk对齐,在tb顶层故意加一个#0.1。

![[<span style='color:red;'>笔记</span>] <span style='color:red;'>SKF</span> Enveloping FAQ 用户指南](https://i-blog.csdnimg.cn/direct/41784d03fd7d40c6a38b1c59510ce8dc.png)

![[Windows] Bypass分流抢票 v1.16.25 五一黄金周自动抢票软件(2024.02.08更新)](https://img-blog.csdnimg.cn/direct/5a933d8bb0a44159bbae2b92f80cb2be.png)