主要参考

零基础学FPGA(六):FPGA时钟架构(Xilinx为例,完整解读)_fpga中的全局时钟-CSDN博客

名词缩写

BUFG:全局时钟,可以达到

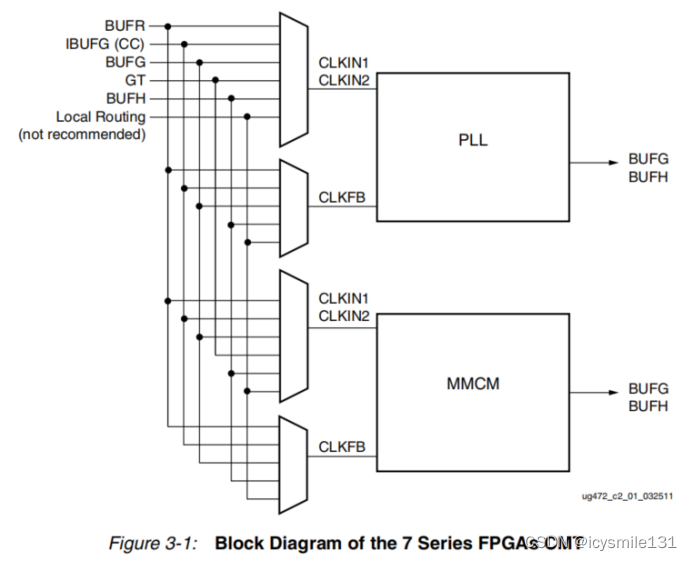

CMT:时钟管理块,常用的MMCM(混合模式时钟管理器)和PLL(锁相环)模块就位于CMT中,每个CMT包含一个MMCM和一个PLL,位于I/O列旁边的CMT列中。提供时钟频率合成、减少偏移和抖动过滤等功能

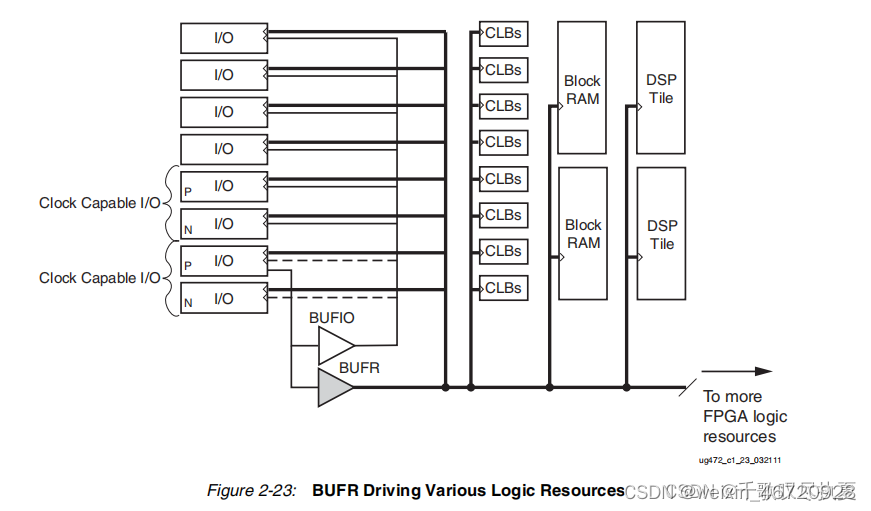

BUFIO:IO时钟缓冲器,位于IOB中,输出只能到达本时钟区域的IO寄存器,无法在FPGA内部逻辑使用。

BUFR:单区域时钟缓冲器,可以驱动内部逻辑CLB和其他同步资源BRAM、DSP等。

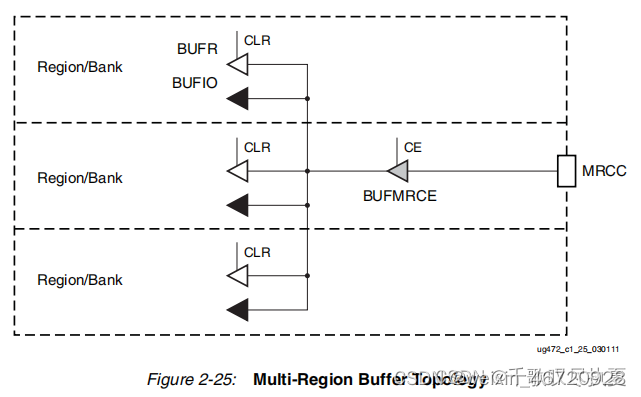

BUFMR:多区域时钟缓冲器,允许最多为三个垂直相邻的时钟区域提供时钟

时钟资源与非时钟资源

xilinx 7系列FPGA中有专门为时钟信号设计的资源,本地布线等非时钟资源,不推荐用于时钟功能。

时钟引脚

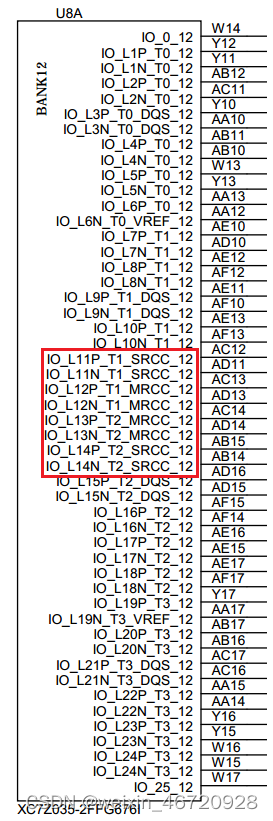

引脚名称为MRCC或SRCC,MR=Multiple Region(多时钟域),SR=Single Resion(单时钟域),CC=Clock Capable。

每个BANK有50个引脚,其中有4对差分CC管脚(其中2对SRCC,2对MRCC)。

SRCC作为区域时钟使用时,只能连接本时钟区域的BUFR和BUFIO。

MRCC则还可以通过BUFMR作用在上下相邻的时钟区域。

它们都是差分的,如果接单端时钟则需接到“P”上,对应的“N”引脚不可用。

时钟区域

时钟区域是一个跨越50个CLB和1个IO BANK的区域,包含了其中的所有同步元素例如:CLB、I/O、串行收发器、DSP、BRAM、CMT。不同器件的时钟域个数不同,从1个到24个。