IP integrator 中的调试流程

Vivado IP integrator 中的 System ILA IP 允许您对 FPGA 或 ACAP 上的实现后设计执行系统内调试。如需监控 IP

integrator 块设计中的接口和信号 , 请使用此功能。此功能支持您在 Vivado 硬件管理器中对 AXI 读写、数据和地址通

道事件以及 AXI 读写传输事务进行调试。

注释 : 在 Versal 器件上 , 使用 ILA 核时支持所有 System ILA 功能 , 并且可通过将“ ILA 输入类型 (ILA Input Type) ”从

Net Probes 更改为 Interface Monitor 来选择相应的功能。

请访问此 链接 并参阅《 Vivado Design Suite 用户指南 : 采用 IP integrator 设计 IP 子系统》 ( UG994 ) 中的相应内容 , 以

了解在块设计中调试接口和 / 或信号线的步骤。

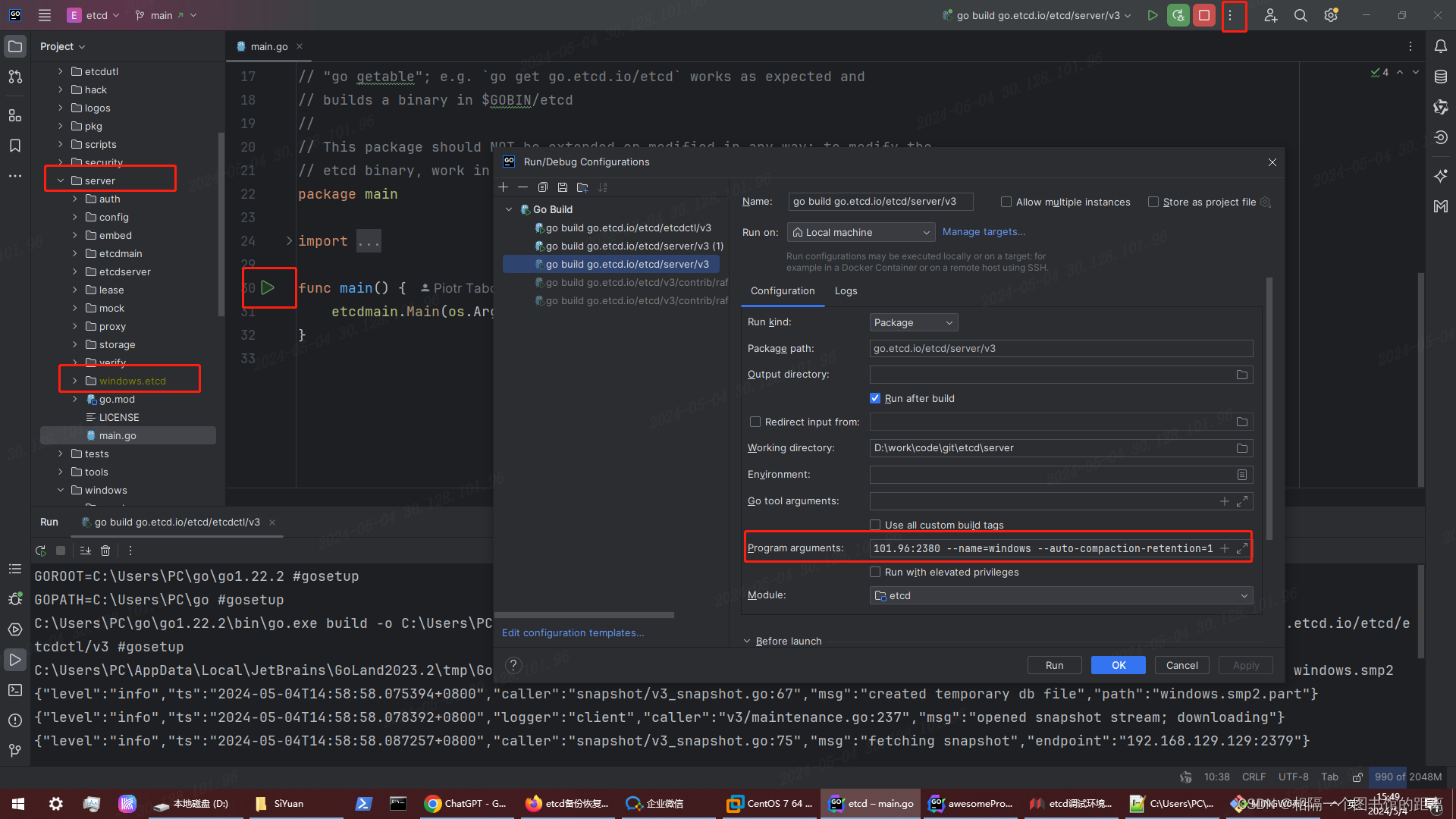

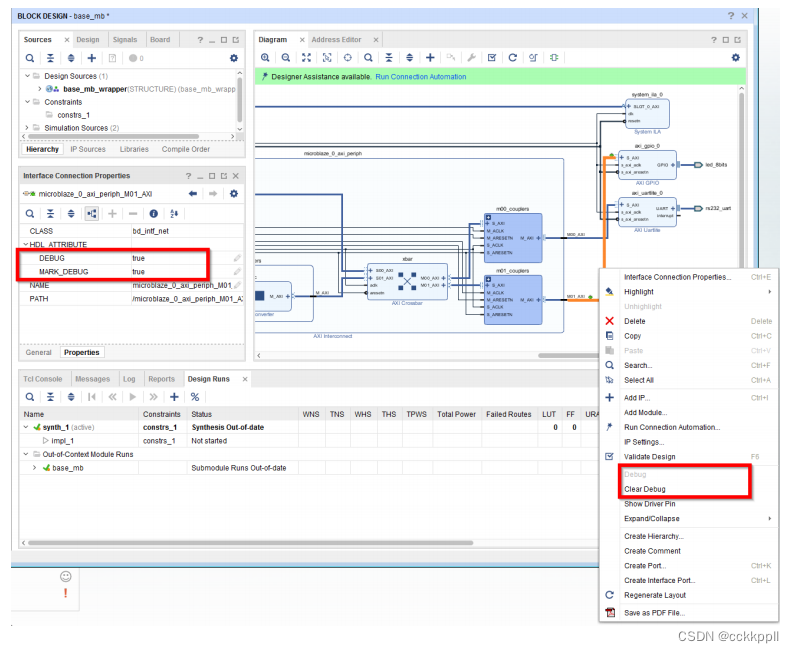

在 IP integrator 块设计中调试信号线和接口

在 IP integrator 块设计画布中 , 可调试信号线和接口。如下所示 , 您可在块设计中右键单击接口或信号线 , 并选择“调

试 (Debug) ”。这样即可将“ Debug ”和“ MARK_DEBUG ”属性设为 true 。此外 , 这样还可启用“设计辅助 (Designer

Assistance) ”以运行“自动连接功能 (Connection Automation) ” , 以供您选择连接到 System Interface ILA 核的信号线

和 / 或接口 , 并可自定义调试核的各属性。

要清除调试属性的信号线和 / 或接口 , 请右键单击信号线或接口 , 然后单击“ Clear Debug ”。

在已综合的设计内查看 System ILA 调试核

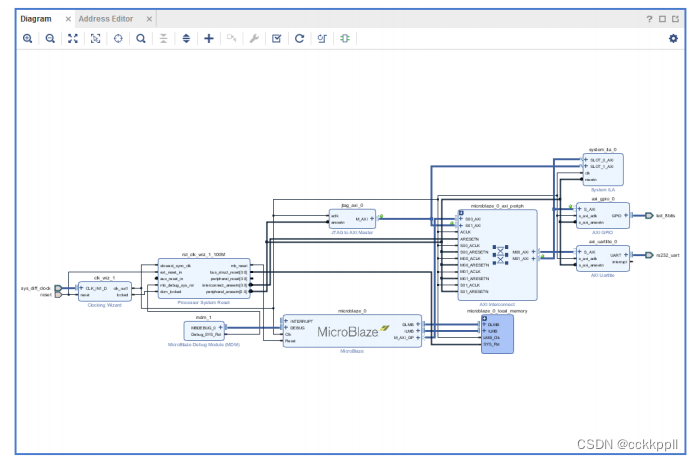

IP integrator 块设计中的 System ILA IP 必须例化。下图所示快照中的块设计包含 2 个已例化的调试核 : System ILA 和

JTAG to AXI Master IP 核。

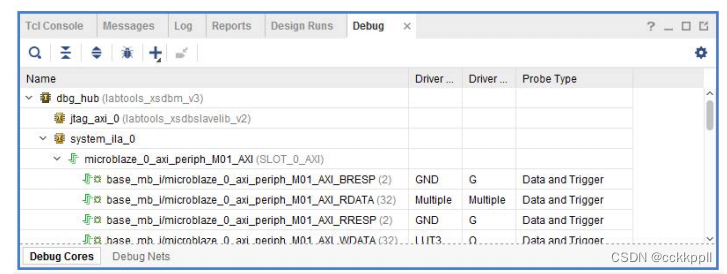

在此块设计完成验证和综合后 , 您可在已综合的设计中打开“调试 (Debug) ”窗口以查看已例化并插入设计的调试核。

System ILA 和 JTAG to AXI Master 调试核如下所示。

如需了解有关如何使用这些接口在硬件管理器中进行调试以及如何利用 AXI 事件级调试的详细信息 , 请参阅“在硬件

管理器中调试 AXI 接口”。

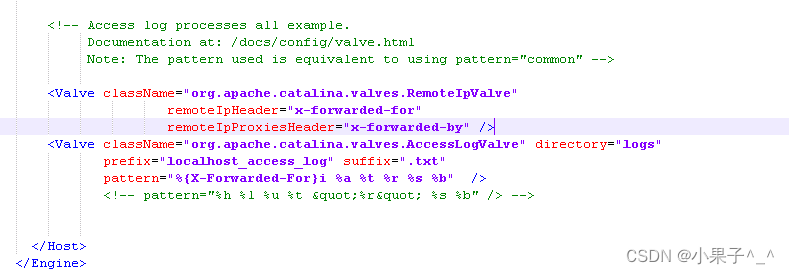

对包含调试核的设计执行实现

Vivado 软件最初以黑盒形式创建 Debug Hub 核。必须先实现该核 , 然后才能运行布局器和布线器。

实现设计

在 Vivado Design Suite 中单击“ Run Implementation ”或者运行以下 Tcl 命令来实现包含调试核的设计 :

launch_runs impl_1

wait_on_run impl_1

您也可以使用实现命令 opt_design, place_design 和 route_design 来实现设计。如需了解有关各种设计实现

方法的更多详细信息 , 请参阅《 Vivado Design Suite 用户指南 : 实现》 ( UG904 ) 。

ILA 核和时序考虑因素

ILA 核的配置会对能否满足整体设计时序目标产生影响。请根据下列建议进行操作 , 以便最大程度减少对时序的影响 :

• 请审慎选择探针宽度。随探针宽度增加 , 对资源利用率和时序的影响也会增大。

• 请审慎选择 ILA 核数据深度。随数据深度增加 , 对块 RAM 资源利用率和时序的影响也会增大。

• 请确保为 ILA 核选择的时钟均为自由运行的时钟。否则可能造成在器件上加载设计时无法与调试核通信。

• 在添加调试核之前完成设计上的时序收敛。赛灵思不建议使用调试核调试相关时序问题。

• 请确保输入到 ILA 核的时钟与正在探测的信号同步。否则在设计编程到器件中时会产生时序问题并导致通信失败。

• 在硬件上运行设计之前请确保设计已满足时序要求。否则会导致结果不可靠。

• 对于非 Versal 架构 : 请确保提供给 dbg_hub 的时钟为自由运行的时钟。否则可能造成在器件上加载设计时无法与

调试核通信。可使用 connect_debug_port Tcl 命令将 Debug Hub 的 clk 管脚连接到自由运行的时钟。

• 对于非 Versal 架构 : 如果仍发现因添加 ILA 调试核而导致时序劣化 , 并且关键路径位于 dbg_hub 中 , 请执行以下

步骤 :

1. 打开已综合的设计。

2. 找到网表中的 dbg_hub 单元。

3. 转至 dbg_hub 的“ Properties ”选项卡。

4. 找到 C_CLK_INPUT_FREQ_HZ 属性。

5. 将其设置为连接到 dbg_hub 的时钟频率 (Hz) 。

6. 找到 C_ENABLE_CLK_DIVIDER 属性并将其启用。

7. 重新执行设计实现。