原语就是对FPGA底层器件的直接调用,与IP功能是类似的,将原语的参数变成IP配置时的GUI界面参数,可能会更加直观。IP的缺陷在于繁杂,比如SelectIO IP内部包含IDDR、ODDR等等IO转换的功能,如果只想使用单沿转双沿一个功能,那么调用SelectIO IP相比直接使用IDDR原语会麻烦很多。

手册中关于原语的讲解其实是比较枯燥的,在实际使用时,还需要与vivado的Default Layout界面相结合,知道该原语在FPGA中的位置,相关接口的走线。比如IDDR、ISERDESE、IBUFDS、IDELAYE、IOB、ILOGIC这些器件的区别,物理位置分布,输入输出信号连接等等,只有搞懂这些关系,才能真正的灵活应用。

因此我在讲解每个原语的时候都会去通过Default Layout界面分析该原语的位置,以及与其他原语的位置关系,从而理解有些IDDR和ISERDESE会共用ILOGIC资源,不能同时使用,这也是两个器件都能实现双沿采样的一个原因。

另外为什么IDDR输入不能用ILA抓取?这也可以从Default Layout界面走线分析得到结果,因为IDDR输入来自IOB,并没有进入FPGA逻辑单元,而ILA只能通过可编程逻辑资源去抓取逻辑部分的信号。

首先需要通过下文了解原语是什么,以及xilinx的芯片有哪几类常规bank,zynq 7000系列哪些是K7架构,哪些是A7架构,HP bank和HR bank的区别,以及高速收发器GTX和GTP。

1、IO相关原语

FPGA内部均使用单端信号,但是经常会使用LVDS等差分信号,此时在IOB处就需要使用IBUFDS将外部输入差分信号转换为单端信号给内部使用,使用OBUFDS将单端输出信号转换为差分输出信号。

同时需要注意IBUFGDS是时钟专用的差分转单端原语。最后需要通过Default Layout去查看这些原语的具体位置,以及怎么实现单端和差分转换的,要留下印象。

多数人应该都听说过双沿传输,但是FPGA内部逻辑处理的数据均是单沿传输,如果要处理双沿传输的输入数据,需要通过IDDR原语将双沿信号转换为单沿信号,之后才能传入FPGA内部逻辑,进行处理。

下面是IDDR原语的讲解及仿真、上板测试,重点需要注意IDDR的位置,使用的资源,以及ILOGIC怎么用作IFD,也就是将IDDR用作D触发器,使得输入路径足够短。

外部信号进入FPGA管脚,到达IDDR输入端的路径是固定的,如果要实现多个信号的对齐,是无法像内部逻辑那样,通过调节器件位置和走线长度来达到延迟目的的,因此xilinx在提供了一个原语IDELAYE,通过设置该原语的参数,可以调节输入信号的延迟。

xilinx原语介绍及仿真——IDELAYE2 & IDELAYCTRL

关于信号输入,还有一个ISERDESE原语,可以将串行的单沿/双沿数据转换为并行的单沿数据,如果需要进行串并转化和双沿采样则使用ISERDESE原语。如果只需要双沿采样,则使用IDDR即可。

在此之前,博客上几乎没有文章详细说明该原语的对齐信号的使用,因此写了这篇文章,主要是理解bitslip信号的使用以及原语。

前面是输入端口的一些原语,输出端口也有对应的原语,比如将单沿信号转换为双沿输出的原语ODDR。

需要详细了解ODDR的位置,才能知道其输出为什么不能作为ILA的输入,以及了解ODDR用作OFD的方式。

如果是HR bank,则OLOGIC输出直接与IOB相连,如果是HP bank,则OLOGIC与IOB之间可以使用ODELAYE进行延时,该原语的使用和相关参数与IDELAYE基本一致。

IO相关的最后一个原语是并串转换的OSERDESE,可以将单沿传输的并行信号转换为单沿或双沿传输的串行数据,串行速率与芯片结构和速度等级有关。

注意OSERDESE的位置,会发现其与ODDR和OFB位置一致,共同使用OLOGIC资源,因此一个信号只能使用其中一个原语,不能同时使用OSERDESE、ODDR、OFB。

2、时钟资源相关原语

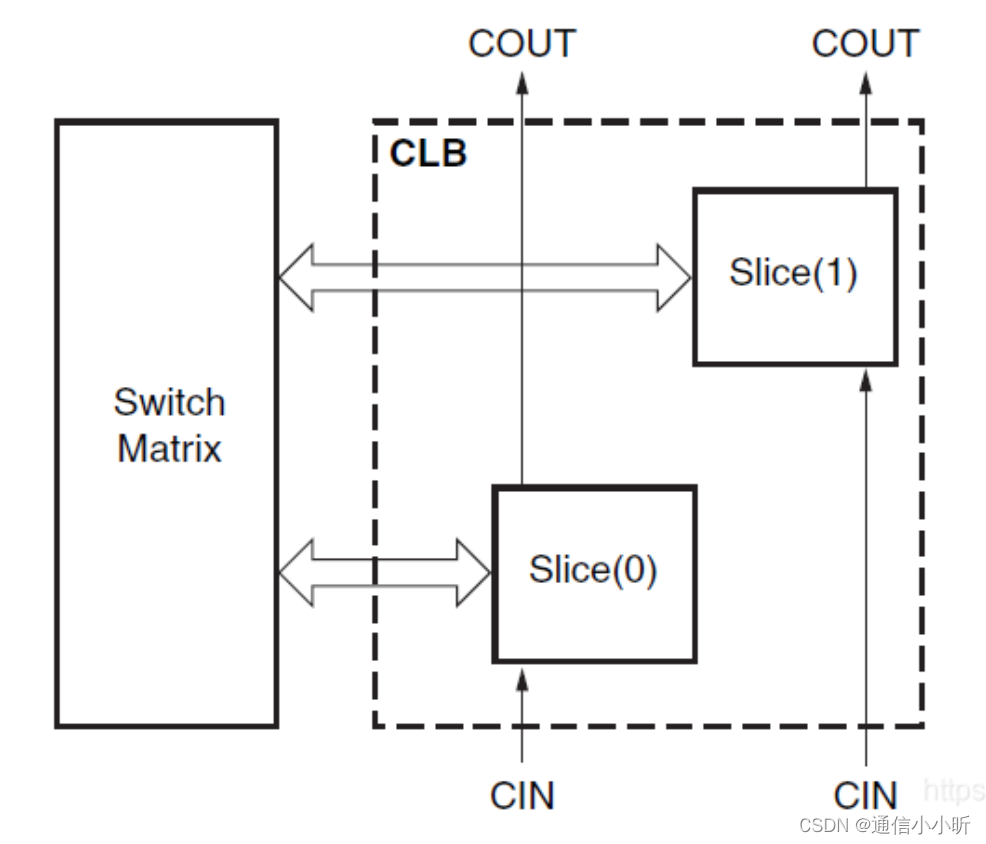

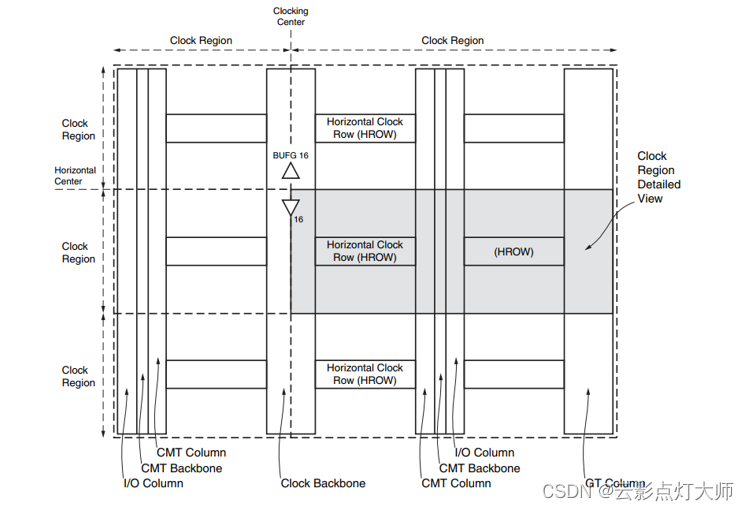

通过一篇文章讲解BUFG、BUFH、BUFR、BUFIO、BUFMR的区别,以及使用方式。总体规律是作用范围越大,延时越大,对于IDDR等时钟一般使用该时钟区域的BUFIO,尽可能减小时钟延时。

要注意各个时钟资源的输入和能够驱动的资源限制,文中每个原语都进行了详细说明,最后还要知道每个bank的时钟管脚。其实最后的时钟资源分布图概括了整篇文章的讲解,只需要理解图21即可。

【惊喜揭秘】xilinx 7系列FPGA时钟区域内部结构大揭秘,让你轻松掌握!

3、原语使用

前文讲解了那么多原语,都没有使用,肯定记不住的,后面几篇文章都使用到了这些原语,可以看看,之后就知道该如何使用这些原语,如何举一反三。

下面这篇文章是HDMI输出图像显示的一个案例,最终需要将单沿传输的10位并行信号转换为双沿采样的串行信号输出,使用ODDR结合用户逻辑完成转换。

对于上面的转换,其实使用OSERDESE会更加方便,不需要其余用户逻辑即可实现,如下所示。

上述案例都只使用了其中一个原语,比较简单,下文是千兆以太网的GMII和RGMII转换模块,RGMII双沿采样、而GMII是单沿采样。

在RGMII转GMII时,使用了IDDR、IDELAYE及IDELAYCTRL原语,为了减小时钟走线延时,IDDR时钟使用了BUFIO原语,同时时钟还要输出给其他模块使用,使用BUFG原语。

在GMII转RGMII时,只使用了ODDR,不使用ODELAYE的原因是HR bank不具有该原语,不好兼容。

基于FPGA的GMII与RGMII接口相互转换(包含源工程文件)

在ISERDESE讲解时也使用了BUFIO和BUFR原语,后续在讲解GT收发器相关知识的时候会涌动差分转单端相关原语,后续在更新相关知识。

如果对文章内容理解有疑惑或者对代码不理解,可以在评论区或者后台留言,看到后均会回复!

如果本文对您有帮助,还请多多点赞👍、评论💬和收藏⭐!您的支持是我更新的最大动力!将持续更新工程!

![[C++初阶]初识C++(二)](https://img-blog.csdnimg.cn/direct/050281efa03947cdb5762431f101d730.png)