配置存储器器件编程

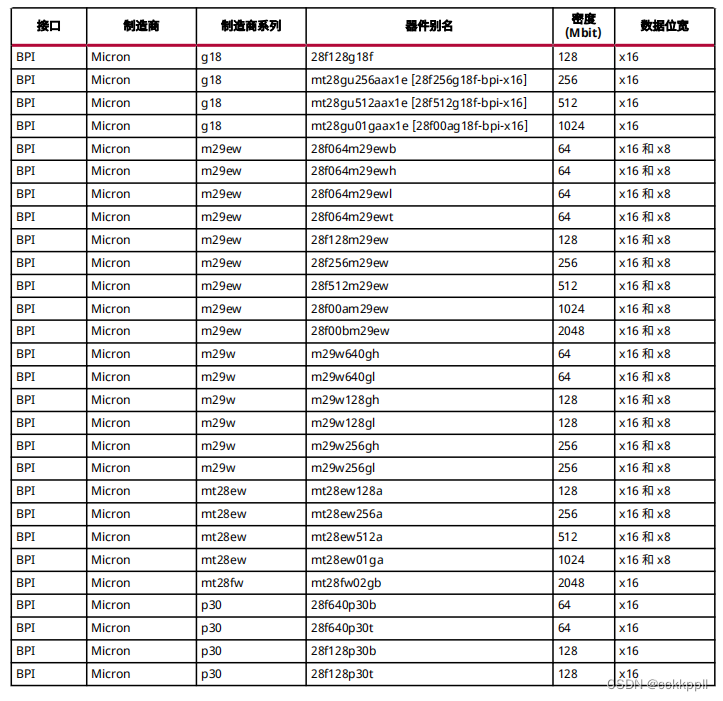

Vivado ® 器件编程器功能支持您直接通过 JTAG 对赛灵思 FPGA 器件进行编程。 Vivado 还可通过 JTAG 对基于闪存的选 定配置存储器器件进行间接编程。具体操作是首先使用特殊配置对赛灵思 FPGA 器件进行编程 , 在 JTAG 与闪存器件接 口之间提供数据路径, 然后使用此数据路径对配置存储器器件内容进行编程。 Vivado 器件配置功能支持您使用赛灵思或 Digilent 电缆来直接配置赛灵思 FPGA 或存储器器件。请参阅“使用 hw_server 连接至硬件目标” , 以获取适用电缆的列表。 Vivado 可采用边界扫描模式运行 , 以便对赛灵思 FPGA 和配 置存储器器件进行配置或编程。

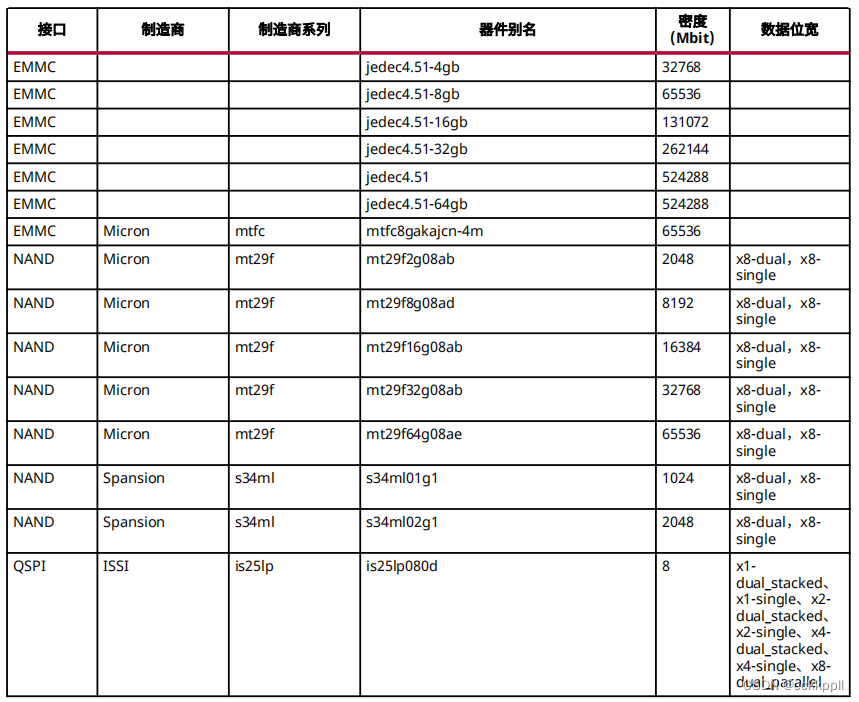

请参阅“ hw_server 支持的 JTAG 线缆和器件” , 以获取受 Vivado 支持的配置存储器器件的完整列表。 要在 Vivado 中从配置存储器器件启动或者对其进行编程 , 请执行以下步骤。

1. 生成比特流 , 用于配置存储器器件。

2. 创建配置存储器文件 ( .mcs 或 .bin ) 。

3. 连接到 Vivado 中的硬件目标。

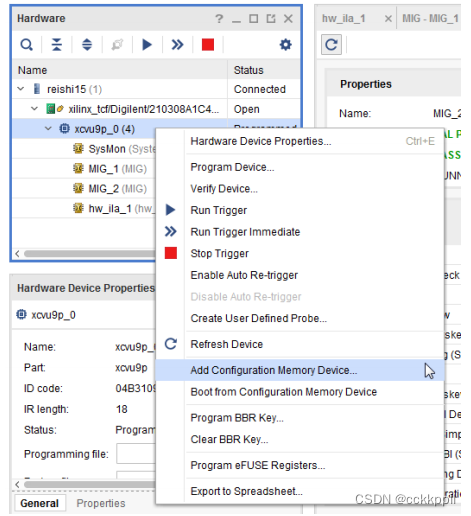

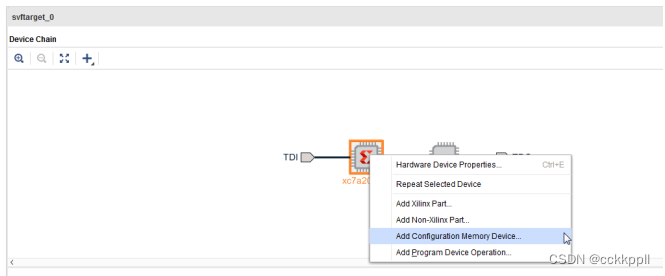

4. 添加配置存储器器件。

5. 使用 Vivado IDE 对配置存储器器件进行编程。

6. 启动 FPGA 器件 ( 可选 ) 。

生成比特流以搭配配置存储器器件使用

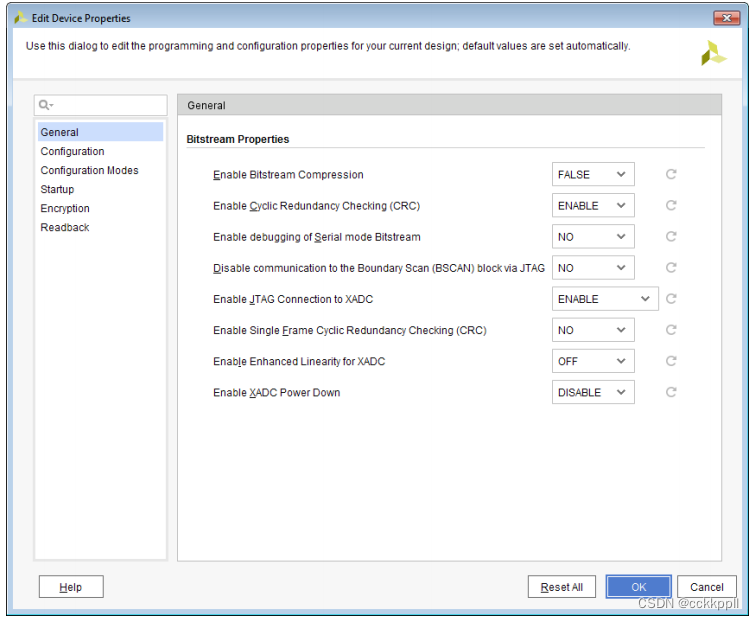

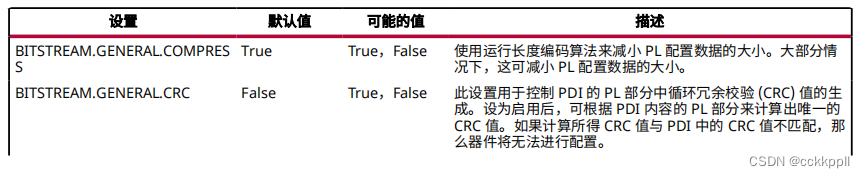

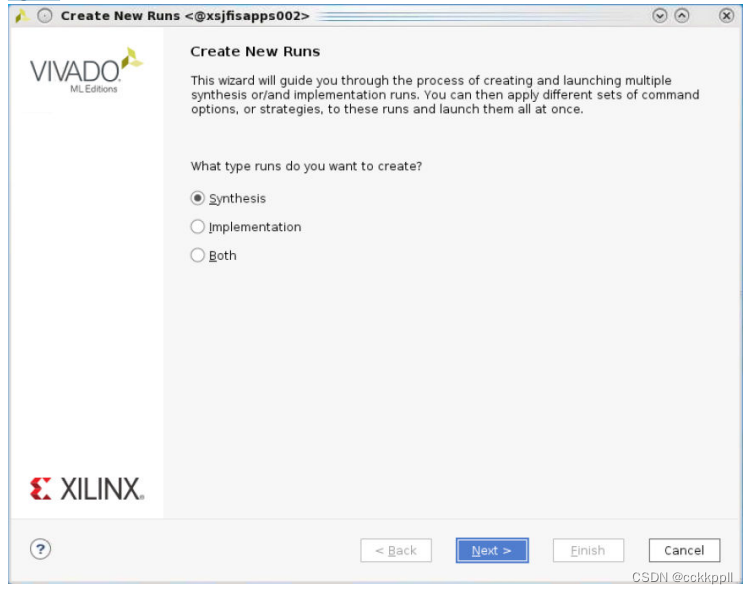

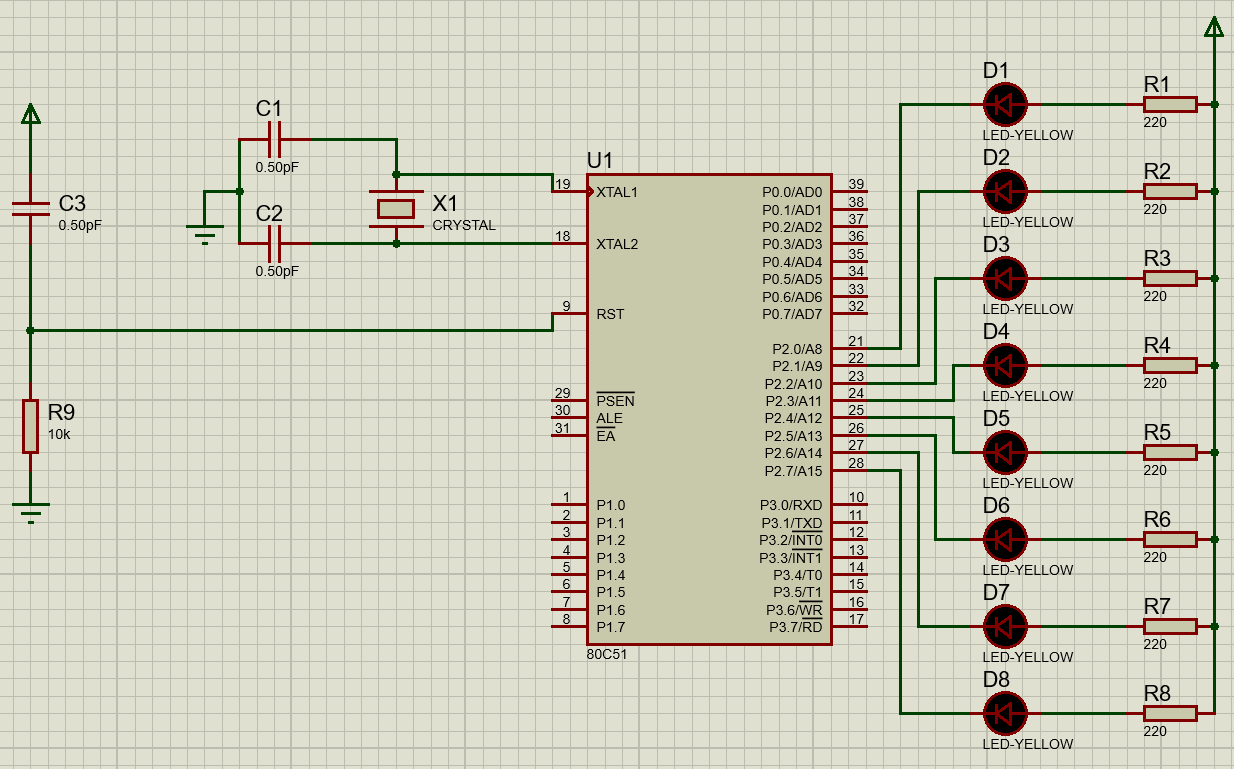

在已综合或已实现的设计中 , 依次选择“ Tools ” → “ Edit Device Properties ”即可打开“编辑器件属性 (Edit Device Properties)”对话框 , 如下所示 在已综合或已实现的设计中, 在 Flow Navigator 中依次选择“ Settings ” → “ Bitstream ” , 然后单击“ Configure additional bitstream”链接设置 , 即可打开“ Edit Device Properties ”对话框 , 如下所示。

使用该对话框左上角的搜索字段即可搜索所有 SPI 或 BPI 相关字段并选择相应的选项设置。请参阅“器件配置比特流或 PDI 设置”以了解有关器件配置设置的更多信息。

创建配置存储器文件 ( 仅适用于 Versal 前的器件 )

使用 write_cfgmem Tcl 命令来创建 .mcs 或 .bin 编程文件。此文件将用于对配置存储器器件进行编程。 例如, 要为单个 1 Gbit BPI 配置存储器器件生成 .mcs 文件 , 请执行以下操作 :

write_cfgmem -format mcs -interface bpix16 -size 128 \ -loadbit "up 0x0 design.bit"-file design.mcs

注释 : write_cfgmem 的 -size 实参以兆字节 (MB) 为单位 , 不同于基于兆位 (Mb) 的闪存器件容量。因此 , 大小为 1 Gbit 的闪存器件换算为 128 MB 提供给以上示例中的 write_cfgmem 。请注意 , write_cfgmem 会根据比特流大 小来自动调整配置存储器文件的大小。

Vivado IDE 支持使用 write_cfgmem 命令将多个 .bit 文件链接在一起。要为包含多个比特流的单个 1 Gbit BPI 配 置存储器器件生成 .mcs 文件 , 请执行以下操作 :

write_cfgmem -format mcs -interface bpix16 -size 128 \

-loadbit "up 0 design1.bit up 0xFFFFF design2.bit" \

-file design1_design2.mcs

如需了解有关 write_cfgmem 命令的更多信息 , 请参阅《 Vivado Design Suite Tcl 命令参考指南》 ( UG835 ) 。

提示 : 您可在 Vivado Lab Edition 中创建配置存储器文件。

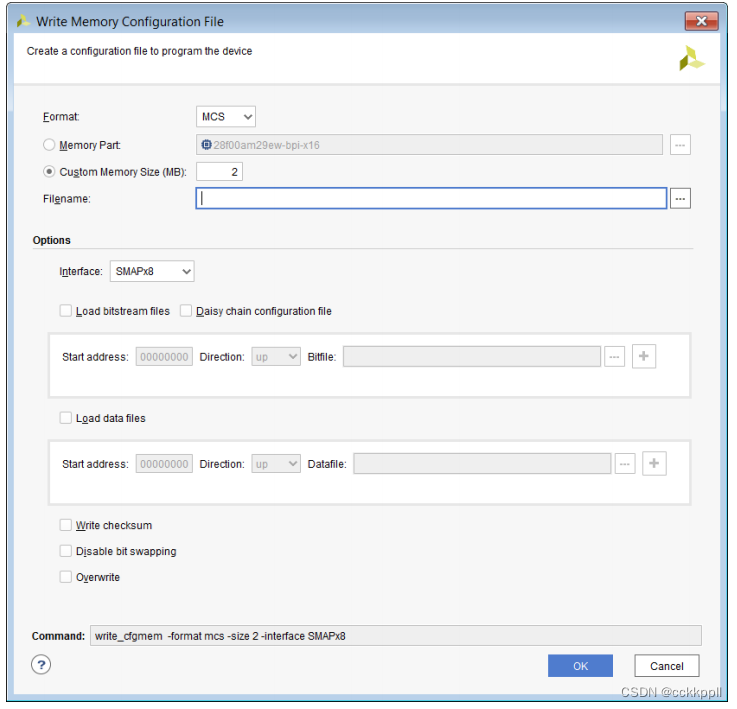

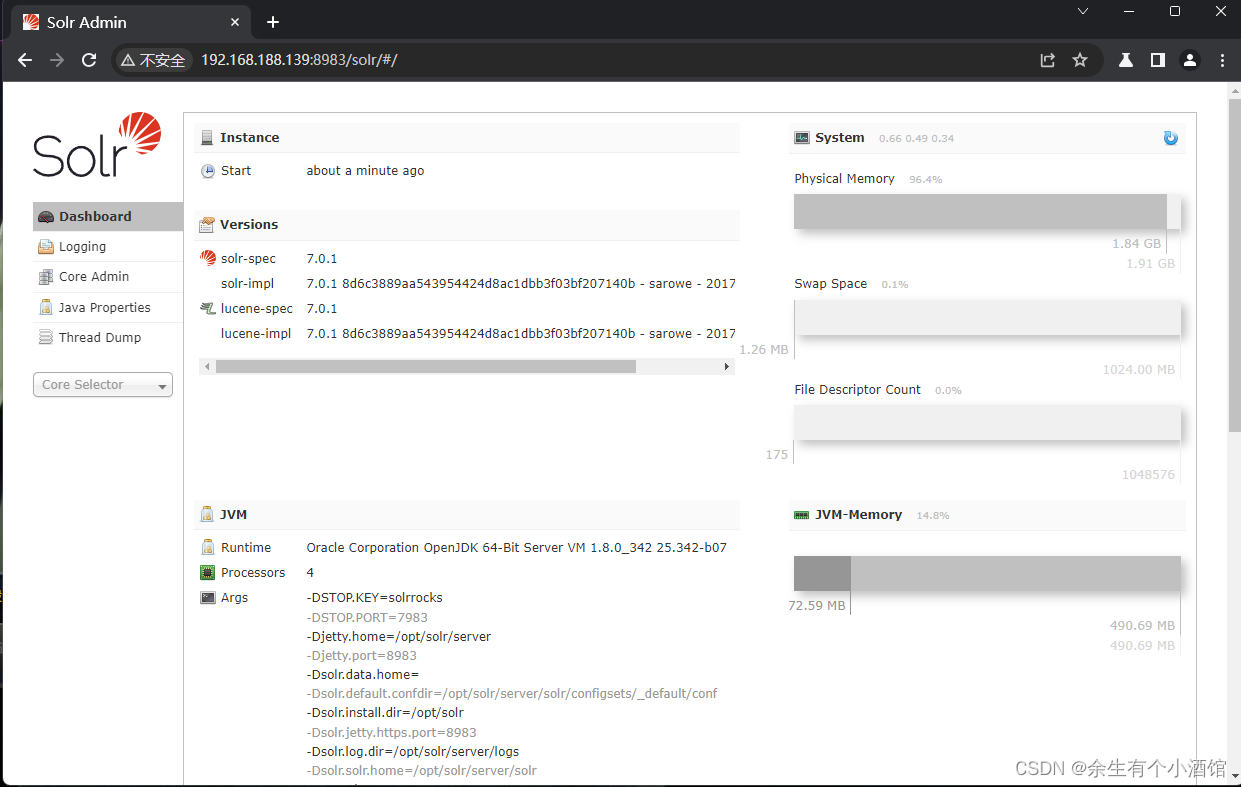

您也可在 Vivado IDE 中创建配置存储器文件。单击“ Tools ” → “ Generate Memory Configuration File ”。这将打开 “编写存储器配置文件 (Write Memory Configuration File) ”对话框 , 如下所示。

选择相应的格式和选项 , 然后单击“ OK ”以生成配置存储器文件。

![[SpringCloud] Feign Client 的创建 (一) (四)](https://img-blog.csdnimg.cn/direct/552bb4fee9314bffa69f91d30344d5bb.png)