URAM存储资源优势

在FPGA中常使用LUTRAM(Distributed RAM)、BRAM(Block RAM)两种片上存储资源。LUTRAM由SLICEM资源派生而来,容量为512b;BRAM容量一般固定36Kb,由RAMBFIFO36资源派生而来,可拆分成两个18Kb BRAM。二者的读延时均较低,基本在1-2个时钟周期(是否使用输出寄存器优化时序)。

随着FPGA计算能力的提高,片上存储资源容量(一般单个仅36Kb,总容量不超过4MB)无法满足高带宽计算的要求,而片外存储资源(如DDR、HBM等)的读写延时较大(一般需要上百时钟周期)无法满足低延时计算的要求。为此,Xilinx自Ultrascale系列开始引入URAM(Ultra RAM)存储资源,该资源容量为288Kb,读延时较低,在不使用级联的情况下,基本保持在1-2个时钟周期(是否使用输出寄存器优化时序)。

使用方法

本文介绍三种使用URAM存储资源的方式:

在具有URAM的FPGA上可通过使用URAM READ BACK IP核进行URAM例化,可参考相关IP产品手册,不多赘述,需要注意的是这种方式仅能例化单个URAM,无法简单进行URAM级联。

xpm_memory原语通过配置memory_type参数为ultra可使用URAM,类似于Distributed RAM、BRAM类型的使用方法,本文不多赘述。

本文重点介绍URAM原语的使用,该原语声明如下,在Ultrascale+及之前系列中,URAM288的位宽固定为72,深度固定为4K,相比BRAM配置灵活度较低:

URAM288_BASE #(

.AUTO_SLEEP_LATENCY(8), // Latency requirement to enter sleep mode

.AVG_CONS_INACTIVE_CYCLES(10), // Average consecutive inactive cycles when is SLEEP mode for power

// estimation

.BWE_MODE_A("PARITY_INTERLEAVED"), // Port A Byte write control

.BWE_MODE_B("PARITY_INTERLEAVED"), // Port B Byte write control

.EN_AUTO_SLEEP_MODE("FALSE"), // Enable to automatically enter sleep mode

.EN_ECC_RD_A("FALSE"), // Port A ECC encoder

.EN_ECC_RD_B("FALSE"), // Port B ECC encoder

.EN_ECC_WR_A("FALSE"), // Port A ECC decoder

.EN_ECC_WR_B("FALSE"), // Port B ECC decoder

.IREG_PRE_A("FALSE"), // Optional Port A input pipeline registers

.IREG_PRE_B("FALSE"), // Optional Port B input pipeline registers

.IS_CLK_INVERTED(1'b0), // Optional inverter for CLK

.IS_EN_A_INVERTED(1'b0), // Optional inverter for Port A enable

.IS_EN_B_INVERTED(1'b0), // Optional inverter for Port B enable

.IS_RDB_WR_A_INVERTED(1'b0), // Optional inverter for Port A read/write select

.IS_RDB_WR_B_INVERTED(1'b0), // Optional inverter for Port B read/write select

.IS_RST_A_INVERTED(1'b0), // Optional inverter for Port A reset

.IS_RST_B_INVERTED(1'b0), // Optional inverter for Port B reset

.OREG_A("FALSE"), // Optional Port A output pipeline registers

.OREG_B("FALSE"), // Optional Port B output pipeline registers

.OREG_ECC_A("FALSE"), // Port A ECC decoder output

.OREG_ECC_B("FALSE"), // Port B output ECC decoder

.RST_MODE_A("SYNC"), // Port A reset mode

.RST_MODE_B("SYNC"), // Port B reset mode

.USE_EXT_CE_A("FALSE"), // Enable Port A external CE inputs for output registers

.USE_EXT_CE_B("FALSE") // Enable Port B external CE inputs for output registers

)

URAM288_BASE_inst (

.DBITERR_A(DBITERR_A), // 1-bit output: Port A double-bit error flag status

.DBITERR_B(DBITERR_B), // 1-bit output: Port B double-bit error flag status

.DOUT_A(DOUT_A), // 72-bit output: Port A read data output

.DOUT_B(DOUT_B), // 72-bit output: Port B read data output

.SBITERR_A(SBITERR_A), // 1-bit output: Port A single-bit error flag status

.SBITERR_B(SBITERR_B), // 1-bit output: Port B single-bit error flag status

.ADDR_A(ADDR_A), // 23-bit input: Port A address

.ADDR_B(ADDR_B), // 23-bit input: Port B address

.BWE_A(BWE_A), // 9-bit input: Port A Byte-write enable

.BWE_B(BWE_B), // 9-bit input: Port B Byte-write enable

.CLK(CLK), // 1-bit input: Clock source

.DIN_A(DIN_A), // 72-bit input: Port A write data input

.DIN_B(DIN_B), // 72-bit input: Port B write data input

.EN_A(EN_A), // 1-bit input: Port A enable

.EN_B(EN_B), // 1-bit input: Port B enable

.INJECT_DBITERR_A(INJECT_DBITERR_A), // 1-bit input: Port A double-bit error injection

.INJECT_DBITERR_B(INJECT_DBITERR_B), // 1-bit input: Port B double-bit error injection

.INJECT_SBITERR_A(INJECT_SBITERR_A), // 1-bit input: Port A single-bit error injection

.INJECT_SBITERR_B(INJECT_SBITERR_B), // 1-bit input: Port B single-bit error injection

.OREG_CE_A(OREG_CE_A), // 1-bit input: Port A output register clock enable

.OREG_CE_B(OREG_CE_B), // 1-bit input: Port B output register clock enable

.OREG_ECC_CE_A(OREG_ECC_CE_A), // 1-bit input: Port A ECC decoder output register clock enable

.OREG_ECC_CE_B(OREG_ECC_CE_B), // 1-bit input: Port B ECC decoder output register clock enable

.RDB_WR_A(RDB_WR_A), // 1-bit input: Port A read/write select

.RDB_WR_B(RDB_WR_B), // 1-bit input: Port B read/write select

.RST_A(RST_A), // 1-bit input: Port A asynchronous or synchronous reset for output

// registers

.RST_B(RST_B), // 1-bit input: Port B asynchronous or synchronous reset for output

// registers

.SLEEP(SLEEP) // 1-bit input: Dynamic power gating control

);

在实际使用时,URAM的使用方式与BRAM相似,需要注意的是,URAM不同于BRAM,必须使用复位信号复位后方能进行使用,复位过程需要保证未进行写操作。

级联

与BRAM一样,在需要时,URAM可以通过使用专用布线级联的方式增加容量。级联需要注意参数配置和端口的连接关系,此外在级联状态下,读周期会相应延长,在不需要拓展位宽,需要拓展深度时的一维级联的代码如下:

`timescale 1ns / 1ps

//

// Company:

// Engineer: wjh776a68

//

// Create Date: 03/22/2023 10:35:33 PM

// Design Name:

// Module Name: uram72

// Project Name:

// Target Devices: xcvu37p

// Tool Versions: 2022.2

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module uram72 # (

parameter cascade_level = 6,

parameter addr_mask = 11'h7f8

) (

input clk,

output wire [71:0] DOUT_A,

output wire [71:0] DOUT_B,

output wire RDACCESS_A,

output wire RDACCESS_B,

input [22:0] ADDR_A,

input [22:0] ADDR_B,

input [8:0] BWE_A,

input [8:0] BWE_B,

input [71:0] DIN_A,

input [71:0] DIN_B,

input RDB_WR_A,

input RDB_WR_B,

input EN_A,

input EN_B

// input rst

);

// 7 uram casade to save one row of output of systolic array (226*226*32).

// 64 * (2 ^ 12) * 7 - 226 * 226 * 32 >= 0

logic [23 - 1 : 0] CAS_ADDR_A[cascade_level:0];

logic [23 - 1 : 0] CAS_ADDR_B[cascade_level:0];

logic [9 - 1 : 0] CAS_BWE_A[cascade_level:0];

logic [9 - 1 : 0] CAS_BWE_B[cascade_level:0];

logic [1 - 1 : 0] CAS_DBITERR_A[cascade_level:0];

logic [1 - 1 : 0] CAS_DBITERR_B[cascade_level:0];

logic [72 - 1 : 0] CAS_DIN_A[cascade_level:0];

logic [72 - 1 : 0] CAS_DIN_B[cascade_level:0];

logic [72 - 1 : 0] CAS_DOUT_A[cascade_level:0];

logic [72 - 1 : 0] CAS_DOUT_B[cascade_level:0];

logic [1 - 1 : 0] CAS_EN_A[cascade_level:0];

logic [1 - 1 : 0] CAS_EN_B[cascade_level:0];

logic [1 - 1 : 0] CAS_RDACCESS_A[cascade_level:0];

logic [1 - 1 : 0] CAS_RDACCESS_B[cascade_level:0];

logic [1 - 1 : 0] CAS_RDB_WR_A[cascade_level:0];

logic [1 - 1 : 0] CAS_RDB_WR_B[cascade_level:0];

logic [1 - 1 : 0] CAS_SBITERR_A[cascade_level:0];

logic [1 - 1 : 0] CAS_SBITERR_B[cascade_level:0];

logic [1 - 1 : 0] CAS_RST [cascade_level:0];

assign CAS_ADDR_A[0] = 0;

assign CAS_ADDR_B[0] = 0;

assign CAS_BWE_A[0] = 0;

assign CAS_BWE_B[0] = 0;

assign CAS_DBITERR_A[0] = 0;

assign CAS_DBITERR_B[0] = 0;

assign CAS_DIN_A[0] = 0;

assign CAS_DIN_B[0] = 0;

assign CAS_DOUT_A[0] = 0;

assign CAS_DOUT_B[0] = 0;

assign CAS_EN_A[0] = 0;

assign CAS_EN_B[0] = 0;

assign CAS_RDACCESS_A[0] = 0;

assign CAS_RDACCESS_B[0] = 0;

assign CAS_RDB_WR_A[0] = 0;

assign CAS_RDB_WR_B[0] = 0;

assign CAS_SBITERR_A[0] = 0;

assign CAS_SBITERR_B[0] = 0;

// assign CAS_RST[0] = rst;

/* always_ff @(posedge clk) begin

CAS_RST[cascade_level:0] <= {CAS_RST[cascade_level - 1:0], rst};

end */

generate

for (genvar i = 0; i < cascade_level + 1; i++) begin

assign CAS_RST[i] = 0;

end

endgenerate

generate

for (genvar i = 0; i < cascade_level; i++) begin : uram_cascade

if (i == 0) begin

URAM288 #(

.AUTO_SLEEP_LATENCY(8), // Latency requirement to enter sleep mode

.AVG_CONS_INACTIVE_CYCLES(10), // Average consecutive inactive cycles when is SLEEP mode for power

// estimation

.BWE_MODE_A("PARITY_INDEPENDENT"), // Port A Byte write control

.BWE_MODE_B("PARITY_INDEPENDENT"), // Port B Byte write control

.CASCADE_ORDER_A("FIRST"), // Port A position in cascade chain

.CASCADE_ORDER_B("FIRST"), // Port B position in cascade chain

.EN_AUTO_SLEEP_MODE("FALSE"), // Enable to automatically enter sleep mode

.EN_ECC_RD_A("FALSE"), // Port A ECC encoder

.EN_ECC_RD_B("FALSE"), // Port B ECC encoder

.EN_ECC_WR_A("FALSE"), // Port A ECC decoder

.EN_ECC_WR_B("FALSE"), // Port B ECC decoder

.IREG_PRE_A("TRUE"), // Optional Port A input pipeline registers

.IREG_PRE_B("TRUE"), // Optional Port B input pipeline registers

.IS_CLK_INVERTED(1'b0), // Optional inverter for CLK

.IS_EN_A_INVERTED(1'b0), // Optional inverter for Port A enable

.IS_EN_B_INVERTED(1'b0), // Optional inverter for Port B enable

.IS_RDB_WR_A_INVERTED(1'b0), // Optional inverter for Port A read/write select

.IS_RDB_WR_B_INVERTED(1'b0), // Optional inverter for Port B read/write select

.IS_RST_A_INVERTED(1'b0), // Optional inverter for Port A reset

.IS_RST_B_INVERTED(1'b0), // Optional inverter for Port B reset

.OREG_A("TRUE"), // Optional Port A output pipeline registers

.OREG_B("TRUE"), // Optional Port B output pipeline registers

.OREG_ECC_A("FALSE"), // Port A ECC decoder output

.OREG_ECC_B("FALSE"), // Port B output ECC decoder

.REG_CAS_A("FALSE"), // Optional Port A cascade register

.REG_CAS_B("FALSE"), // Optional Port B cascade register

.RST_MODE_A("SYNC"), // Port A reset mode

.RST_MODE_B("SYNC"), // Port B reset mode

.SELF_ADDR_A(11'h000), // Port A self-address value

.SELF_ADDR_B(11'h000), // Port B self-address value

.SELF_MASK_A(addr_mask), // Port A self-address mask

.SELF_MASK_B(addr_mask), // Port B self-address mask

.USE_EXT_CE_A("FALSE"), // Enable Port A external CE inputs for output registers

.USE_EXT_CE_B("FALSE") // Enable Port B external CE inputs for output registers

)

URAM288_inst (

.CAS_OUT_ADDR_A(CAS_ADDR_A[i + 1]), // 23-bit output: Port A cascade output address

.CAS_OUT_ADDR_B(CAS_ADDR_B[i + 1]), // 23-bit output: Port B cascade output address

.CAS_OUT_BWE_A(CAS_BWE_A[i + 1]), // 9-bit output: Port A cascade Byte-write enable output

.CAS_OUT_BWE_B(CAS_BWE_B[i + 1]), // 9-bit output: Port B cascade Byte-write enable output

.CAS_OUT_DBITERR_A(CAS_DBITERR_A[i + 1]), // 1-bit output: Port A cascade double-bit error flag output

.CAS_OUT_DBITERR_B(CAS_DBITERR_B[i + 1]), // 1-bit output: Port B cascade double-bit error flag output

.CAS_OUT_DIN_A(CAS_DIN_A[i + 1]), // 72-bit output: Port A cascade output write mode data

.CAS_OUT_DIN_B(CAS_DIN_B[i + 1]), // 72-bit output: Port B cascade output write mode data

.CAS_OUT_DOUT_A(CAS_DOUT_A[i + 1]), // 72-bit output: Port A cascade output read mode data

.CAS_OUT_DOUT_B(CAS_DOUT_B[i + 1]), // 72-bit output: Port B cascade output read mode data

.CAS_OUT_EN_A(CAS_EN_A[i + 1]), // 1-bit output: Port A cascade output enable

.CAS_OUT_EN_B(CAS_EN_B[i + 1]), // 1-bit output: Port B cascade output enable

.CAS_OUT_RDACCESS_A(CAS_RDACCESS_A[i + 1]), // 1-bit output: Port A cascade read status output

.CAS_OUT_RDACCESS_B(CAS_RDACCESS_B[i + 1]), // 1-bit output: Port B cascade read status output

.CAS_OUT_RDB_WR_A(CAS_RDB_WR_A[i + 1]), // 1-bit output: Port A cascade read/write select output

.CAS_OUT_RDB_WR_B(CAS_RDB_WR_B[i + 1]), // 1-bit output: Port B cascade read/write select output

.CAS_OUT_SBITERR_A(CAS_SBITERR_A[i + 1]), // 1-bit output: Port A cascade single-bit error flag output

.CAS_OUT_SBITERR_B(CAS_SBITERR_B[i + 1]), // 1-bit output: Port B cascade single-bit error flag output

.ADDR_A(ADDR_A), // 23-bit input: Port A address

.ADDR_B(ADDR_B), // 23-bit input: Port B address

.BWE_A(BWE_A), // 9-bit input: Port A Byte-write enable

.BWE_B(BWE_B), // 9-bit input: Port B Byte-write enable

.CAS_IN_ADDR_A(CAS_ADDR_A[i]), // 23-bit input: Port A cascade input address

.CAS_IN_ADDR_B(CAS_ADDR_B[i]), // 23-bit input: Port B cascade input address

.CAS_IN_BWE_A(CAS_BWE_A[i]), // 9-bit input: Port A cascade Byte-write enable input

.CAS_IN_BWE_B(CAS_BWE_B[i]), // 9-bit input: Port B cascade Byte-write enable input

.CAS_IN_DBITERR_A(CAS_DBITERR_A[i]), // 1-bit input: Port A cascade double-bit error flag input

.CAS_IN_DBITERR_B(CAS_DBITERR_B[i]), // 1-bit input: Port B cascade double-bit error flag input

.CAS_IN_DIN_A(CAS_DIN_A[i]), // 72-bit input: Port A cascade input write mode data

.CAS_IN_DIN_B(CAS_DIN_B[i]), // 72-bit input: Port B cascade input write mode data

.CAS_IN_DOUT_A(CAS_DOUT_A[i]), // 72-bit input: Port A cascade input read mode data

.CAS_IN_DOUT_B(CAS_DOUT_B[i]), // 72-bit input: Port B cascade input read mode data

.CAS_IN_EN_A(CAS_EN_A[i]), // 1-bit input: Port A cascade enable input

.CAS_IN_EN_B(CAS_EN_B[i]), // 1-bit input: Port B cascade enable input

.CAS_IN_RDACCESS_A(CAS_RDACCESS_A[i]), // 1-bit input: Port A cascade read status input

.CAS_IN_RDACCESS_B(CAS_RDACCESS_B[i]), // 1-bit input: Port B cascade read status input

.CAS_IN_RDB_WR_A(CAS_RDB_WR_A[i]), // 1-bit input: Port A cascade read/write select input

.CAS_IN_RDB_WR_B(CAS_RDB_WR_B[i]), // 1-bit input: Port B cascade read/write select input

.CAS_IN_SBITERR_A(CAS_SBITERR_A[i]), // 1-bit input: Port A cascade single-bit error flag input

.CAS_IN_SBITERR_B(CAS_SBITERR_B[i]), // 1-bit input: Port B cascade single-bit error flag input

.CLK(clk), // 1-bit input: Clock source

.DIN_A(DIN_A), // 72-bit input: Port A write data input

.DIN_B(DIN_B), // 72-bit input: Port B write data input

.EN_A(EN_A), // 1-bit input: Port A enable

.EN_B(EN_B), // 1-bit input: Port B enable

.INJECT_DBITERR_A(1'b0), // 1-bit input: Port A double-bit error injection

.INJECT_DBITERR_B(1'b0), // 1-bit input: Port B double-bit error injection

.INJECT_SBITERR_A(1'b0), // 1-bit input: Port A single-bit error injection

.INJECT_SBITERR_B(1'b0), // 1-bit input: Port B single-bit error injection

.OREG_CE_A(1'b1), // 1-bit input: Port A output register clock enable

.OREG_CE_B(1'b1), // 1-bit input: Port B output register clock enable

.OREG_ECC_CE_A(1'b1), // 1-bit input: Port A ECC decoder output register clock enable

.OREG_ECC_CE_B(1'b1), // 1-bit input: Port B ECC decoder output register clock enable

.RDB_WR_A(RDB_WR_A), // 1-bit input: Port A read/write select

.RDB_WR_B(RDB_WR_B), // 1-bit input: Port B read/write select

.RST_A(CAS_RST[i]), // 1-bit input: Port A asynchronous or synchronous reset for

// output registers

.RST_B(CAS_RST[i]), // 1-bit input: Port B asynchronous or synchronous reset for

// output registers

.SLEEP(1'b0) // 1-bit input: Dynamic power gating control

);

end

else if (i == cascade_level - 1) begin

URAM288 #(

.AUTO_SLEEP_LATENCY(8), // Latency requirement to enter sleep mode

.AVG_CONS_INACTIVE_CYCLES(10), // Average consecutive inactive cycles when is SLEEP mode for power

// estimation

.BWE_MODE_A("PARITY_INDEPENDENT"), // Port A Byte write control

.BWE_MODE_B("PARITY_INDEPENDENT"), // Port B Byte write control

.CASCADE_ORDER_A("LAST"), // Port A position in cascade chain

.CASCADE_ORDER_B("LAST"), // Port B position in cascade chain

.EN_AUTO_SLEEP_MODE("FALSE"), // Enable to automatically enter sleep mode

.EN_ECC_RD_A("FALSE"), // Port A ECC encoder

.EN_ECC_RD_B("FALSE"), // Port B ECC encoder

.EN_ECC_WR_A("FALSE"), // Port A ECC decoder

.EN_ECC_WR_B("FALSE"), // Port B ECC decoder

.IREG_PRE_A("FALSE"), // Optional Port A input pipeline registers

.IREG_PRE_B("FALSE"), // Optional Port B input pipeline registers

.IS_CLK_INVERTED(1'b0), // Optional inverter for CLK

.IS_EN_A_INVERTED(1'b0), // Optional inverter for Port A enable

.IS_EN_B_INVERTED(1'b0), // Optional inverter for Port B enable

.IS_RDB_WR_A_INVERTED(1'b0), // Optional inverter for Port A read/write select

.IS_RDB_WR_B_INVERTED(1'b0), // Optional inverter for Port B read/write select

.IS_RST_A_INVERTED(1'b0), // Optional inverter for Port A reset

.IS_RST_B_INVERTED(1'b0), // Optional inverter for Port B reset

.OREG_A("TRUE"), // Optional Port A output pipeline registers

.OREG_B("TRUE"), // Optional Port B output pipeline registers

.OREG_ECC_A("FALSE"), // Port A ECC decoder output

.OREG_ECC_B("FALSE"), // Port B output ECC decoder

.REG_CAS_A("TRUE"), // Optional Port A cascade register

.REG_CAS_B("TRUE"), // Optional Port B cascade register

.RST_MODE_A("SYNC"), // Port A reset mode

.RST_MODE_B("SYNC"), // Port B reset mode

.SELF_ADDR_A(i), // Port A self-address value

.SELF_ADDR_B(i), // Port B self-address value

.SELF_MASK_A(addr_mask), // Port A self-address mask

.SELF_MASK_B(addr_mask), // Port B self-address mask

.USE_EXT_CE_A("FALSE"), // Enable Port A external CE inputs for output registers

.USE_EXT_CE_B("FALSE") // Enable Port B external CE inputs for output registers

)

URAM288_inst (

.CAS_OUT_ADDR_A(CAS_ADDR_A[i + 1]), // 23-bit output: Port A cascade output address

.CAS_OUT_ADDR_B(CAS_ADDR_B[i + 1]), // 23-bit output: Port B cascade output address

.CAS_OUT_BWE_A(CAS_BWE_A[i + 1]), // 9-bit output: Port A cascade Byte-write enable output

.CAS_OUT_BWE_B(CAS_BWE_B[i + 1]), // 9-bit output: Port B cascade Byte-write enable output

.CAS_OUT_DBITERR_A(CAS_DBITERR_A[i + 1]), // 1-bit output: Port A cascade double-bit error flag output

.CAS_OUT_DBITERR_B(CAS_DBITERR_B[i + 1]), // 1-bit output: Port B cascade double-bit error flag output

.CAS_OUT_DIN_A(CAS_DIN_A[i + 1]), // 72-bit output: Port A cascade output write mode data

.CAS_OUT_DIN_B(CAS_DIN_B[i + 1]), // 72-bit output: Port B cascade output write mode data

.CAS_OUT_DOUT_A(CAS_DOUT_A[i + 1]), // 72-bit output: Port A cascade output read mode data

.CAS_OUT_DOUT_B(CAS_DOUT_B[i + 1]), // 72-bit output: Port B cascade output read mode data

.CAS_OUT_EN_A(CAS_EN_A[i + 1]), // 1-bit output: Port A cascade output enable

.CAS_OUT_EN_B(CAS_EN_B[i + 1]), // 1-bit output: Port B cascade output enable

.CAS_OUT_RDACCESS_A(CAS_RDACCESS_A[i + 1]), // 1-bit output: Port A cascade read status output

.CAS_OUT_RDACCESS_B(CAS_RDACCESS_B[i + 1]), // 1-bit output: Port B cascade read status output

.CAS_OUT_RDB_WR_A(CAS_RDB_WR_A[i + 1]), // 1-bit output: Port A cascade read/write select output

.CAS_OUT_RDB_WR_B(CAS_RDB_WR_B[i + 1]), // 1-bit output: Port B cascade read/write select output

.CAS_OUT_SBITERR_A(CAS_SBITERR_A[i + 1]), // 1-bit output: Port A cascade single-bit error flag output

.CAS_OUT_SBITERR_B(CAS_SBITERR_B[i + 1]), // 1-bit output: Port B cascade single-bit error flag output

.DOUT_A(DOUT_A), // 72-bit output: Port A read data output

.DOUT_B(DOUT_B), // 72-bit output: Port B read data output

.RDACCESS_A(RDACCESS_A), // 1-bit output: Port A read status

.RDACCESS_B(RDACCESS_B), // 1-bit output: Port B read status

.ADDR_A({23{1'b1}}), // 23-bit input: Port A address

.ADDR_B({23{1'b1}}), // 23-bit input: Port B address

.BWE_A({9{1'b1}}), // 9-bit input: Port A Byte-write enable

.BWE_B({9{1'b1}}), // 9-bit input: Port B Byte-write enable

.CAS_IN_ADDR_A(CAS_ADDR_A[i]), // 23-bit input: Port A cascade input address

.CAS_IN_ADDR_B(CAS_ADDR_B[i]), // 23-bit input: Port B cascade input address

.CAS_IN_BWE_A(CAS_BWE_A[i]), // 9-bit input: Port A cascade Byte-write enable input

.CAS_IN_BWE_B(CAS_BWE_B[i]), // 9-bit input: Port B cascade Byte-write enable input

.CAS_IN_DBITERR_A(CAS_DBITERR_A[i]), // 1-bit input: Port A cascade double-bit error flag input

.CAS_IN_DBITERR_B(CAS_DBITERR_B[i]), // 1-bit input: Port B cascade double-bit error flag input

.CAS_IN_DIN_A(CAS_DIN_A[i]), // 72-bit input: Port A cascade input write mode data

.CAS_IN_DIN_B(CAS_DIN_B[i]), // 72-bit input: Port B cascade input write mode data

.CAS_IN_DOUT_A(CAS_DOUT_A[i]), // 72-bit input: Port A cascade input read mode data

.CAS_IN_DOUT_B(CAS_DOUT_B[i]), // 72-bit input: Port B cascade input read mode data

.CAS_IN_EN_A(CAS_EN_A[i]), // 1-bit input: Port A cascade enable input

.CAS_IN_EN_B(CAS_EN_B[i]), // 1-bit input: Port B cascade enable input

.CAS_IN_RDACCESS_A(CAS_RDACCESS_A[i]), // 1-bit input: Port A cascade read status input

.CAS_IN_RDACCESS_B(CAS_RDACCESS_B[i]), // 1-bit input: Port B cascade read status input

.CAS_IN_RDB_WR_A(CAS_RDB_WR_A[i]), // 1-bit input: Port A cascade read/write select input

.CAS_IN_RDB_WR_B(CAS_RDB_WR_B[i]), // 1-bit input: Port B cascade read/write select input

.CAS_IN_SBITERR_A(CAS_SBITERR_A[i]), // 1-bit input: Port A cascade single-bit error flag input

.CAS_IN_SBITERR_B(CAS_SBITERR_B[i]), // 1-bit input: Port B cascade single-bit error flag input

.CLK(clk), // 1-bit input: Clock source

.DIN_A({72{1'b1}}), // 72-bit input: Port A write data input

.DIN_B({72{1'b1}}), // 72-bit input: Port B write data input

.EN_A(1'b1), // 1-bit input: Port A enable

.EN_B(1'b1), // 1-bit input: Port B enable

.INJECT_DBITERR_A(1'b0), // 1-bit input: Port A double-bit error injection

.INJECT_DBITERR_B(1'b0), // 1-bit input: Port B double-bit error injection

.INJECT_SBITERR_A(1'b0), // 1-bit input: Port A single-bit error injection

.INJECT_SBITERR_B(1'b0), // 1-bit input: Port B single-bit error injection

.OREG_CE_A(1'b1), // 1-bit input: Port A output register clock enable

.OREG_CE_B(1'b1), // 1-bit input: Port B output register clock enable

.OREG_ECC_CE_A(1'b1), // 1-bit input: Port A ECC decoder output register clock enable

.OREG_ECC_CE_B(1'b1), // 1-bit input: Port B ECC decoder output register clock enable

.RDB_WR_A(1'b1), // 1-bit input: Port A read/write select

.RDB_WR_B(1'b1), // 1-bit input: Port B read/write select

.RST_A(CAS_RST[i]), // 1-bit input: Port A asynchronous or synchronous reset for

// output registers

.RST_B(CAS_RST[i]), // 1-bit input: Port B asynchronous or synchronous reset for

// output registers

.SLEEP(1'b0) // 1-bit input: Dynamic power gating control

);

end

else begin

URAM288 #(

.AUTO_SLEEP_LATENCY(8), // Latency requirement to enter sleep mode

.AVG_CONS_INACTIVE_CYCLES(10), // Average consecutive inactive cycles when is SLEEP mode for power

// estimation

.BWE_MODE_A("PARITY_INDEPENDENT"), // Port A Byte write control

.BWE_MODE_B("PARITY_INDEPENDENT"), // Port B Byte write control

.CASCADE_ORDER_A("MIDDLE"), // Port A position in cascade chain

.CASCADE_ORDER_B("MIDDLE"), // Port B position in cascade chain

.EN_AUTO_SLEEP_MODE("FALSE"), // Enable to automatically enter sleep mode

.EN_ECC_RD_A("FALSE"), // Port A ECC encoder

.EN_ECC_RD_B("FALSE"), // Port B ECC encoder

.EN_ECC_WR_A("FALSE"), // Port A ECC decoder

.EN_ECC_WR_B("FALSE"), // Port B ECC decoder

.IREG_PRE_A("FALSE"), // Optional Port A input pipeline registers

.IREG_PRE_B("FALSE"), // Optional Port B input pipeline registers

.IS_CLK_INVERTED(1'b0), // Optional inverter for CLK

.IS_EN_A_INVERTED(1'b0), // Optional inverter for Port A enable

.IS_EN_B_INVERTED(1'b0), // Optional inverter for Port B enable

.IS_RDB_WR_A_INVERTED(1'b0), // Optional inverter for Port A read/write select

.IS_RDB_WR_B_INVERTED(1'b0), // Optional inverter for Port B read/write select

.IS_RST_A_INVERTED(1'b0), // Optional inverter for Port A reset

.IS_RST_B_INVERTED(1'b0), // Optional inverter for Port B reset

.OREG_A("TRUE"), // Optional Port A output pipeline registers

.OREG_B("TRUE"), // Optional Port B output pipeline registers

.OREG_ECC_A("FALSE"), // Port A ECC decoder output

.OREG_ECC_B("FALSE"), // Port B output ECC decoder

.REG_CAS_A("TRUE"), // Optional Port A cascade register

.REG_CAS_B("TRUE"), // Optional Port B cascade register

.RST_MODE_A("SYNC"), // Port A reset mode

.RST_MODE_B("SYNC"), // Port B reset mode

.SELF_ADDR_A(i), // Port A self-address value

.SELF_ADDR_B(i), // Port B self-address value

.SELF_MASK_A(addr_mask), // Port A self-address mask

.SELF_MASK_B(addr_mask), // Port B self-address mask

.USE_EXT_CE_A("FALSE"), // Enable Port A external CE inputs for output registers

.USE_EXT_CE_B("FALSE") // Enable Port B external CE inputs for output registers

)

URAM288_inst (

.CAS_OUT_ADDR_A(CAS_ADDR_A[i + 1]), // 23-bit output: Port A cascade output address

.CAS_OUT_ADDR_B(CAS_ADDR_B[i + 1]), // 23-bit output: Port B cascade output address

.CAS_OUT_BWE_A(CAS_BWE_A[i + 1]), // 9-bit output: Port A cascade Byte-write enable output

.CAS_OUT_BWE_B(CAS_BWE_B[i + 1]), // 9-bit output: Port B cascade Byte-write enable output

.CAS_OUT_DBITERR_A(CAS_DBITERR_A[i + 1]), // 1-bit output: Port A cascade double-bit error flag output

.CAS_OUT_DBITERR_B(CAS_DBITERR_B[i + 1]), // 1-bit output: Port B cascade double-bit error flag output

.CAS_OUT_DIN_A(CAS_DIN_A[i + 1]), // 72-bit output: Port A cascade output write mode data

.CAS_OUT_DIN_B(CAS_DIN_B[i + 1]), // 72-bit output: Port B cascade output write mode data

.CAS_OUT_DOUT_A(CAS_DOUT_A[i + 1]), // 72-bit output: Port A cascade output read mode data

.CAS_OUT_DOUT_B(CAS_DOUT_B[i + 1]), // 72-bit output: Port B cascade output read mode data

.CAS_OUT_EN_A(CAS_EN_A[i + 1]), // 1-bit output: Port A cascade output enable

.CAS_OUT_EN_B(CAS_EN_B[i + 1]), // 1-bit output: Port B cascade output enable

.CAS_OUT_RDACCESS_A(CAS_RDACCESS_A[i + 1]), // 1-bit output: Port A cascade read status output

.CAS_OUT_RDACCESS_B(CAS_RDACCESS_B[i + 1]), // 1-bit output: Port B cascade read status output

.CAS_OUT_RDB_WR_A(CAS_RDB_WR_A[i + 1]), // 1-bit output: Port A cascade read/write select output

.CAS_OUT_RDB_WR_B(CAS_RDB_WR_B[i + 1]), // 1-bit output: Port B cascade read/write select output

.CAS_OUT_SBITERR_A(CAS_SBITERR_A[i + 1]), // 1-bit output: Port A cascade single-bit error flag output

.CAS_OUT_SBITERR_B(CAS_SBITERR_B[i + 1]), // 1-bit output: Port B cascade single-bit error flag output

.ADDR_A({23{1'b1}}), // 23-bit input: Port A address

.ADDR_B({23{1'b1}}), // 23-bit input: Port B address

.BWE_A({9{1'b1}}), // 9-bit input: Port A Byte-write enable

.BWE_B({9{1'b1}}), // 9-bit input: Port B Byte-write enable

.CAS_IN_ADDR_A(CAS_ADDR_A[i]), // 23-bit input: Port A cascade input address

.CAS_IN_ADDR_B(CAS_ADDR_B[i]), // 23-bit input: Port B cascade input address

.CAS_IN_BWE_A(CAS_BWE_A[i]), // 9-bit input: Port A cascade Byte-write enable input

.CAS_IN_BWE_B(CAS_BWE_B[i]), // 9-bit input: Port B cascade Byte-write enable input

.CAS_IN_DBITERR_A(CAS_DBITERR_A[i]), // 1-bit input: Port A cascade double-bit error flag input

.CAS_IN_DBITERR_B(CAS_DBITERR_B[i]), // 1-bit input: Port B cascade double-bit error flag input

.CAS_IN_DIN_A(CAS_DIN_A[i]), // 72-bit input: Port A cascade input write mode data

.CAS_IN_DIN_B(CAS_DIN_B[i]), // 72-bit input: Port B cascade input write mode data

.CAS_IN_DOUT_A(CAS_DOUT_A[i]), // 72-bit input: Port A cascade input read mode data

.CAS_IN_DOUT_B(CAS_DOUT_B[i]), // 72-bit input: Port B cascade input read mode data

.CAS_IN_EN_A(CAS_EN_A[i]), // 1-bit input: Port A cascade enable input

.CAS_IN_EN_B(CAS_EN_B[i]), // 1-bit input: Port B cascade enable input

.CAS_IN_RDACCESS_A(CAS_RDACCESS_A[i]), // 1-bit input: Port A cascade read status input

.CAS_IN_RDACCESS_B(CAS_RDACCESS_B[i]), // 1-bit input: Port B cascade read status input

.CAS_IN_RDB_WR_A(CAS_RDB_WR_A[i]), // 1-bit input: Port A cascade read/write select input

.CAS_IN_RDB_WR_B(CAS_RDB_WR_B[i]), // 1-bit input: Port B cascade read/write select input

.CAS_IN_SBITERR_A(CAS_SBITERR_A[i]), // 1-bit input: Port A cascade single-bit error flag input

.CAS_IN_SBITERR_B(CAS_SBITERR_B[i]), // 1-bit input: Port B cascade single-bit error flag input

.CLK(clk), // 1-bit input: Clock source

.DIN_A({72{1'b1}}), // 72-bit input: Port A write data input

.DIN_B({72{1'b1}}), // 72-bit input: Port B write data input

.EN_A(1'b1), // 1-bit input: Port A enable

.EN_B(1'b1), // 1-bit input: Port B enable

.INJECT_DBITERR_A(1'b0), // 1-bit input: Port A double-bit error injection

.INJECT_DBITERR_B(1'b0), // 1-bit input: Port B double-bit error injection

.INJECT_SBITERR_A(1'b0), // 1-bit input: Port A single-bit error injection

.INJECT_SBITERR_B(1'b0), // 1-bit input: Port B single-bit error injection

.OREG_CE_A(1'b1), // 1-bit input: Port A output register clock enable

.OREG_CE_B(1'b1), // 1-bit input: Port B output register clock enable

.OREG_ECC_CE_A(1'b1), // 1-bit input: Port A ECC decoder output register clock enable

.OREG_ECC_CE_B(1'b1), // 1-bit input: Port B ECC decoder output register clock enable

.RDB_WR_A(1'b1), // 1-bit input: Port A read/write select

.RDB_WR_B(1'b1), // 1-bit input: Port B read/write select

.RST_A(CAS_RST[i]), // 1-bit input: Port A asynchronous or synchronous reset for

// output registers

.RST_B(CAS_RST[i]), // 1-bit input: Port B asynchronous or synchronous reset for

// output registers

.SLEEP(1'b0) // 1-bit input: Dynamic power gating control

);

end

end

endgenerate

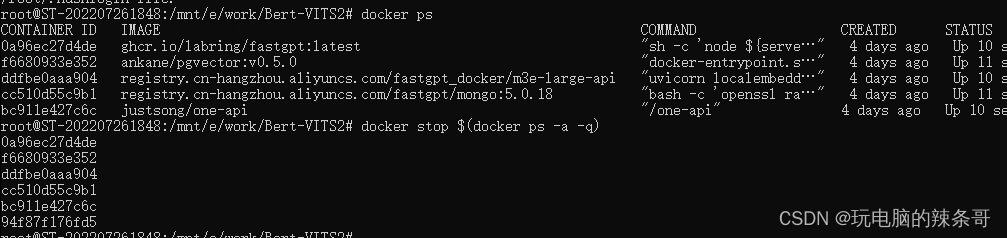

仿真

对于级联后URAM的使用方法可参考仿真文件激励的使用过程。

`timescale 1ns / 1ps

//

// Company:

// Engineer: wjh776a68

//

// Create Date: 03/23/2023 11:50:49 AM

// Design Name:

// Module Name: uram72_tb

// Project Name:

// Target Devices: XCVU37P

// Tool Versions: 2022.2

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module uram72_tb(

);

logic clk;

logic [71:0] DOUT_A;

logic [71:0] DOUT_B;

logic RDACCESS_A;

logic RDACCESS_B;

logic [22:0] ADDR_A;

logic [22:0] ADDR_B;

logic [8:0] BWE_A;

logic [8:0] BWE_B;

logic [71:0] DIN_A;

logic [71:0] DIN_B;

logic RDB_WR_A;

logic RDB_WR_B;

logic rst;

initial begin

clk = 0;

forever #1 clk = ~clk;

end

initial begin

rst <= 1;

repeat(2) @(posedge clk);

rst <= 0;

RDB_WR_A <= 0;

RDB_WR_B <= 0;

ADDR_A <= 0;

ADDR_B <= 0;

BWE_A <= 0;

BWE_B <= 0;

@(posedge clk);

@(posedge RDACCESS_A);

ADDR_A <= 23'h000f00;

DIN_A <= 72'h121112111211121121;

DIN_B <= 72'h121112111211121121;

BWE_A <= 'b111111111;

BWE_B <= 0;

RDB_WR_A <= 1;

@(posedge clk);

RDB_WR_A <= 0;

ADDR_B <= 23'h100;

@(posedge clk);

end

uram72 uram72_inst (

clk,

DOUT_A,

DOUT_B,

RDACCESS_A,

RDACCESS_B,

ADDR_A,

ADDR_B,

BWE_A,

BWE_B,

DIN_A,

DIN_B,

RDB_WR_A,

RDB_WR_B,

rst

);

endmodule

完整代码可从公众号回复URAM下载。