1 电路

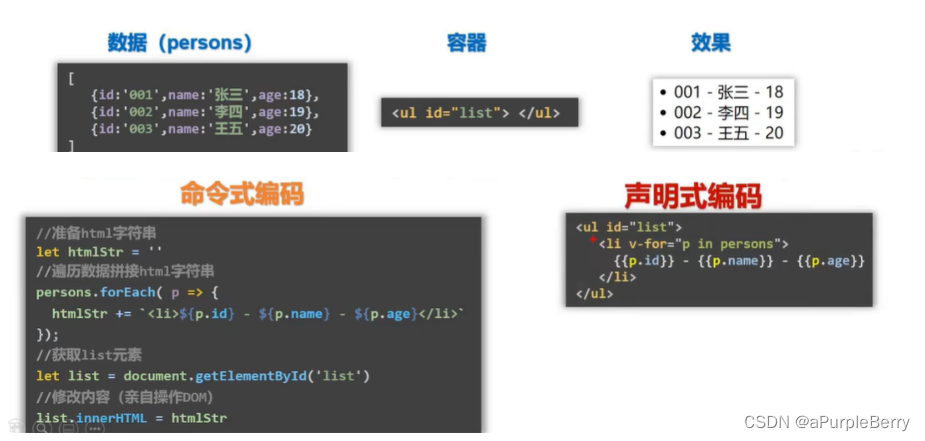

与c语言不同,verilog是并行执行语言,在看到一段简单的程序模块时,应该结合fpga内部逻辑模型,想到是什么样的功能电路。

2 时序

fpga的设计主要是以时序电路为主,它的所有动作都是在时钟一拍一拍的节奏下转变触发,即时钟是时序电路的控制者。

可以理解为时钟为心脏,功能模块为器官,而触发器为基本组织细胞。

3 可编程

fpga,可编程逻辑器件,分为可编程逻辑单元,可编程连线,可编程io。

之所以可编程是因为可以通过特殊01代码,制成一张张真值表,并将真值表组合起来实现大规模的逻辑功能。

4 工程性

fpga后端需要掌握时序优化,面积优化,功能优化等技能。软件方面,可以灵活定义API与软件架构,并可以通过处理器内核,实现软硬件协同开发。

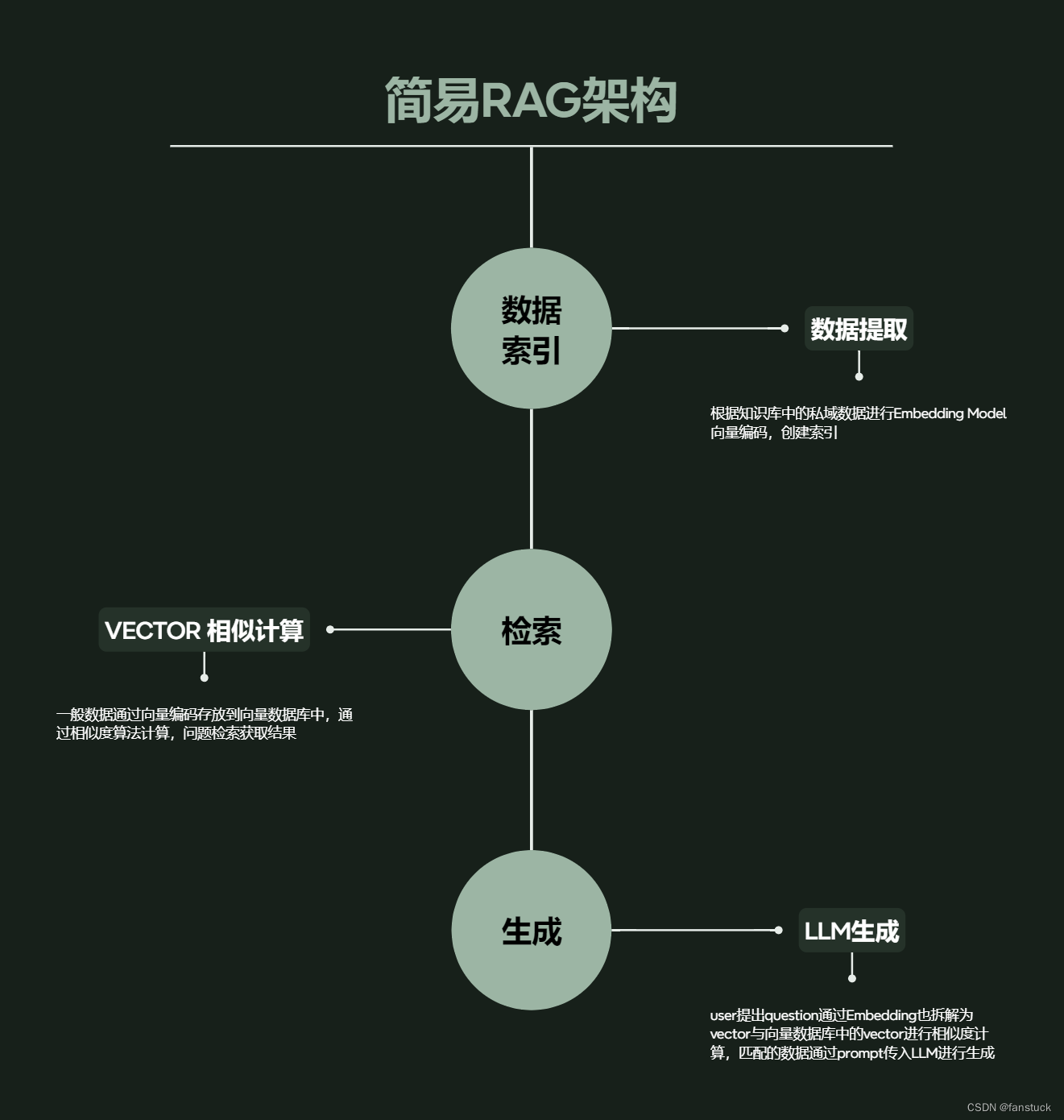

5 架构

单片机多基于给定架构,而fpga可以自定义软硬件架构,具有极高的灵活性与创造潜力。

子模块相对独立,以实现不同功能(子模块直接也可以有接口),在顶层模块中例化子模块,综合实现复杂功能。考虑时序。