视频链接

ZYNQ7100板级系统硬件实战01_哔哩哔哩_bilibili

ZYNQ硬件板级原理图实战导学

1、XC7Z100-2FFG900简介

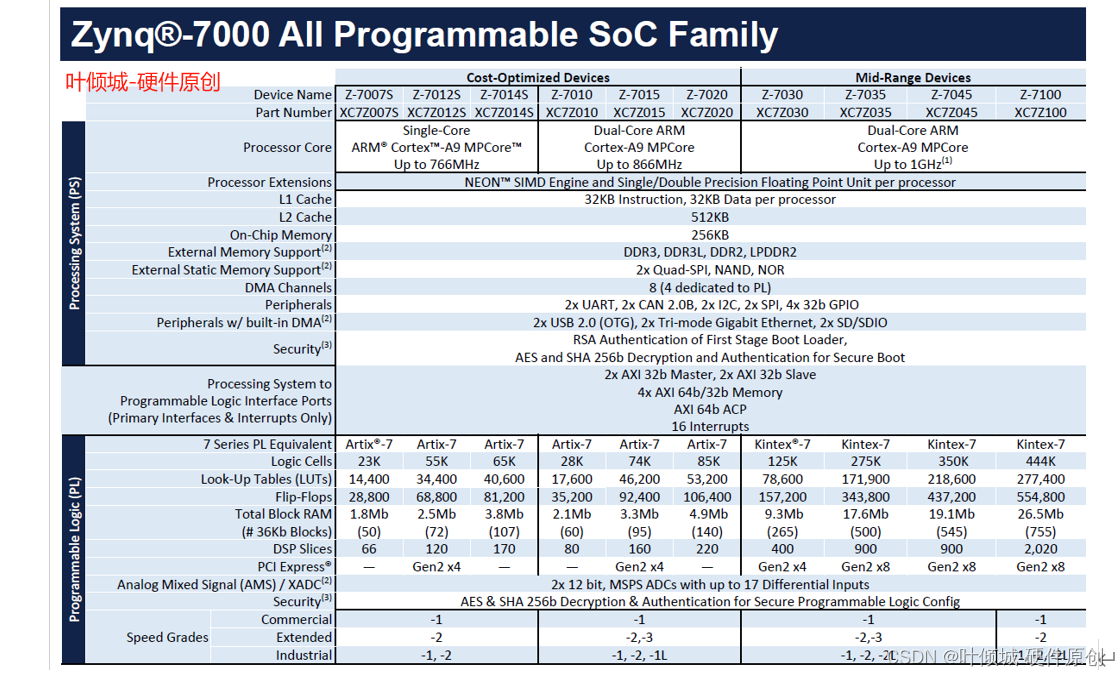

Zynq-7000系列是Xilinx公司推出的全可编程片上系统(All Programmable SoC),包含 PS(Processing System,处理器系统)和 PL(Programmable Logic,可编程逻辑)两部分。Zynq SoC整合了ARM双核cortex-A9处理器和 Xilinx 7系列 FPGA架构,ARM Cortex-A9 是一个应用级的处理器,能运行像 Linux 这样的操作系统,而可编程逻辑是基于 Xilinx 7 系列的 FPGA 架构。使得它不仅拥有ASIC在能耗、性能和兼容性方面的优势,而且具有FPGA硬件可编程性的优点。

性能 Artix < Kintex

ArtixTM-based devices: Z-7010, Z-7015, Z-7020

KintexTM-based devices: Z-7030, Z-7035,Z-7045,Z-7100

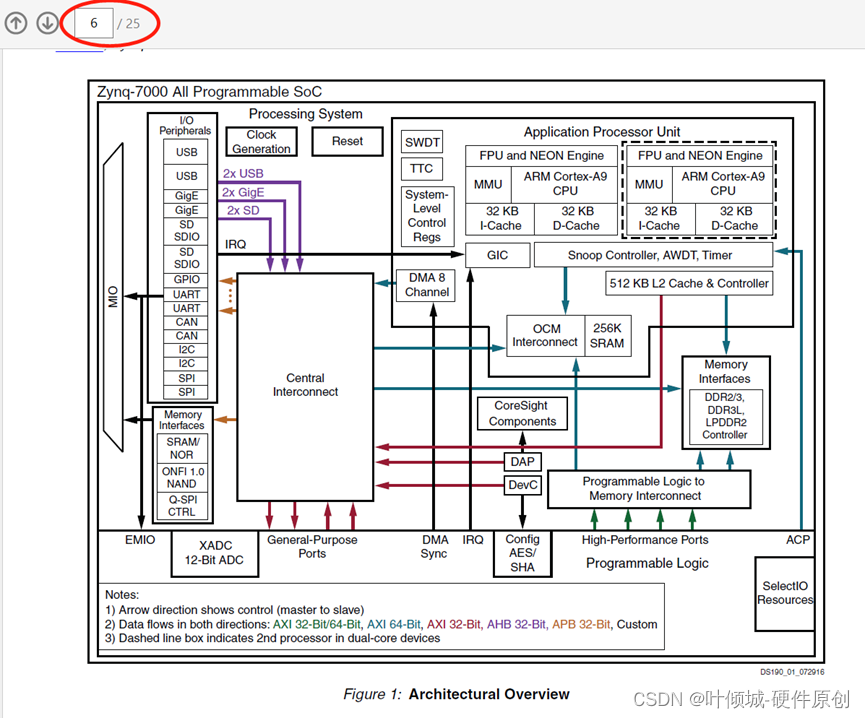

ZYNQ实际上是一个以处理器为核心的系统,PL只是它的一个外设。

Zynq-7000系列的亮点在于它包含了完整的ARM处理器系统,且处理器系统中集成了内存控制器和大量的外设,使 Cortex-A9 处理器可以完全独立于可编程逻辑单元。ZYNQ的PL和PS两部分的供电电路是独立的,这样PS或PL部分不被使用的话就可以被断电。

《ds190-Zynq-7000-Overview》 P7~P9

ZYNQ7000芯片的PS总体框图如图所示

《ds190-Zynq-7000-Overview》 P6

ZYNQ一般都是先配置启动PS,PS启动之后去配置PL。

ZYNQ处理器系统里并非只有 ARM 处理器,还有一组相关的处理资源,形成了一个应用处理器单元 (Application Processing Unit,APU),另外还有扩展外设接口、cache 存储器、存储器接口、互联接口和时钟发生电路等。

• Processing System (PS) 处理系统

1、Application processor unit (APU)

2、Memory interfaces

3、I/O peripherals (IOP)

4、Interconnect

• Programmable Logic (PL) 可编程逻辑

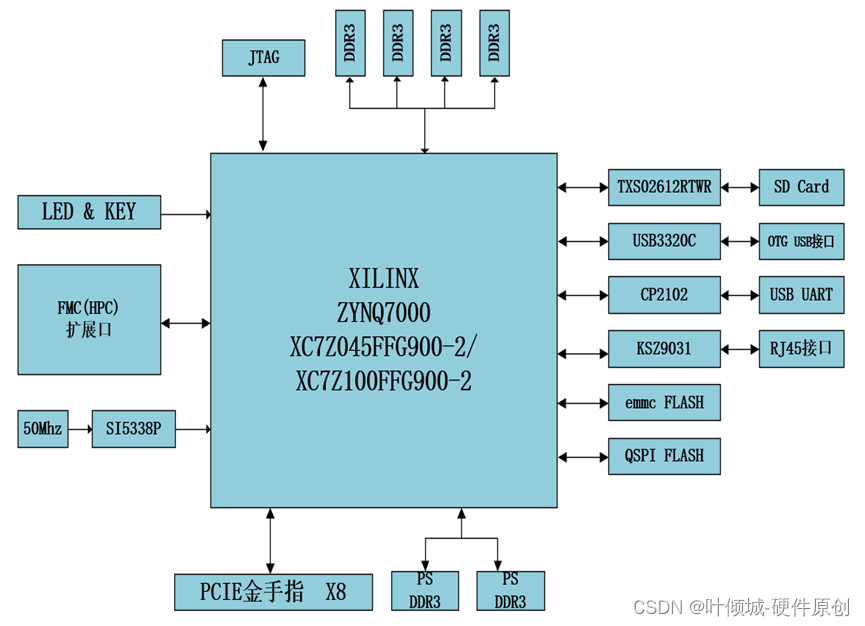

zynq板卡使用的是Xilinx公司的Zynq7000系列的芯片,型号为XC7Z100-2FFG900。芯片的PS系统集成了两个ARM Cortex™-A9处理器,AMBA®互连,内部存储器,外部存储器接口和外设。这些外设主要包括USB总线接口,以太网接口,SD/SDIO接口,I2C总线接口,CAN总线接口,UART接口,GPIO等。PS可以独立运行并在上电或复位下启动。

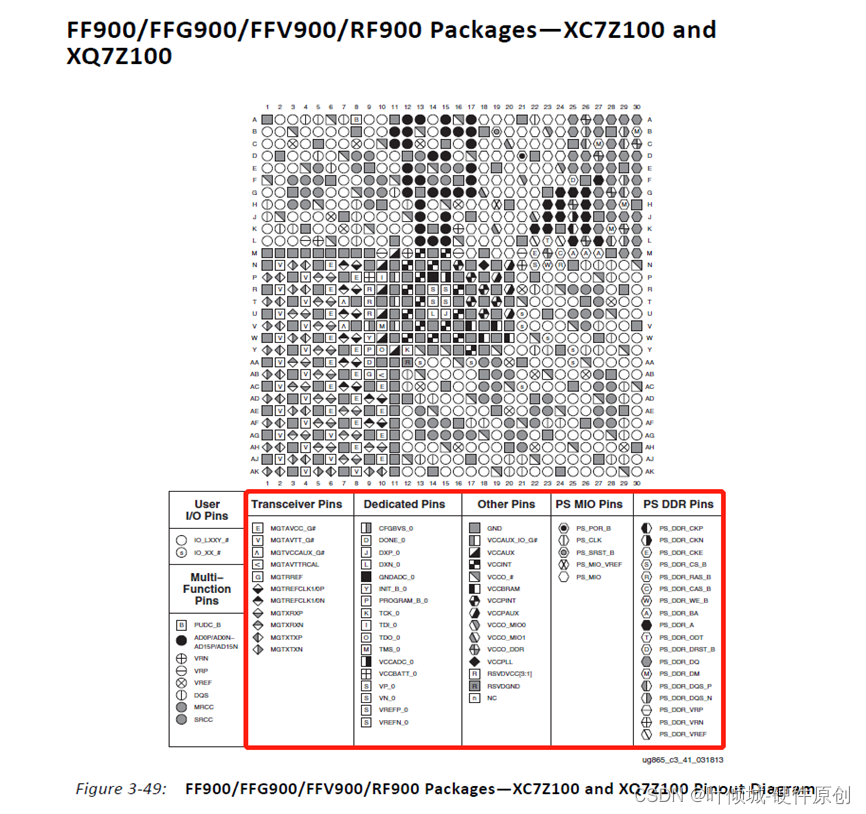

XC7Z100-2FFG900I芯片的速度等级为-2,工业级,封装为FGG900,引脚间距为1.0mm,ZYNQ7000系列的具体的芯片型号定义如下图所示。

Zynq 7000 SoC Package Devices Pinout Files

《ug865-Zynq-7000-Pkg-Pinout》 P11

其中FPGA芯片ZYNQ的主要参数如下所示:(★)

名称 |

具体参数 |

逻辑单元LogicCells |

326,080 |

查找表(Slices) |

50,950 |

触发器(CLBflip-flops) |

407,600 |

BlockRAM(36kbeach)大小 |

445 |

DSP处理单元(DSPSlices) |

840 |

PCIeGen2 |

1 |

模数转换/XADC |

1个12bit,1MbpsAD |

GTPTransceiver |

16个,12.5Gb/smax |

速度等级 |

-2 |

温度等级 |

工业级 |

1.1.2、XC7Z100-2FFG900的管脚分类

1.1.2.1、XC7Z100-2FFG900的PL Pins summary

Pin Name |

Description |

| CFGBVS_0 (Input) Dedicated |

Configuration Banks Voltage Select 配置组电压选择 This pin selects the preconfiguration I/O standard type for the dedicated configuration bank 0. If the VCCO for bank 0 is 2.5V or 3.3V, then this pin must be connected to VCCO_0. If the VCCO for bank 0 is less than or equal to 1.8V, then this pin should be connected to GND. 这个引脚选择专用配置Bank 0的预配置I/O标准类型。 如果Bank 0的VCCO为2.5V或3.3V,则该引脚必须连接到VCCO_0。 如果Bank 0的VCCO小于或等于1.8V,则该引脚应连接到GND。 |

DONE_0 (Bidirectional) Dedicated |

Active High, DONE indicates successful completion of configuration. DONE表示配置成功完成(高电平有效) |

INIT_B_0 (Bidirectional) (open-drain) Dedicated |

Active Low, indicates initialization of configuration memory. 表示配置存储器的初始化(低电平有效); |

PROGRAM_B_0 (Input)Dedicated |

Active Low, asynchronous reset to configuration logic. 异步复位到配置逻辑(低电平有效)。 |

TCK_0 (Input) Dedicated |

IEEE Std 1149.1 (JTAG) Test Clock Jtag测试时钟 |

TDI_0 (Input) Dedicated |

JTAG Test Data Input Jtag数据输入 |

TDO_0 (Output)Dedicated |

JTAG Test Data Output Jtag数据输出 |

TMS_0 (Input)Dedicated |

JTAG Test Mode Select Jtag模式选择 |

RSVDVCC[3:1] Dedicated N/A |

Reserved pins—must be tied to VCCO_0. 保留引脚 — 必须连接到VCCO_0。 |

RSVDGND Dedicated N/A |

Reserved pins—do not connect. 保留引脚 — 不连接 |

| VCCBATT_0 N/A Supply Voltage |

Decryptor key memory backup supply; this pin should be tied to the appropriate VCC or GND when not used. 解密器密钥存储器备份供电;当不使用时,此引脚应连接到适当的VCC或GND。 //VCCBATT是FPGA内部易失性存储器的电池备份电源,用于存储AES解密器的密钥。 对于需要来自易失性密钥存储区的解密密钥的加密比特流,将此引脚连接到电池以在FPGA未供电时保留密钥。 如果不要求使用易失性密钥存储区中的解密密钥,请将此引脚连接到GND或VCCAUX。 // |

1.1.2.2、XC7Z100-2FFG900的PS Pins summary

1.1.2.3、XC7Z100-2FFG900的MGT Pins summary

1.1.2.4、XC7Z100-2FFG900电源管脚分类

1.1.3、MIO-at-a-Glance Table (bank 500 & 501 配置)(★)

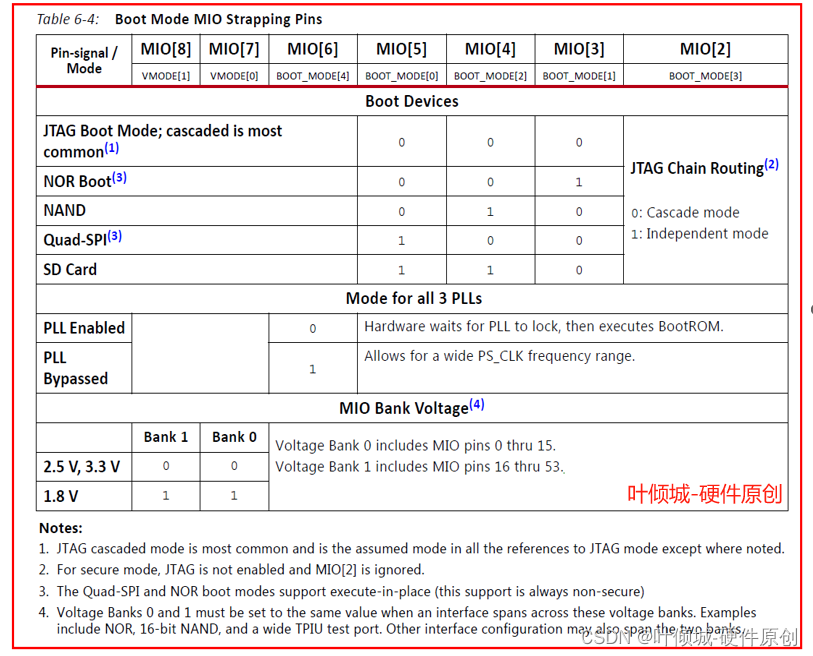

1.1.4、BOOT Mode MIO Strapping Pins (★)