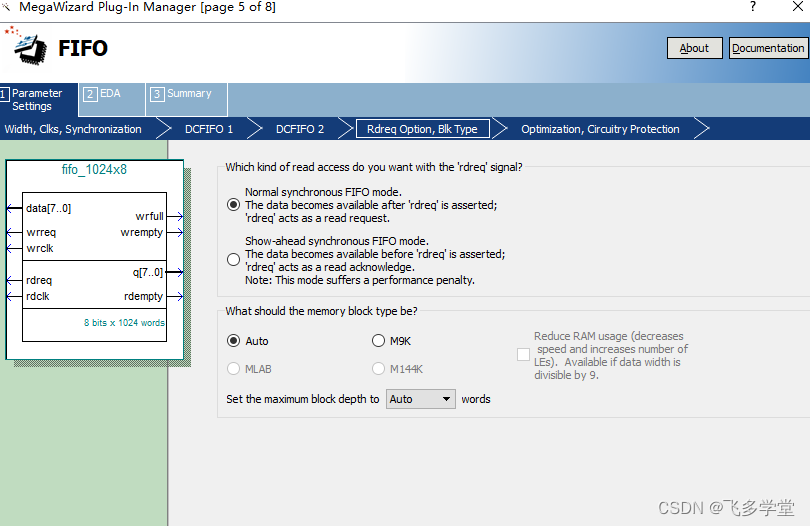

1.IDE:Quartus II

2.设备:Cyclone II EP2C8Q208C8N

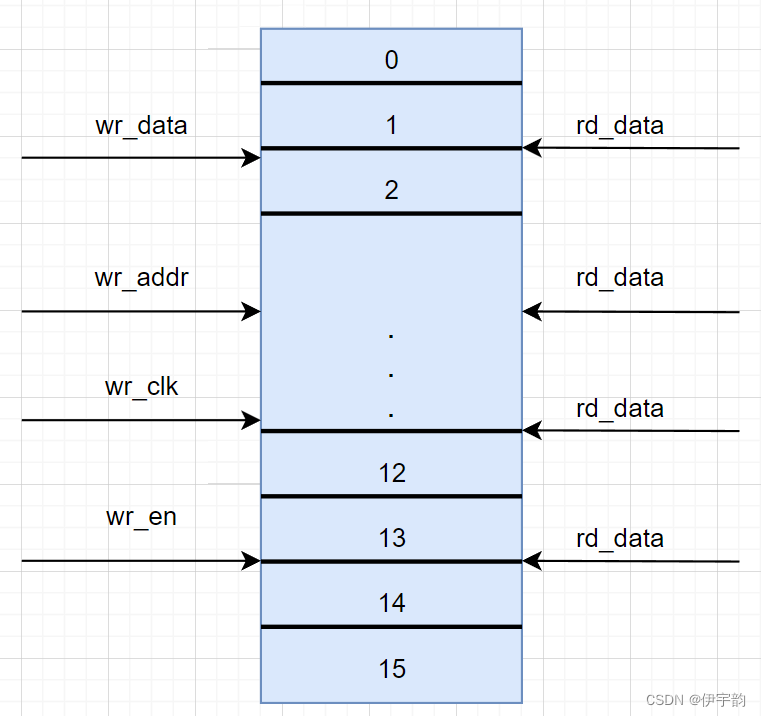

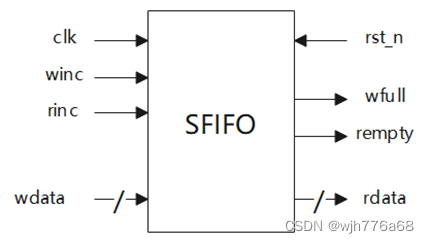

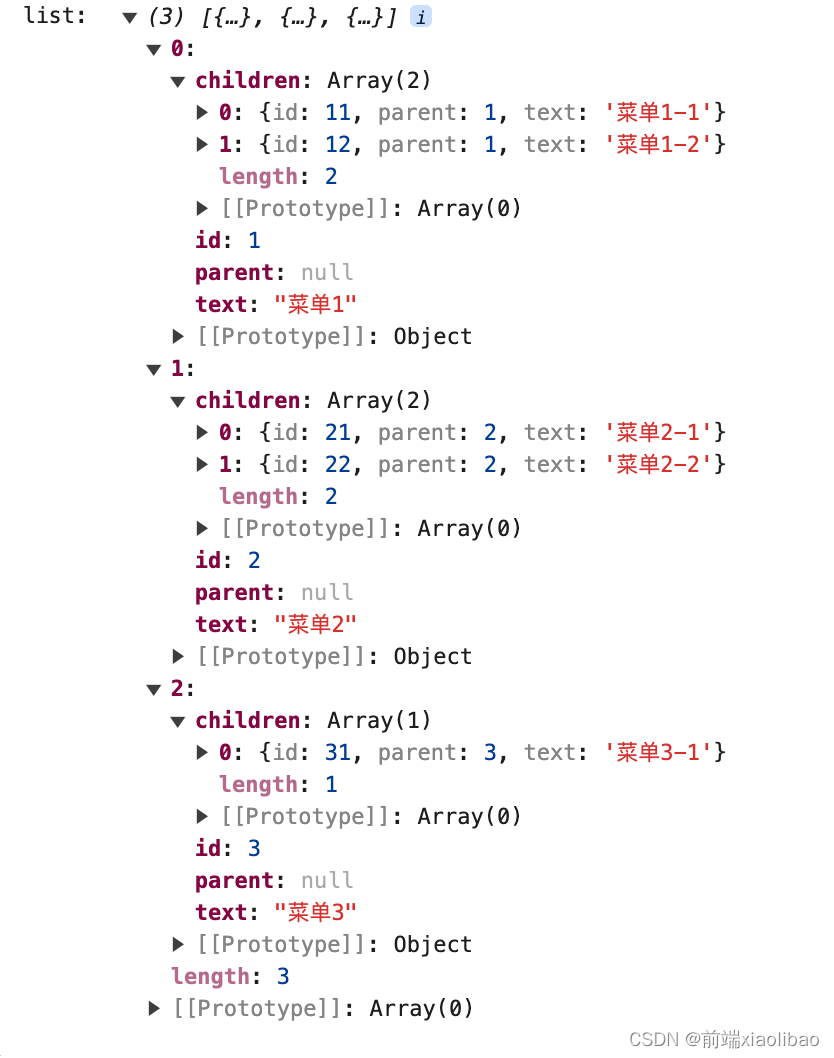

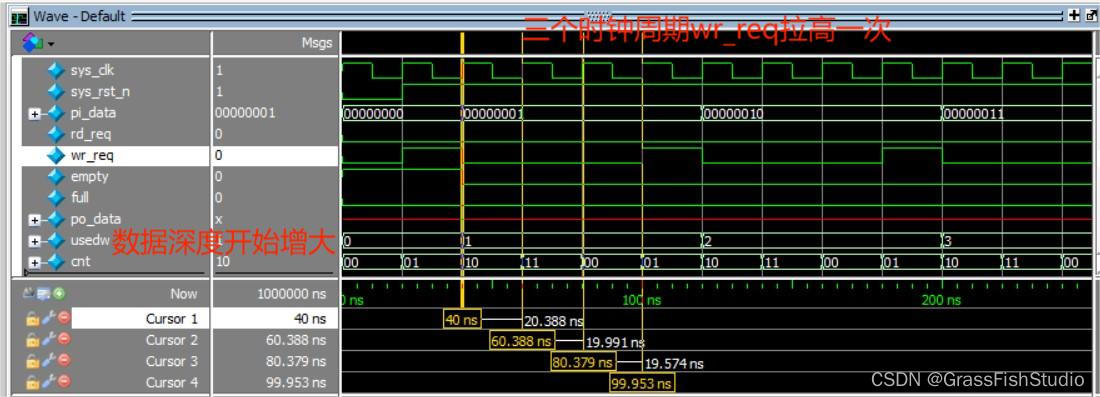

3.实验:同步fifo数据先入先出,输入8位宽数据,输出也为8位宽数据,每三个时钟输入一个数据,数据输入同时也会自增1,直到255。

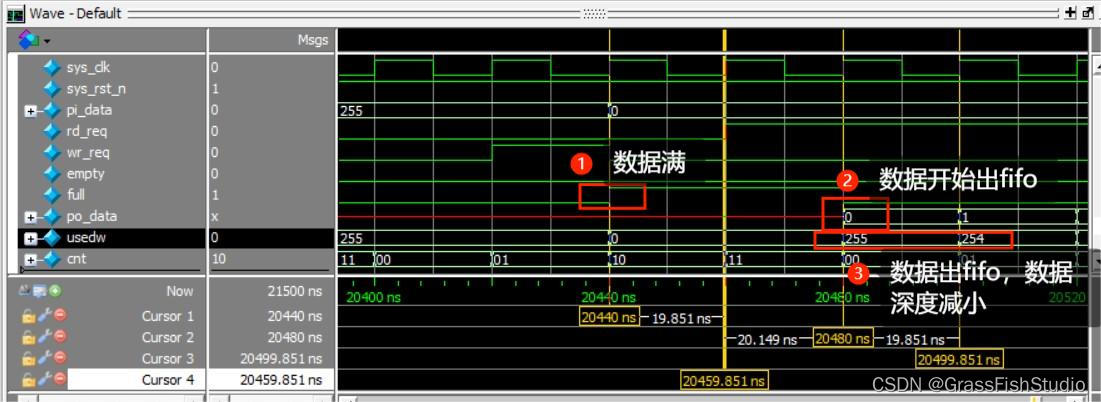

4.时序图:

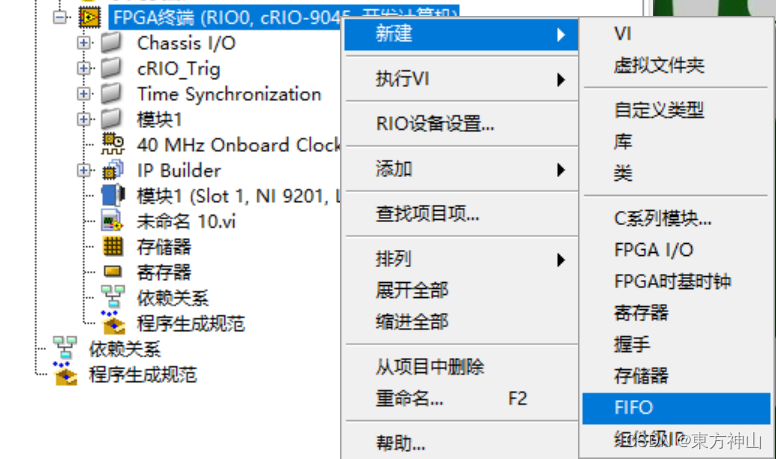

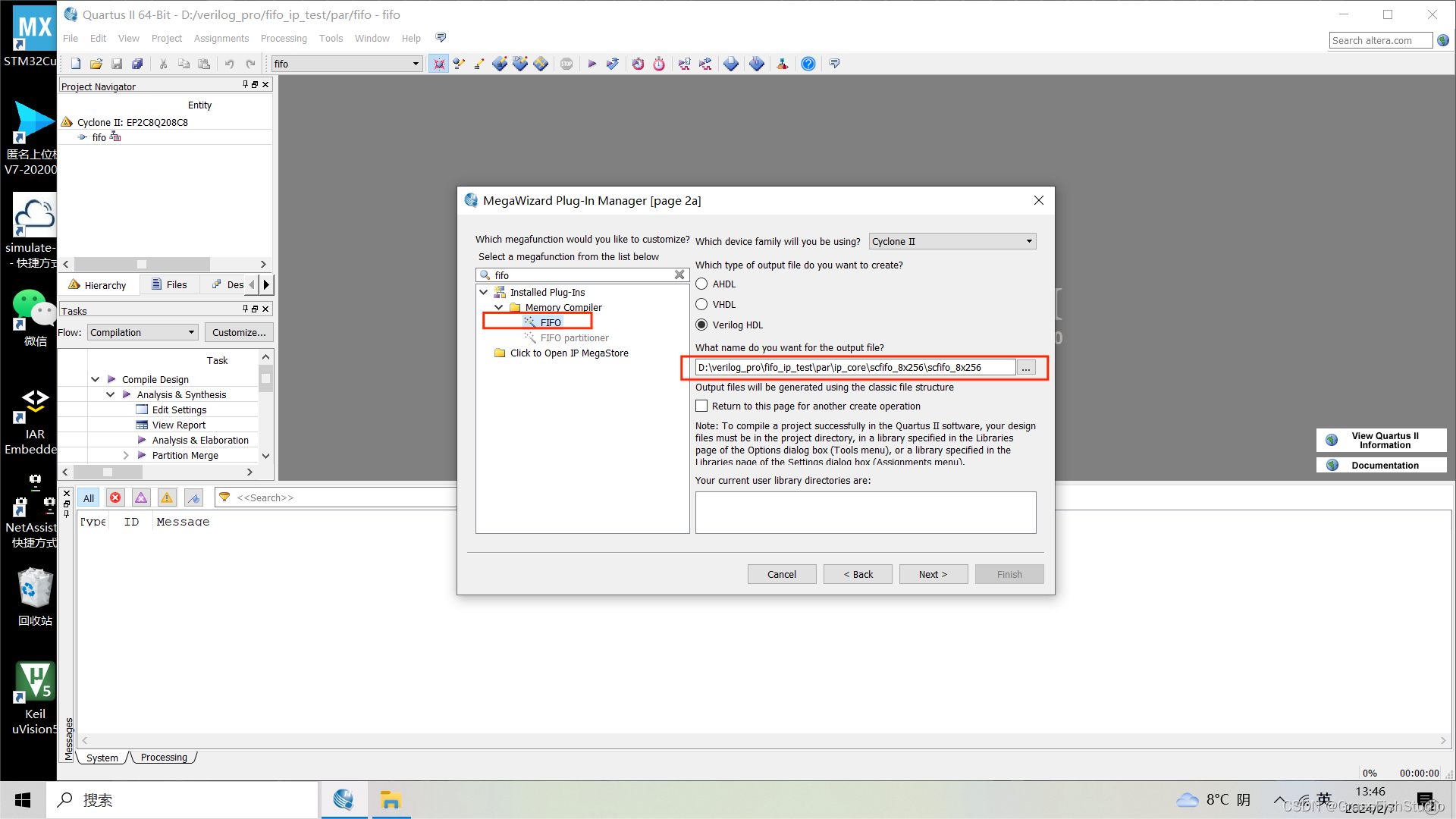

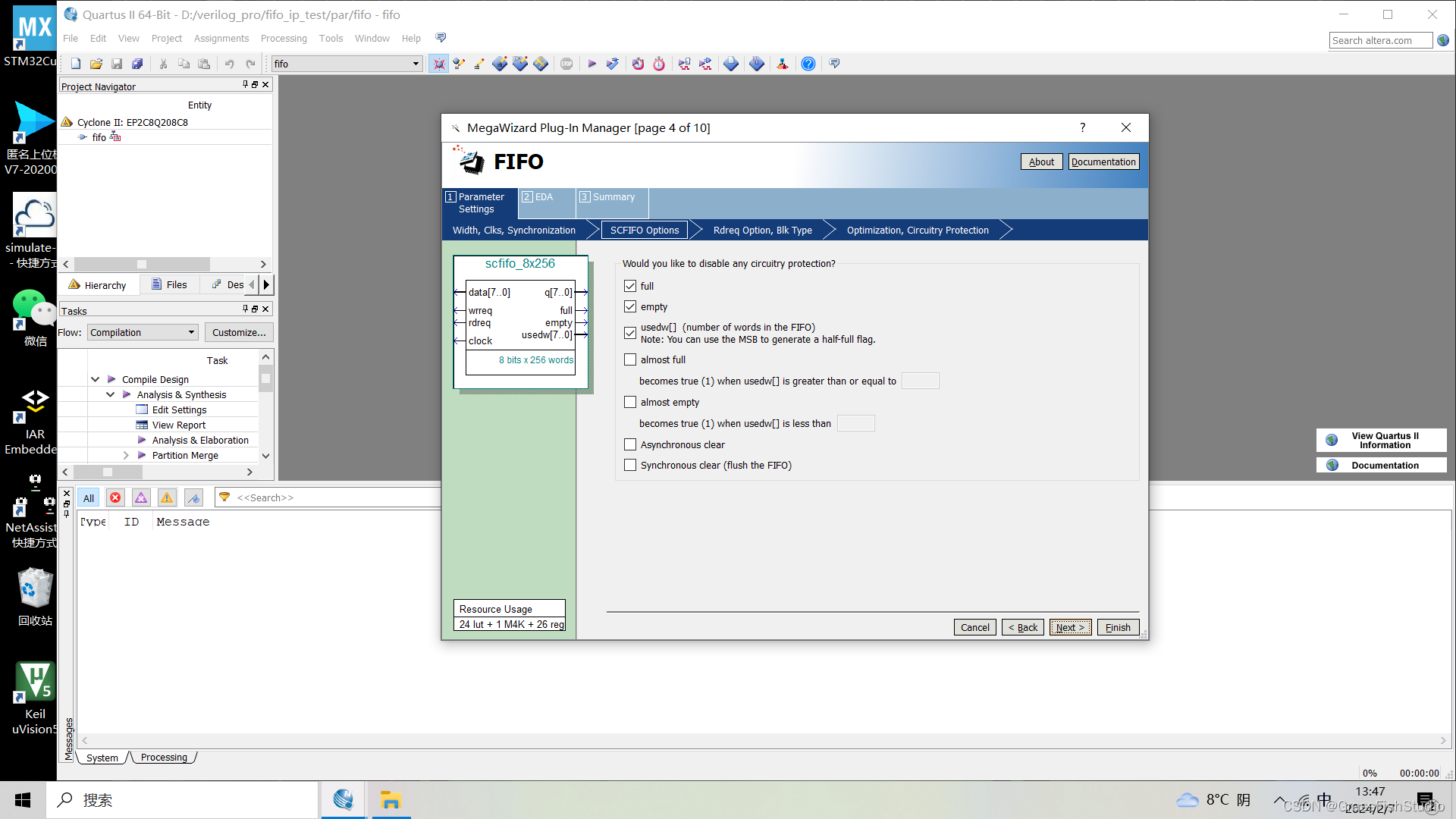

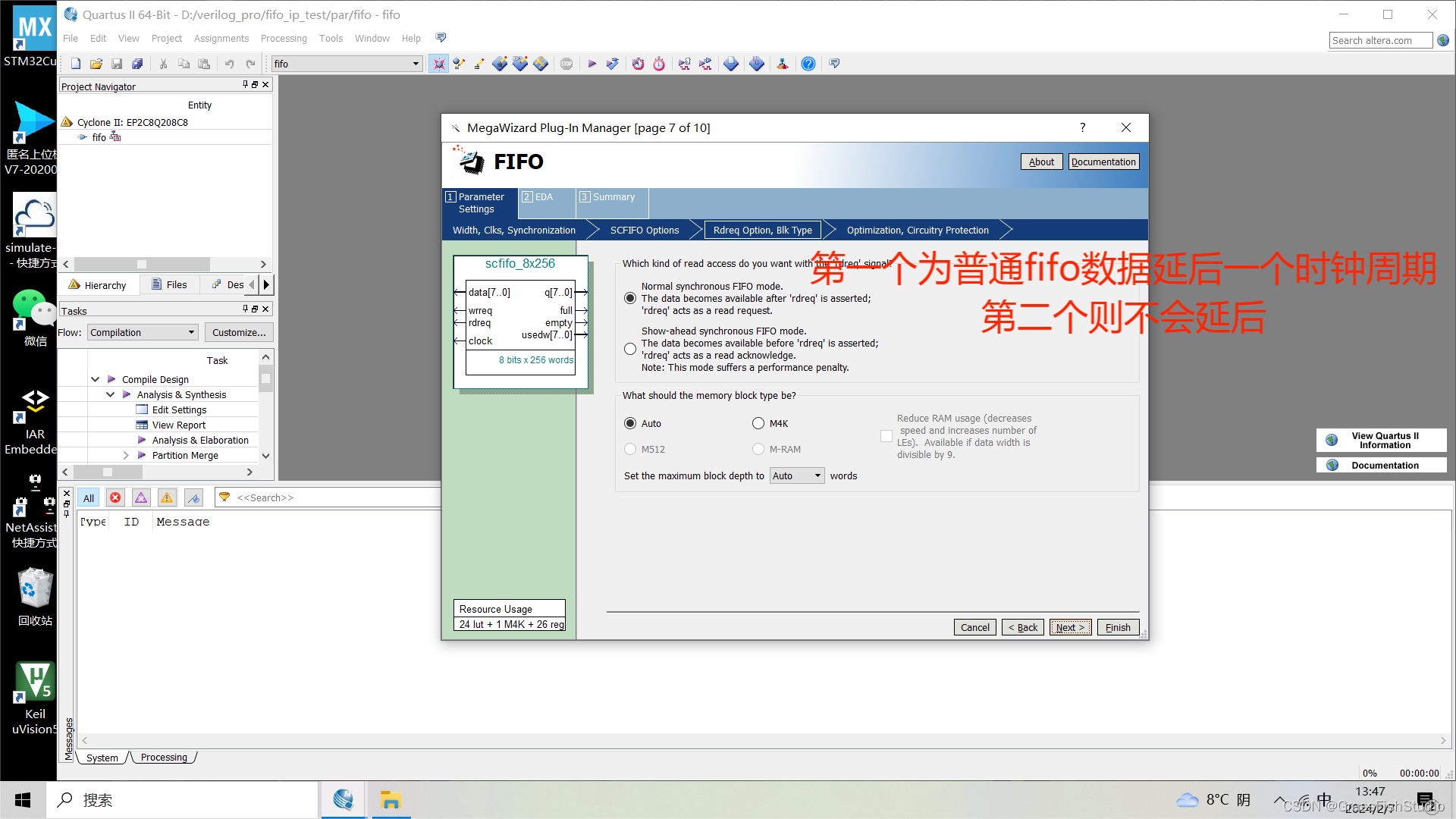

5.步骤

6.代码:

fifo.v

/*

*同步fifo

*/

module fifo(

input wire sys_clk ,

input wire [7:0] pi_data , //输入的数据

input wire rd_req ,

input wire wr_req ,

output wire empty ,

output wire full ,

output wire [7:0] po_data , //出来的数据

output wire [7:0] usedw //fifo中的数据个数

);

/*

*实例化配置的fifo IP核

*/

scfifo_8x256 scfifo_8x256_inst (

.clock (sys_clk),

.data (pi_data),

.rdreq (rd_req ),

.wrreq (wr_req ),

.empty (empty ),

.full (full ),

.q (po_data),

.usedw (usedw )

);

endmodule

tb_fifo.v

/*

*同步fifo仿真代码

*/

`timescale 1ns/1ns

module tb_fifo();

reg sys_clk ;

reg sys_rst_n ;

reg [7:0] pi_data ;

reg rd_req ;

reg wr_req ;

wire empty ;

wire full ;

wire [7:0] po_data ;

wire [7:0] usedw ;

reg [1:0] cnt ; //计数器,三个时钟fifo进一个数据

/*

*初始化

*/

initial

begin

sys_clk = 1'b1 ;

sys_rst_n = 1'b0 ;

#20

sys_rst_n = 1'b1 ;

end

always #10 sys_clk = ~ sys_clk ; //模拟时钟

/*

*计数器

*/

always @ (posedge sys_clk or negedge sys_rst_n) begin

if(sys_rst_n == 1'b0)

cnt <= 2'd0;

else if(cnt == 2'd3)

cnt <= 2'd0;

else

cnt <= cnt + 1'b1;

end

/*

*写请求信号(三个时钟信号一次写请求)

*/

always @ (posedge sys_clk or negedge sys_rst_n) begin

if(sys_rst_n == 1'b0)

wr_req <= 1'b0 ;

else if(cnt == 2'd0 && rd_req == 1'b0)

wr_req <= 1'b1 ;

else

wr_req <= 1'b0 ;

end

/*

*输入信号赋值(0~255)

*/

always @ (posedge sys_clk or negedge sys_rst_n) begin

if(sys_rst_n == 1'b0)

pi_data <= 8'd0 ;

else if(pi_data == 8'd255 && wr_req == 1'b1) //数据满

pi_data <= 8'd0 ;

else if(wr_req == 1'b1) //数据没有满的情况下,且写请求信号到来则将写入的数据增大1

pi_data <= pi_data + 1'b1 ;

else

pi_data <= pi_data ;

end

/*

*读请求信号

*/

always @ (posedge sys_clk or negedge sys_rst_n) begin

if(sys_rst_n == 1'b0)

rd_req <= 1'b0 ;

else if(full == 1'b1) //数据满则发出读信号

rd_req <= 1'b1 ;

else if(empty == 1'b1) //数据空则失能读信号

rd_req <= 1'b0 ;

else

rd_req <= rd_req ;

end

/*

*实例化fifo模块

*/

fifo fifo_inst(

.sys_clk (sys_clk) ,

.pi_data (pi_data) ,

.rd_req (rd_req ) ,

.wr_req (wr_req ) ,

.empty (empty ) ,

.full (full ) ,

.po_data (po_data) ,

.usedw (usedw )

);

endmodule