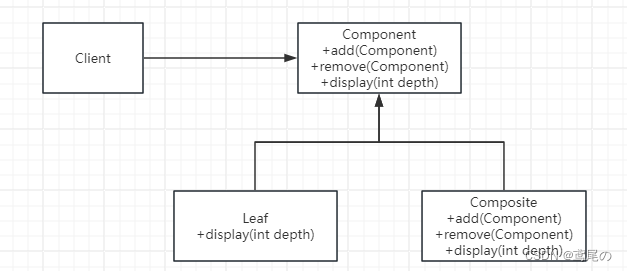

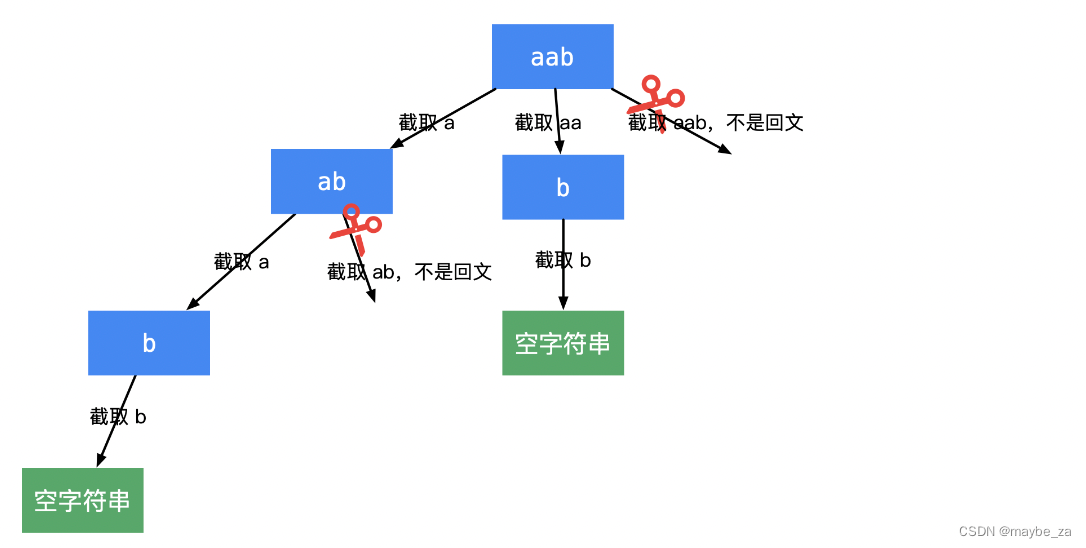

架构

1.系统逻辑视图

- Ingress Chip作用:

- 解析报文128字节的头部(MMU(Memory Management Unit) Cell的最小单元)

- 隧道终结(网络隧道:一种在网络中传输数据的技术,它通过在原始数据包的外部封装一层或多层额外的协议头来创建一个虚拟的通道)

- 报文头分类,决定VRF(Virtual Routing and Forwarding)

- 通过VRF与报文头的信息进行L2/L3/MPLS查找

- 入口ACL处理;基于ACL(Access Control List)进行计数与统计

- 报文缓存、准入控制与调度

- 修改报文(如基于报文类型进行修改)

- Switch Fabric(交换结构)作用:

- 基于HiGig头部信息进行报文的交换选路(HiGig:一种网络交换设备之间使用的接口模式)

- 多播处理

- 支持基于服务的流量控制

- Egress Chip作用:

- 解析HiGig报文头

- 根据HiGig头部信息决定出端口

- 报文缓存、准入控制与调度

- 修改报文

- 出口ACL处理

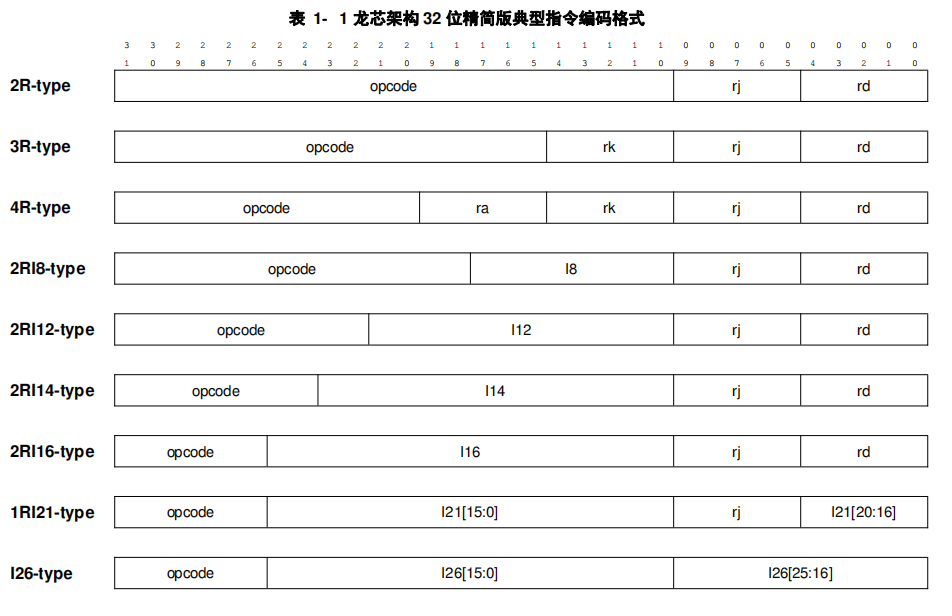

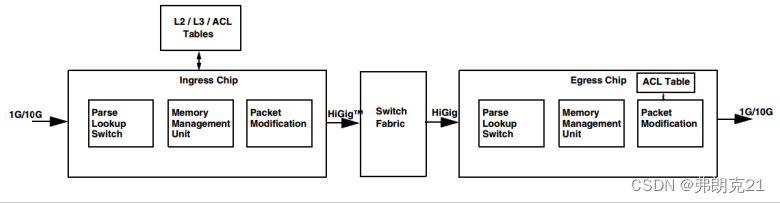

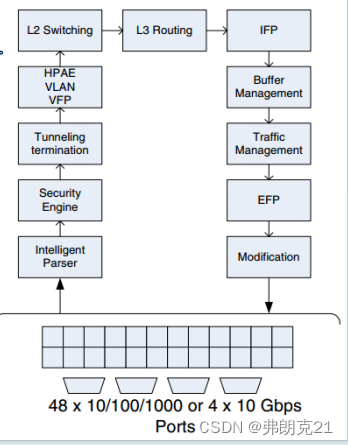

2.逻辑芯片视图

![[图片]](https://img-blog.csdnimg.cn/direct/4800b686996847caaa2f6043102e87fe.png)

TCAM:Ternary Content Addressable Memory三态内容寻址寄存器。从CAM的基础上发展而来。一般的CAM存储器中每个bit位的状态只有两个(“0"或"1”)、而TCAM中每个bit位有三种状态,除掉"0"和

"1"外,还有一个"don’ t care"状态,所以称为三态,它是通过掩码来实现的,正是TCAM的这个第三种状态特征使其既能进行精准匹配查找,又能进行模糊匹配查找,而CAM没有第三种状态,所以只能进行精准匹配查找。TCAM表内所有条目都可以并行访问,比如,如果你要100条ACL,TCAM能一次就能对比这100条ACL进行对比操作,过去如果有100条ACL的话,需要第一条ACL对比完后再对比第二条,再对比第三条,直至N条,效率很明显没有TCAM高。

TCAM的组件FM(特性管理器)软件将匹配语句编译(合并)为TCAM表项,这样就可以以帧转发速度查询TCAM。

参考文档:https://blog.csdn.net/u013480581/article/details/53305800

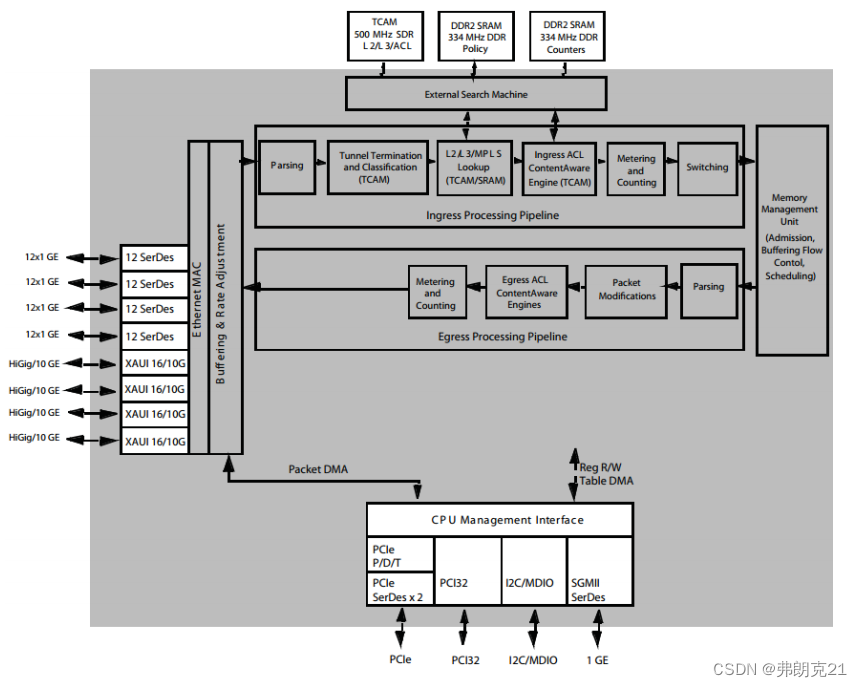

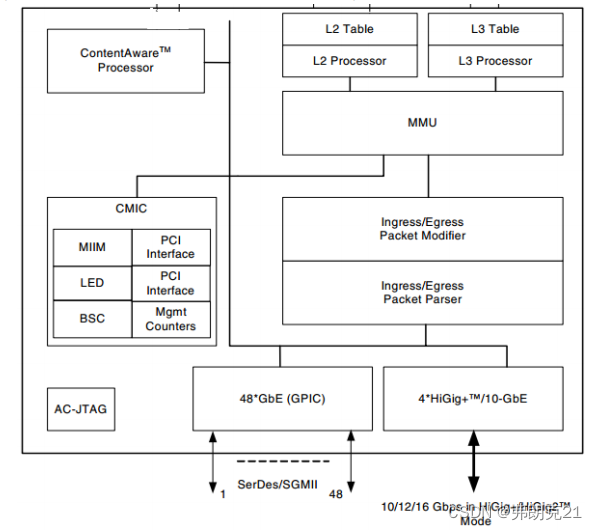

3.芯片框图

- GPIC(Gigabit Ethernet Port Interface Controller):端口的配置信息驻留在GPIC里。GPIC可以配置为SGMⅡ模式或者SerDes模式。SGMⅡ模式可以直连外部PHY设备;SerDes模式可以直接连接光模块

- HiGig:HiGig模式用于多个芯片互连来增加整个系统的端口密度

- CMIC(Communication Media Interface Controller):通PIC外接CPU,实现对芯片寄存器的读写设置操作。CPU口发包的处理逻辑与端口接收报文一样(一般CPU口是0口,就像0口接收到了报文一样),处理过程也会出现报文重新被送CPU的情况。

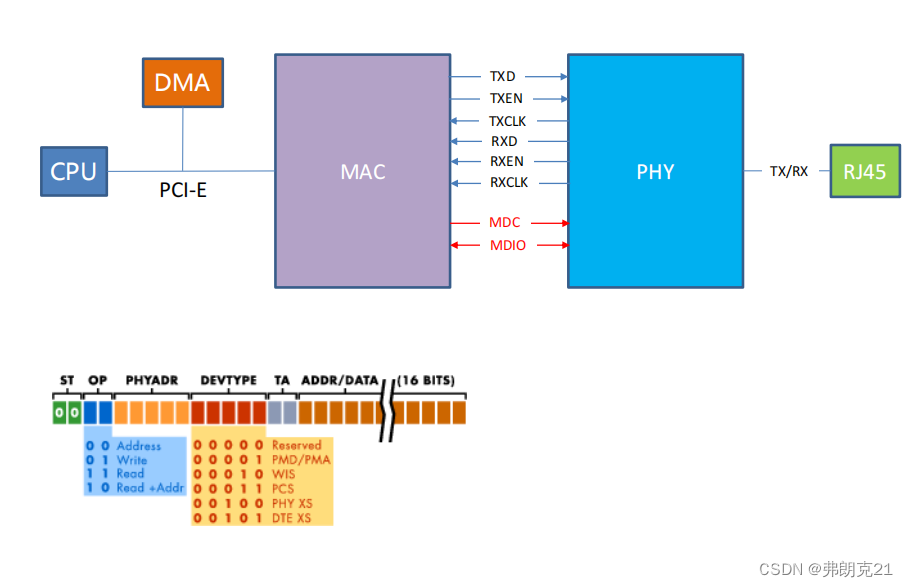

4.MIIM(Medium Independent Interface Management)

5.交换结构

采用模块化、高性能的管道式报文交换处理架构。再管道上的每个模块都有各自的处理功能,并把处理的结构提供给下一模块进行处理。

- Intelligent Parser:包括两个独立的解析器,全解析器和HiGig解析器。全解析器负责解析来自端口与CMIC的报文(面板口与CPU口),需要的信息都可以在头128字节里获得,全解析器必须保存所有的解析信息,以备各种搜索引擎使用,HiGig解析器负责解析来自HiGig口的报文。

- Security Engine:早期的硬件安全检测机制,防止Dos攻击。

- L2 Switching:分配VLAN、优先级,源MAC学习,目的MAC查找转发

- L3 Routing:源/目的IP查找

- ContenAware Proccessing:CAP用来提供ACL、差分服务、QoS等类型的应用。图中的IFP、EFP即CAP。

- Buffer Management:控制端口的传输行为与流量整形。每个出口关联有8个CoS队列,调度器可配置为不同的模式对这8个队列进行不同的仲裁。调试器仲裁的一个主要方面是提供最小带宽保证与最大带宽限速,通过监视每个CoS队列的计数机制实现。

- Modification:根据搜索引擎的结果,进行VLAN转换、隧道封装与L3路由变更。

CAP之前被称为过滤引擎(filter precessor),所以IFP(ingress filter processor)、EFP(egress filter processor)沿用了这样的命名。

Interlligent Parser可以从逻辑上看成是硬件内部有一个微程序(硬件电路实现)负责解析报文,并把报文的各个字段(如MAC,IP等)保存到结构体的各个成员变量里,以便高效地提供给后续的搜索引擎使用。

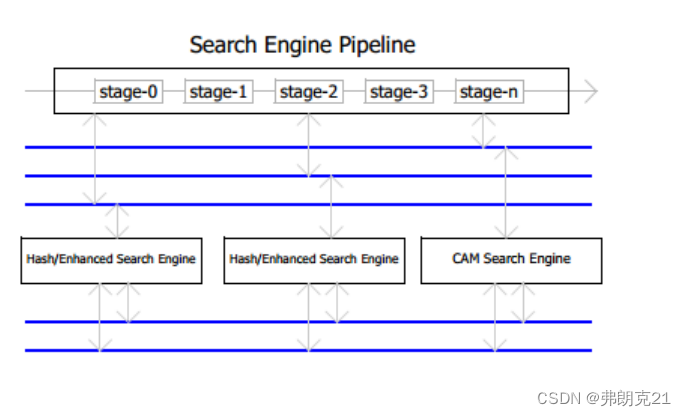

6.CAP

芯片内部主要的搜索引擎有两种:HASH搜索引擎和CAM搜索引擎

- HASH搜索引擎:L2、L3、VLAN表、IPMC表等等

- CAM搜索引擎:ACL表

每个搜索引擎都带有一定的存储空间,用来存储相应的内容表项。搜索引擎采用管道式的架构,进行每个引擎的处理