系列文章目录

提示:这里可以添加系列文章的所有文章的目录,目录需要自己手动添加

例如:第一章 Python 机器学习入门之pandas的使用

提示:写完文章后,目录可以自动生成,如何生成可参考右边的帮助文档

前言

闪存Vt编码需遵循格雷码的标准。而在TLC上,我们可以构造数个不同的格雷码以满足8个Vt状态的编码需求。选哪个格雷码使用,则和TLC各个页(page)的读取性能及可靠性平衡相关。

一、先以MLC为例

先以MLC为例,每一个存储单元可以存储两个bit,分别隶属于Upper Page (UP),和Lower Page (LP)。为了获得两个bit的数据,每个闪存单元有4个Vt状态,需要用三个Vref来作比较。即,

又因为UP的读取需要两次Vref的比较,LP的读取只需要一次Vref的比较,所以UP的读取速度比LP要慢很多;相应的UP所承受的读干扰(Read Disturb)也会比LP要多。这会在系统端应用的时候,造成性能与可靠性的下降。

二、举例

1.性能说明

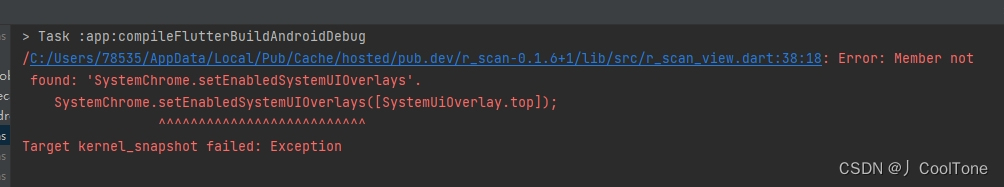

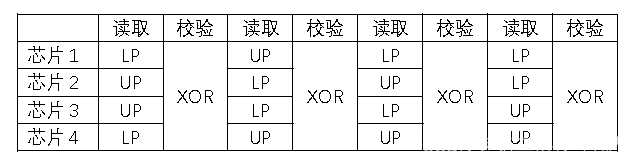

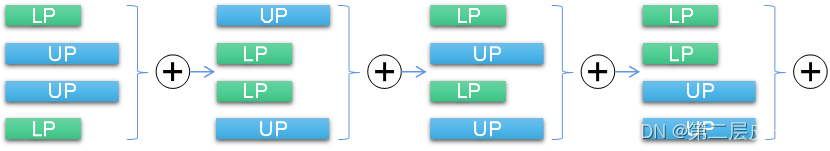

用性能举一个例子,如果闪存控制器(controller),同时在四个闪存芯片上读取数据,且要求四个芯片上的数据都读取完成后再做奇偶校验,其顺序如下,

以上一共16个page,假设UP的读取延时是LP的1.5倍,LP和UP的数量各占一半的情况下,平均每次的读取时间理应是1.25个LP的读取时间。但事实上每次奇偶校验都要等待最慢的一个page读完才能开始,因此实际完成这个操作的时间会更长,

所以在固件的设计中,通常希望把各个芯片上有“并行读取”需求的数据都放在相同类型的页里 -- 要么都放在LP里,要么都放在UP里,以降低对性能的影响。同理,在闪存的设计中,我们希望尽量缩短UP的读取时间,让固件设计的回旋余地更大。并且Vref_UP1和Vref_UP2左边,即Vt编码是11和00的两个Vt分布,要控制得离这两个Vref稍远些,尤其是Vt最低的11态。因为读干扰会让Vt上升,对低Vt态的影响最大。

就TLC而言,由于有8个Vt状态,需要7次比较才能把三个页(LP、MP、UP)都读出来。TLC如果沿用SLC到MLC的思路,将这7次比较分配为:LP比较1次,MP比较2次,UP比较4次。这虽然也能得到所有数据,但在系统应用端,读取性能势必会被UP的超长延迟所牵制。且UP的读干扰也会数倍于LP。为了更好的平衡各个页之间的读延时与读干扰,TLC会使用2-3-2读取,即在分配7次比较时:LP用两个比较电压,比较两次;MP用三个比较电压,比较三次;UP用两个比较电压,比较两次。这样做可以降低最高比较次数,平衡各个page的读取。以此类推,QLC有16个Vt状态,需要15个比较电压,读4个page,所以最佳分配应该是3-4-4-4或者4-3-4-4之类的读取。

2.TLC2-3-2

然而TLC 2-3-2读取和TLC Vt编码又有什么关系呢?可以利用MLC的例子来做初步的解释。为了更方便解释,我们作一些重命名,以统一MLC、TLC乃至QLC、PLC各个Vt状态和Vref的命名规范:

最低的Vt状态命名为Erase态,简称E

次低至最高的Vt状态命名为Program态,简称P。对MLC,有三个P态,从低到高分别是P1、P2、P3。TLC可以类推,有P1、P2、P3、P4、P5、P6、P7,7个program态。QLC有15个program态。

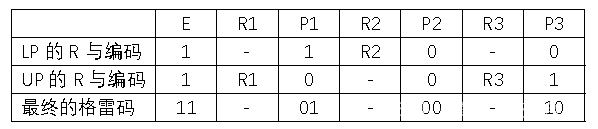

在读取数据时使用的比较电压,命名为Read电压,简称R。对MLC,有三个R,R1、R2、R3。TLC有7个Read电压,QLC有15个Read电压。将E/P/R按电压高低,放在同一个表里,再加上各个页的编码,对MLC,可得

LP用一次比较读出,比较电压是R2。比R2低的Vt读作1、比R2高的Vt读作0

UP用两次比较读出,比较电压是R1和R3,在R1、R3之间的Vt读作0,在这两个比较电压之外的Vt读作

再观察一下上面的表,不难发现,一旦定义好了某个page所使用的R,那么只要编码在R的两边做翻转,就可以得到对应这个page的Vt的二进制编码。比如

就LP而言,R2的左边是1,右边是0、

就UP而言,R1的左边是1,右边是0;R3的左边是0,右边是1

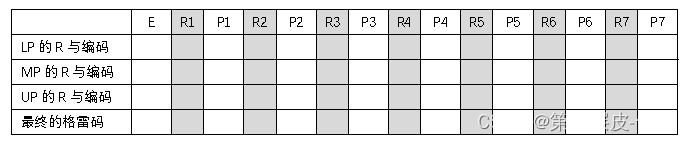

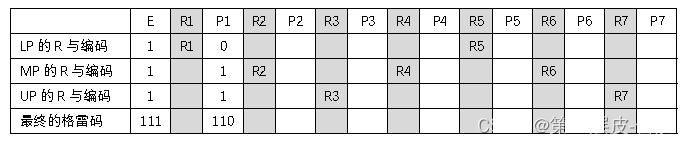

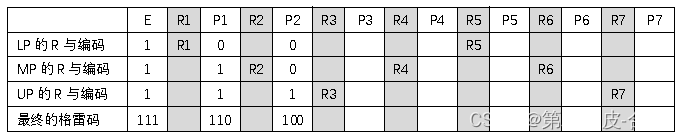

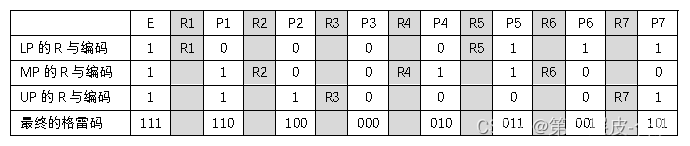

这些R就像一个个隔断,每次编码碰到它们,就要翻转一下。利用这个规律,可以把TLC 2-3-2读取的格雷码构造出来。先画一张空表,如下

接下去把7个R分配到三个不同的page上。需要注意的一个点是,任意两个Vt状态之间,各个Page所对应的R,出现的次数“不能全是”偶数次。因为二进制只有0和1,若某page的两个编码之间出现偶数个R,那么0会翻转回0,1会翻转回1。如果所有page都如此,就会出现重复编码。举例如果P1和P6之间,LP/MP/UP都被分配了两个R,那么P1和P6的编码一定是重复的。还好TLC的R只有7个,且分在三个不同的page上,分配时较容易达成这一要求。

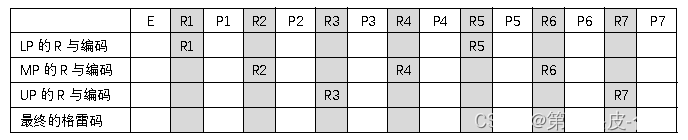

定义MP的三个比较电压为R2、R4和R6,LP的两个比较电压为R1、R5,UP的两个比较电压为R3、R7。当然也可以把LP和UP的比较电压对换,一样能得到一组2-3-2的格雷码。先以上面的定义为基准,得到

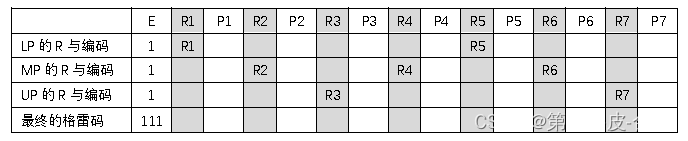

然后就可以往这张表里填各个page的Vt编码了。由于一般约定E对所有page的编码为1,那么

1)对LP而言,从左往右,编码碰到R1之后翻转为0;再碰到R5,翻转回1

2)对MP而言,从左往右,编码碰到R2翻转为0;碰到R4翻转为1;最后碰到R6翻转为0

3)对LP而言,从左往右,编码碰到R3之后翻转为0;再碰到R7,翻转回1

如果我们是一步一步填表的,那就是

总结

格雷码1就是典型的1-2-4编码,格雷码2和3都是2-3-2编码。为了支撑TLC三个page的读平衡,可以使用格雷码2或者格雷码3。

QLC和PLC因为有更多的R,为满足格雷码编码的要求及读平衡,R的分配会相对复杂,推荐使用代码做判断。如果读者有好的、不需要使用代码对QLC/PLC做R分配的方法,也欢迎交流。

![[NAND Flash 5.<span style='color:red;'>2</span>] SLC、MLC、<span style='color:red;'>TLC</span>、QLC、PLC NAND_<span style='color:red;'>闪</span><span style='color:red;'>存</span>颗粒类型](https://img-blog.csdnimg.cn/direct/3ead637fa6ab47ffb7aa5ff77a87eeb0.png#pic_center)