简介:

以太网:

以太网(Ethernet)是当今现有局域网采用的最通用的通信协议标准, 该标准定义了在局域网中采用的电缆类型和信号处理方法。以太网的分类有标准以太网(10Mbit/s)、 快速以太网(100Mbit/s)和千兆以太网( 1000Mbit/s) 。随着以太网技术的飞速发展, 市场上也出现了万兆以太网(10Gbit/s)。在实际应用中, 千兆以太网理论上最高通信速率为 1000Mbit/s,可以胜任大部分的使用场景。

MDC/MDIO,英文全称Management Data Clock和Management Data Input/Output,是以太网标准IEEE802.3中专门用于MAC和PYH之间管理的串行接口总线,其中MDC是总线时钟信号,MDIO为数据线。

RJ45接口:

以太网通信离不开连接端口的支持, 网络数据连接的端口就是以太网接口。 以太网接口类型有 RJ45 接口(水晶头)、 RJ11 接口(电话线接口)、 SC 光纤接口等。

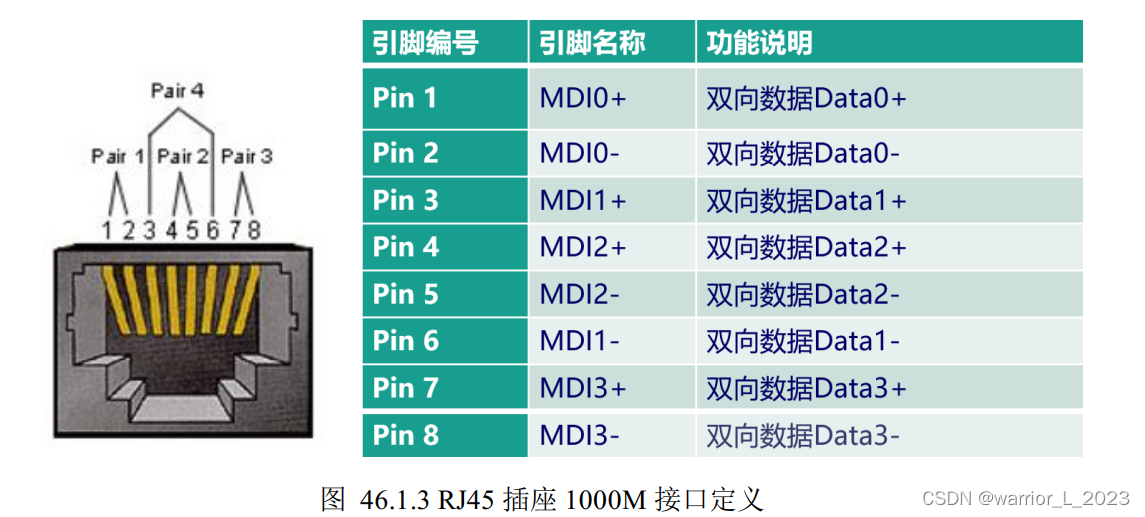

不同速度下,RJ45接口有不同的定义:

(1)10M/100M 通信速率下的定义

(2)1000M 的通信速率下, RJ45 插座的 8 根线都有用到,且都是双向引脚。

PHY与MDIO:

PHY:

PHY个人理解它应该是辅助以太网通信的数据转换芯片。

从硬件的角度来说,以太网接口电路主要由 MAC(Media Access Control)控制器和物理层接口 PHY(Physical Layer, PHY)两大部分构成。 MAC 指媒体访问控制子层协议,它和 PHY 接口既可以整合到单颗芯片内,也可以独立分开,对于本次设计来说, MAC 控制器由 FPGA 实现, PHY 芯片指开发板板载的以太网芯片。

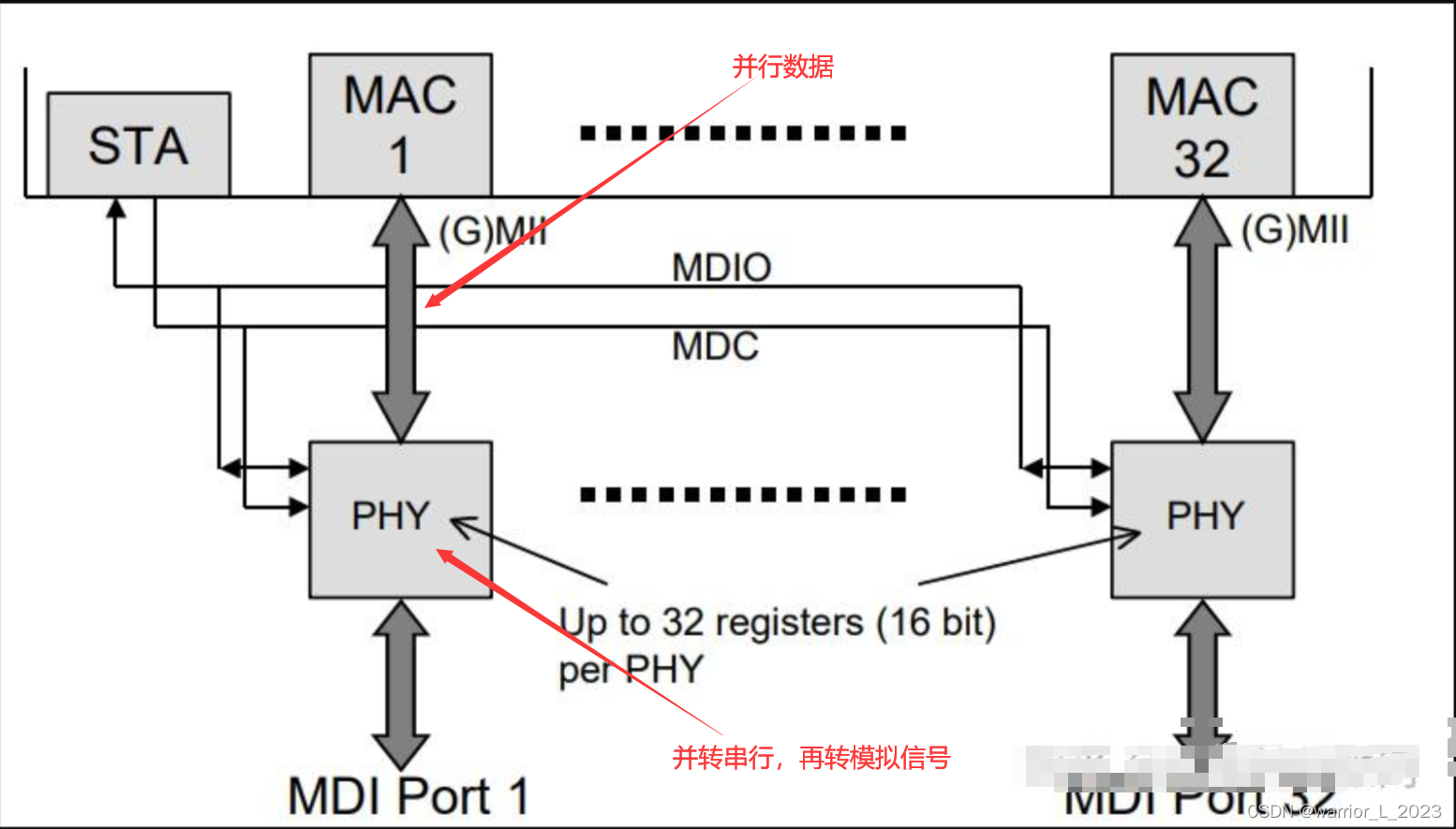

PHY 在发送数据的时候,接收 MAC 发过来的数据(对 PHY 来说,没有帧的概念,都是数据而不管什么地址,数据还是 CRC),把并行数据转化为串行流数据,按照物理层的编码规则把数据编码转换为模拟信号发送出去,接收数据时的流程反之。

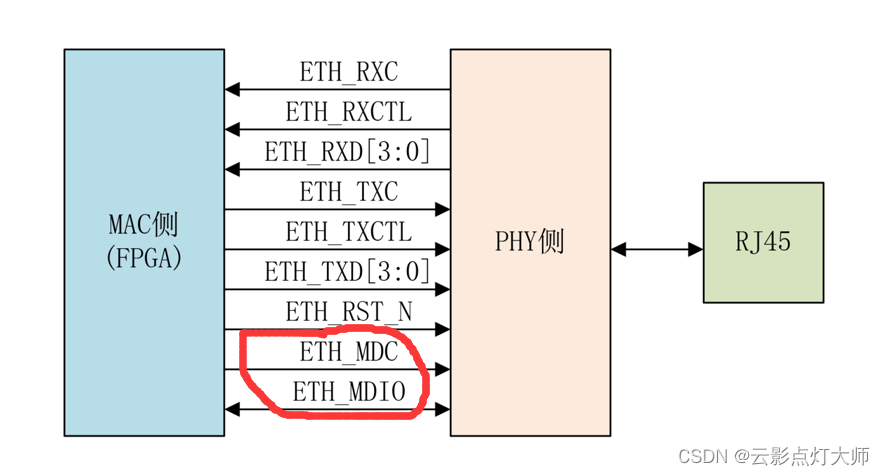

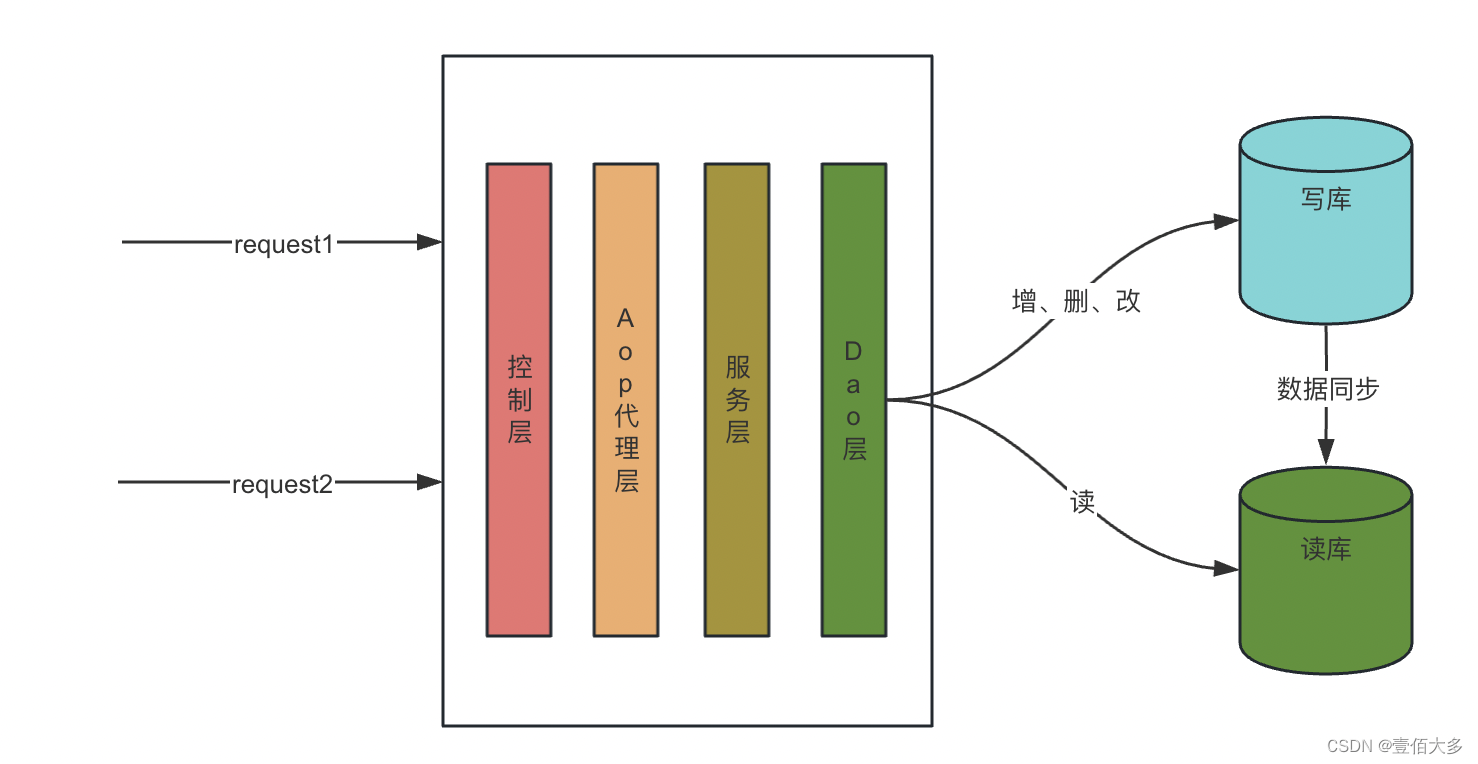

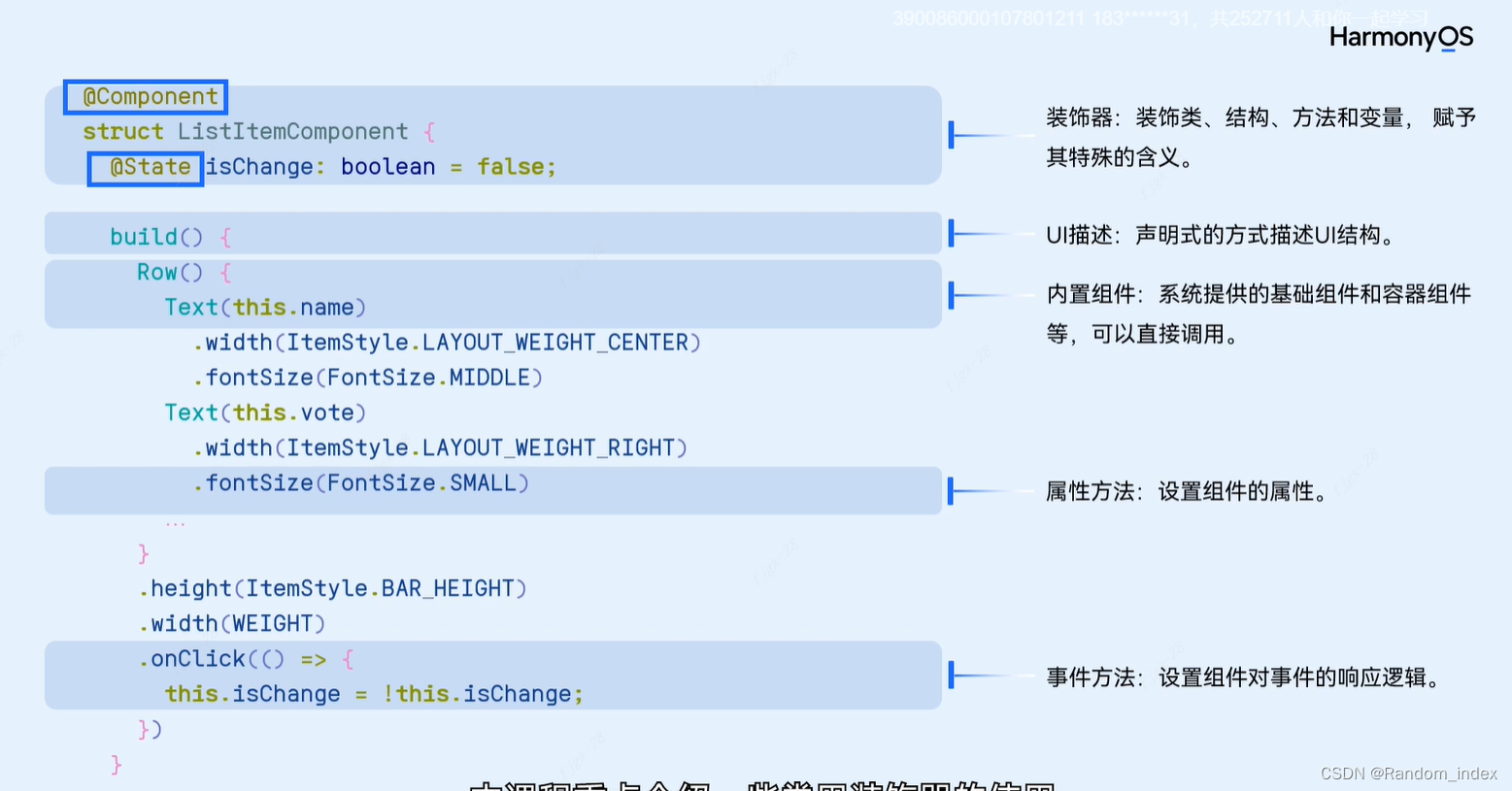

如图:

PHY 还提供了和对端设备连接的重要功能,并通过 LED 灯显示出自己目前的连接状态和工作状态。当我们给网卡接入网线的时候, PHY 芯片不断发出脉冲信号来检测对端是否有设备,它们通过标准的“语言”交流,互相协商并确定连接速度、双工模式、是否采用流控等。通常情况下,协商的结果是两个设备中能同时支持的最大速度和最好的双工模式。这个技术被称为AutoNegotiation,即自协商。

补充以太网芯片PHY的介绍:

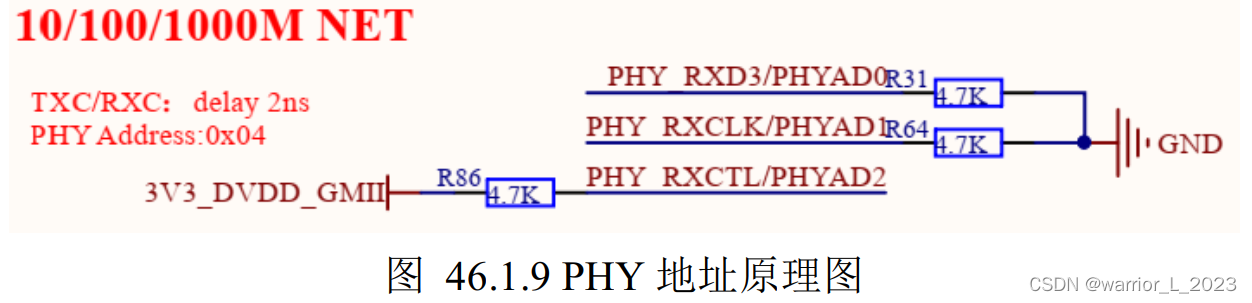

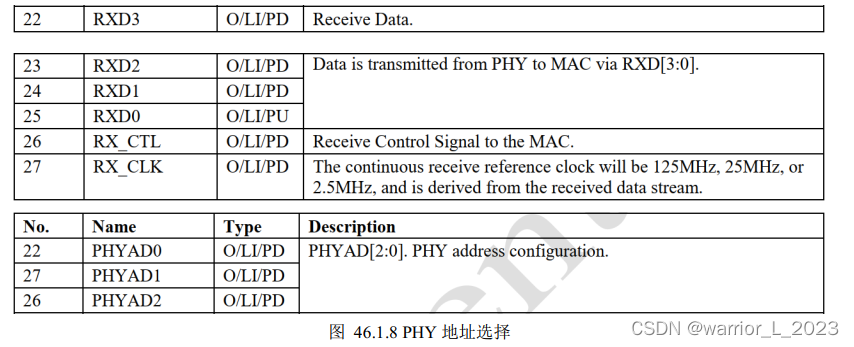

地址:

YT8531 芯片的 PHY 地址由 PHYAD0、 PHYAD1 和 PHYAD2 引脚决定,如下图所示: PHY 地址一共有3 位,我们可以通过硬件电路设置 PHYAD[2:0]引脚为上拉或者下拉,即分配为高低电平, 0 或 1,从而表示不同的地址。

所以地址为:0000_0100 == 0x04

复位:

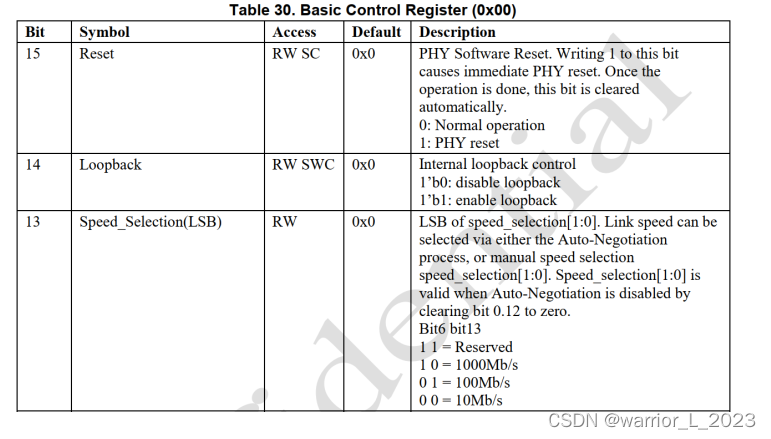

YT8531 芯片复位后, PHY 内部寄存器的数据会恢复默认的状态,并且重新开始和 MAC 进行自协商。YT8531 支持两种复位方式,一种是硬件复位,另外一种是软件复位。硬件复位时通过 PHY_RST_N 引脚实现对 PHY 芯片的复位,当 ETH_RST_N 引脚持续 10ms 的低电平时,即可实现对 PHY 芯片的复位。软件复位通过向寄存器地址 0x00 的 Bit[15]写入 1 进行复位,并且在完成复位后,该位会自动清零。

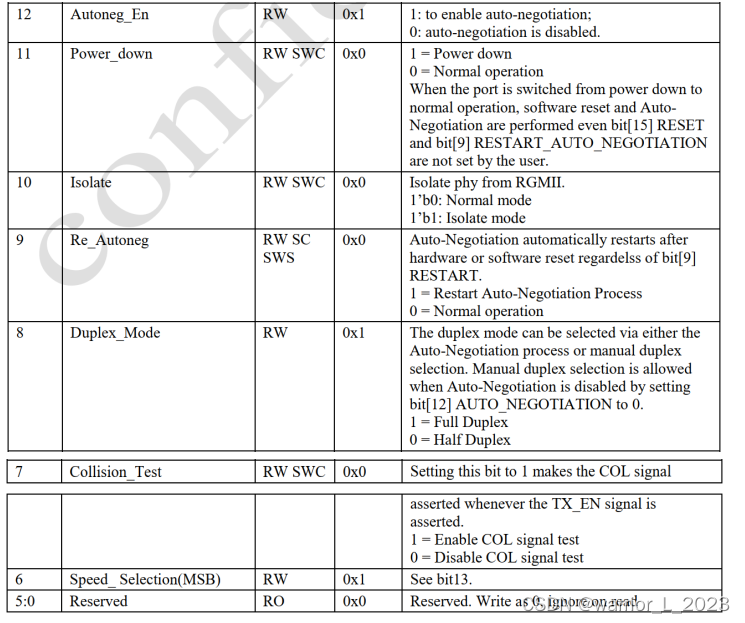

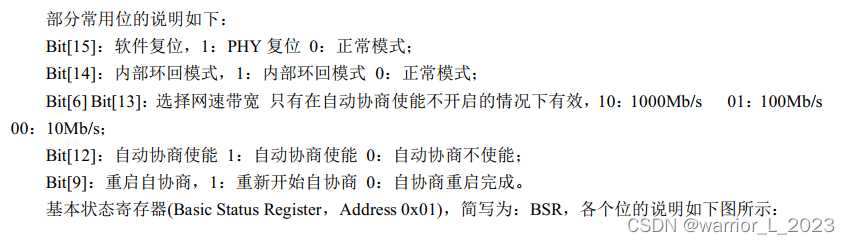

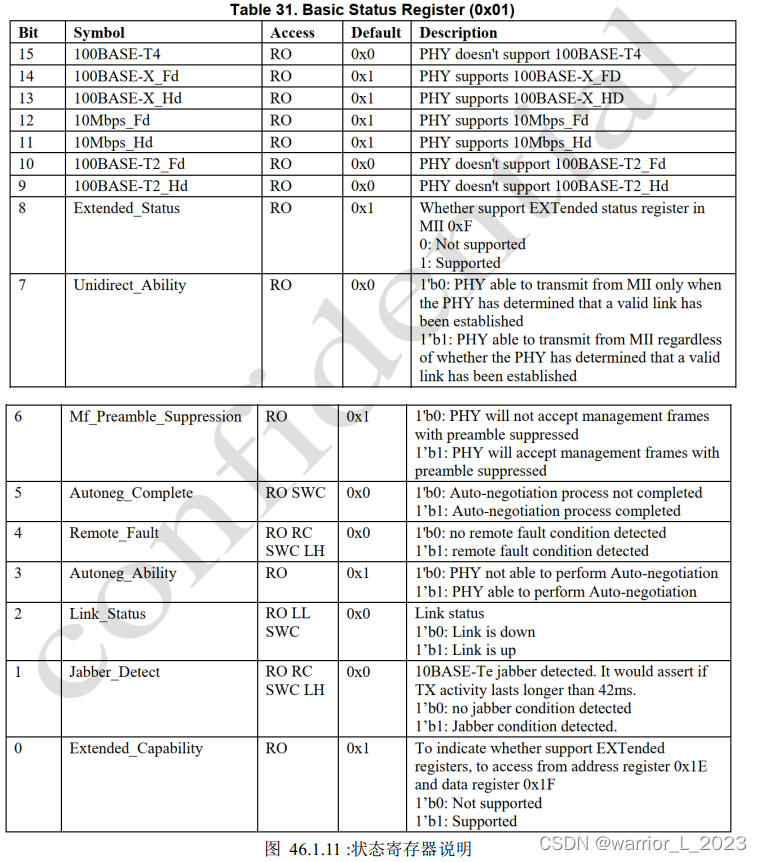

寄存器:

YT8531 共有 22 位寄存器,这里我们仅介绍本实验用到的三个寄存器,控制寄存器、状态寄存器以及PHY 芯片具体状态寄存器。

可以知道的是这三个寄存器,每个都是16bit。哈哈。

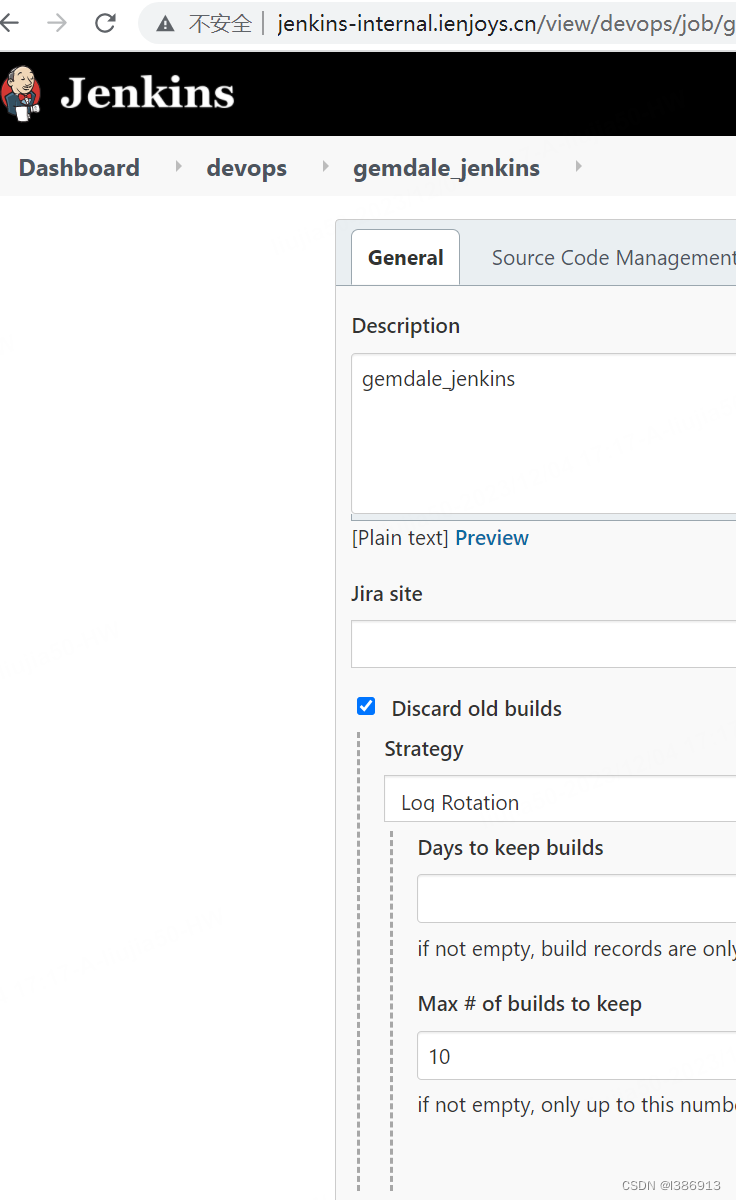

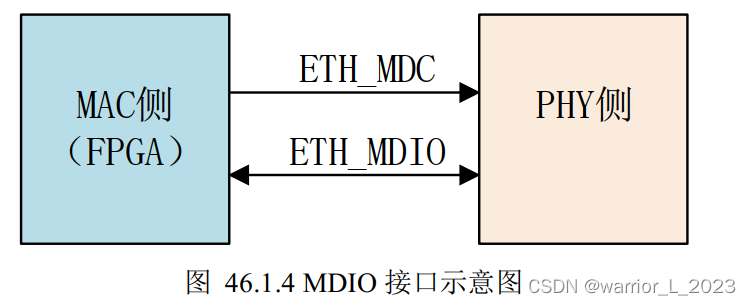

MDIO 接口:

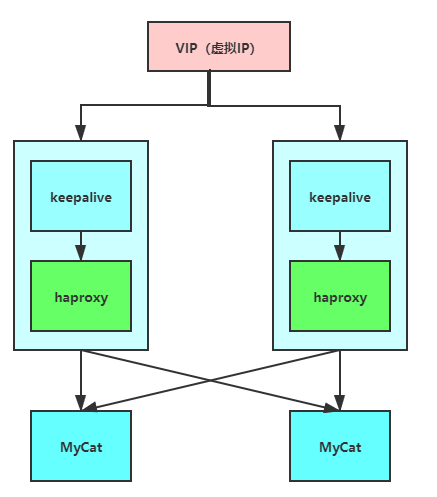

MAC 和 PHY 芯片有一个配置接口,即 MDIO 接口,可以配置 PHY 芯片的工作模式以及获取 PHY 芯片的若干状态信息。 PHY 芯片内部包含一系列寄存器,用户通过这些寄存器来配置 PHY 芯片的工作模式以及获取 PHY 芯片的若干状态信息,如连接速率、双工模式、自协商状态等。 FPGA 通过 MDIO 接口对 PHY芯片内部的寄存器进行配置。通常情况下, PHY 芯片在默认状态下也可以正常工作,在做以太网通信实验时,对 MDIO 接口的配置不是必须的,本章旨在向大家介绍 MDIO 接口以及如何对 MDIO 接口进行读写操作。 MAC 和 PHY 连接示意图如下图所示:

MDIO 接口也称为 SMI 接口(Serial Management Interface,串行管理接口),包括 ETH_MDC(数据管理时钟)和 ETH_MDIO(数据管理输入输出)两条信号线。 ETH_MDC 为 ETH_MDIO 提供时钟, ETH_MDC的最大时钟不能超过 12.5Mhz。 ETH_MDIO 为双向数据引脚,既用于发送数据,也用于接收数据。

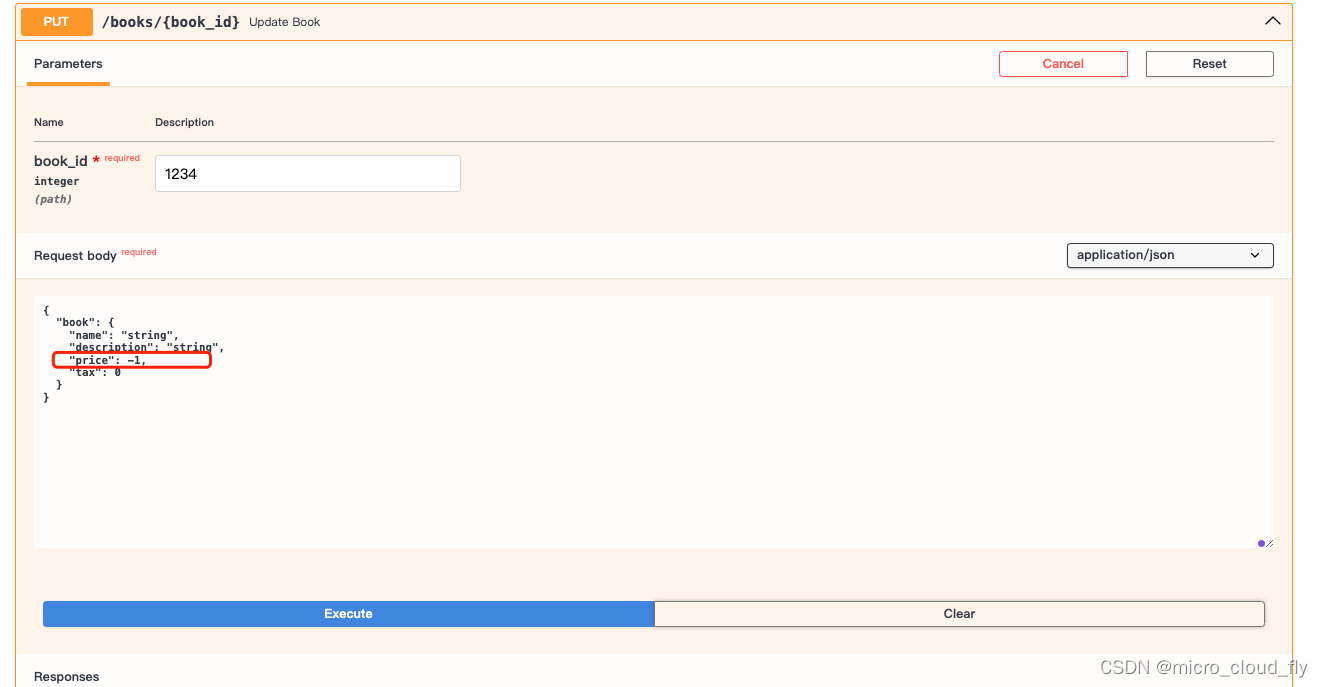

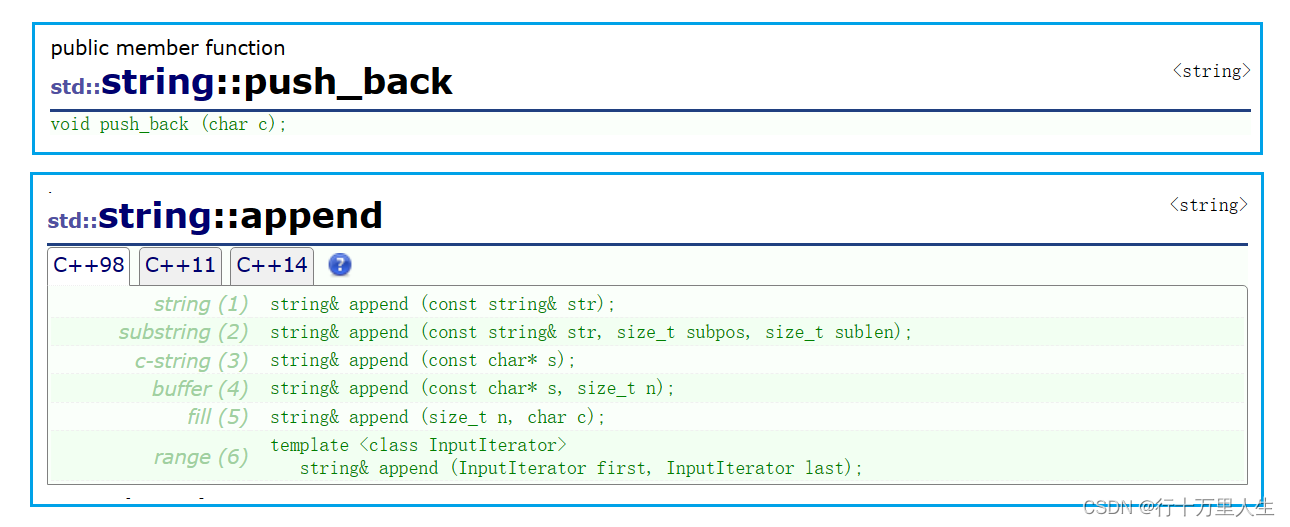

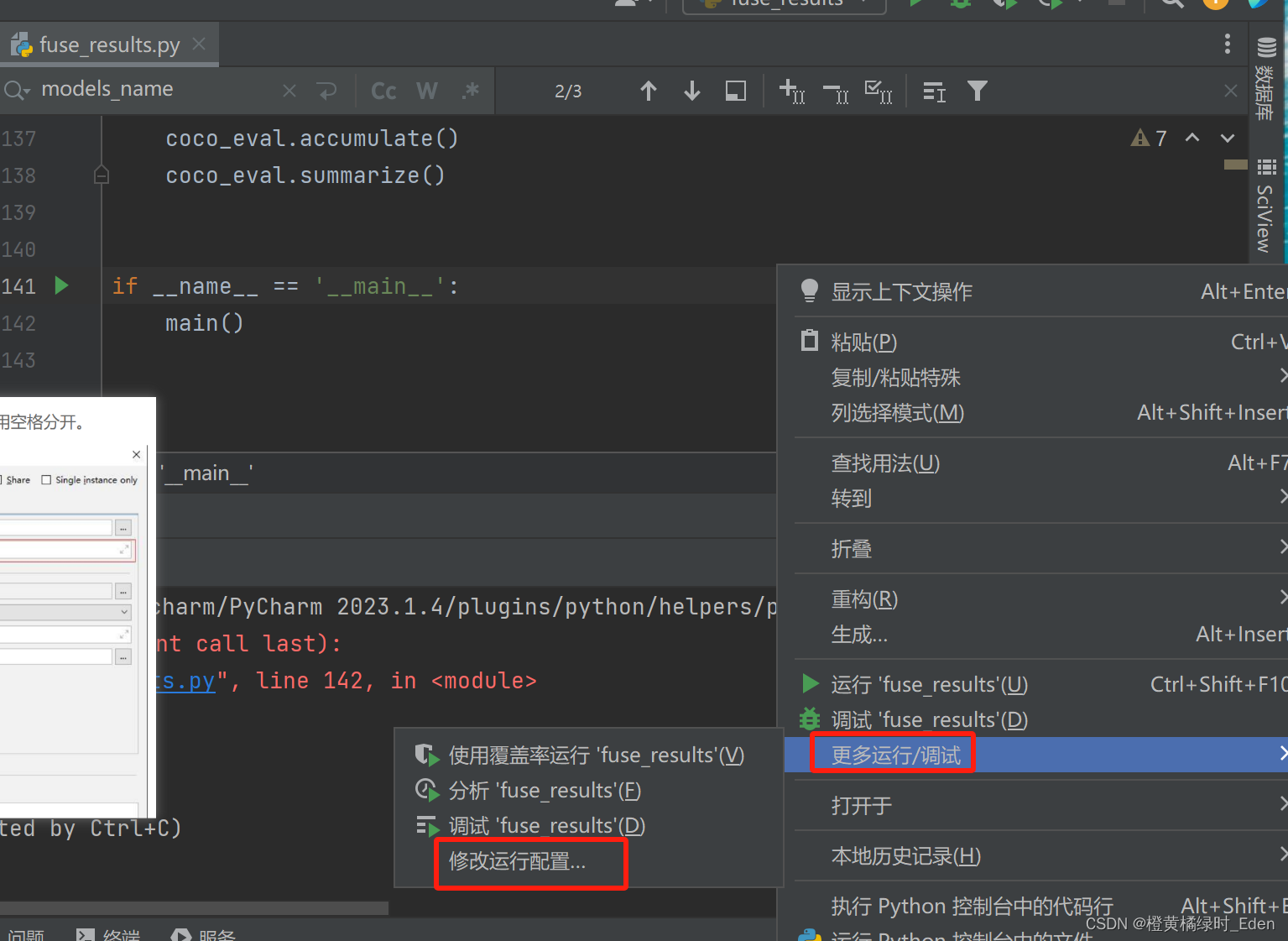

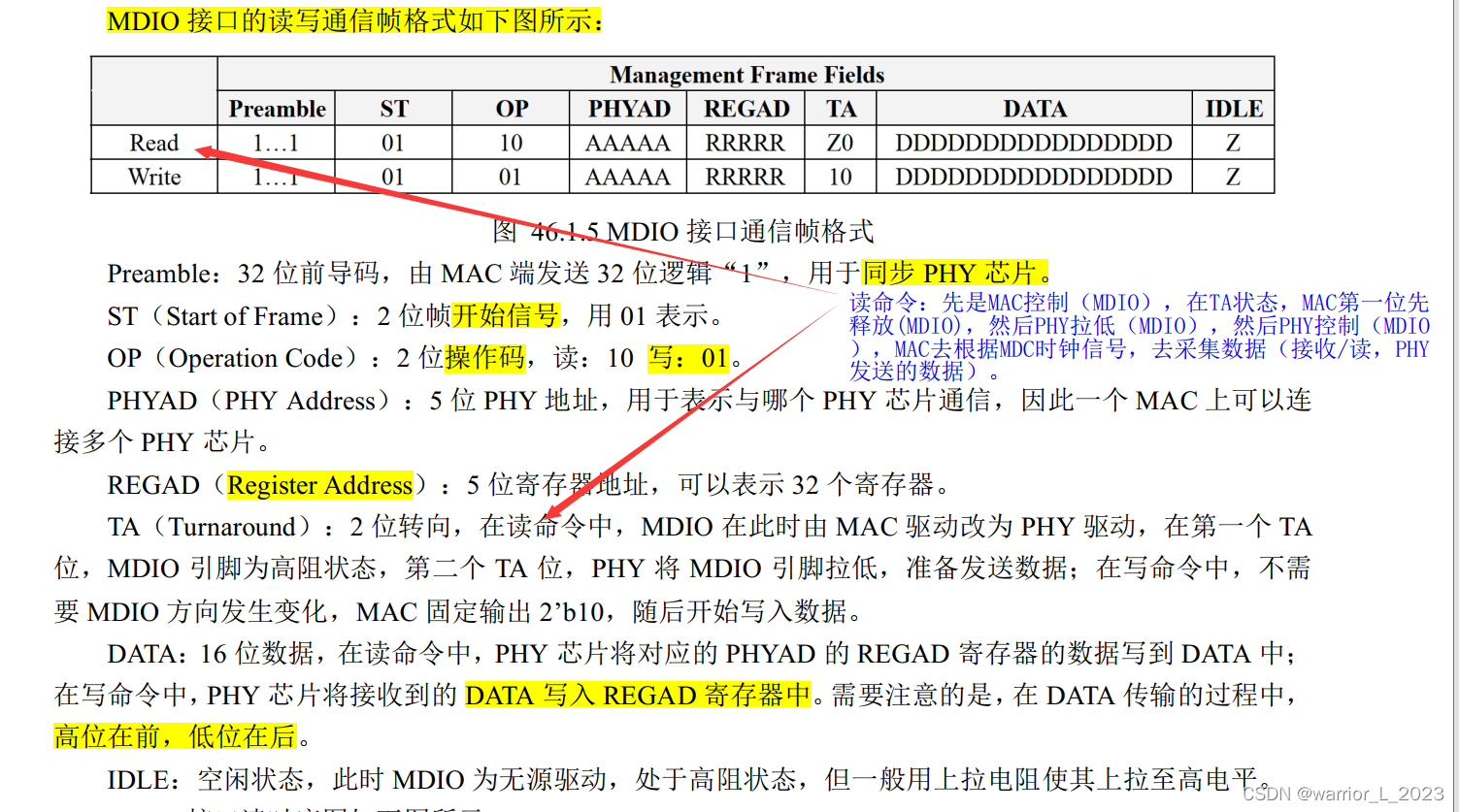

MDIO 接口的读写通信帧格式如下图所示:

读命令:先是MAC控制(MDIO),在TA状态,MAC第一位先释放(MDIO),然后PHY拉低(MDIO),然后PHY控制(MDIO),MAC去根据MDC时钟信号,去采集数据(接收/读,PHY发送的数据)。

读时序:

分析:

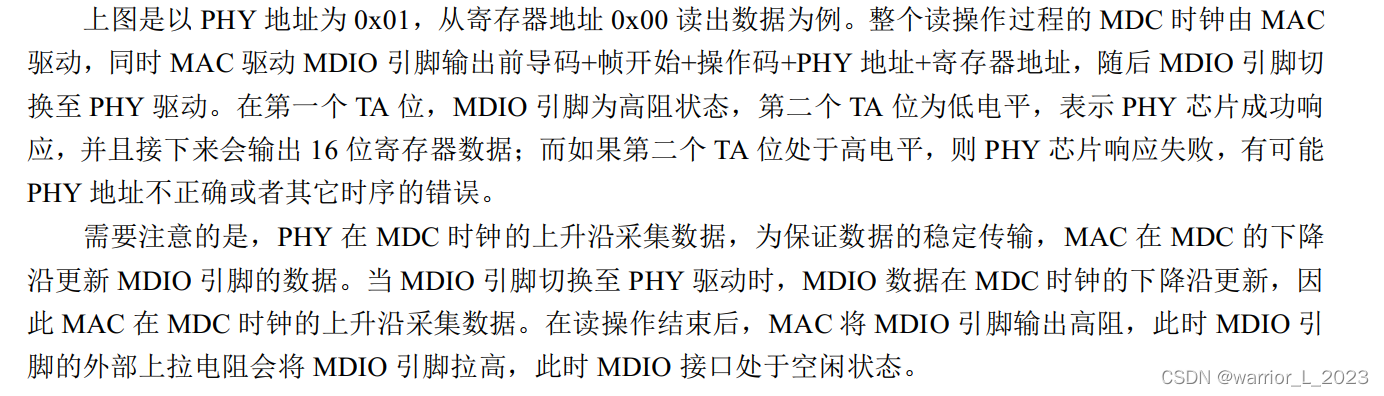

经过观察,MDIO数据线,数据变化的时间点是在MDC的下降沿,MAC或者PHY对MDIO数据线采样的时间点是在MDC的上升沿。

也就是说在MDC上升沿附近,MDIO数据要保持稳定。下降沿,MDIO可以改变数据。

读时序中,先由MAC控制MDIO发送“32bit前导码”,然后发送“2bit帧开始信号01”,然后发送“2bit操作码10(读op)”,然后发送“5bitPHY的地址”,然后发送“5bit寄存器地址”,然后MAC“释放MDIO,产生ibit的高阻态,下一位由PHY去拉低MDIO,PHY接管数据线MDIO”.

然后PHY,发送16bit数据。

发送完,MDIO处于空闲状态,PHY与MAC都不驱动MDIO,一般由上拉电阻拉高MDIO。

以下是”原子哥“的分析:

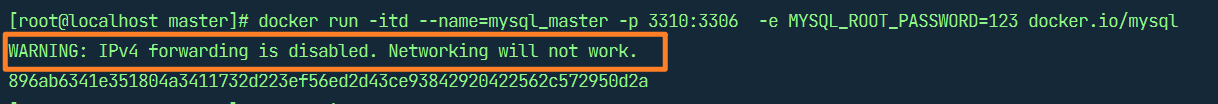

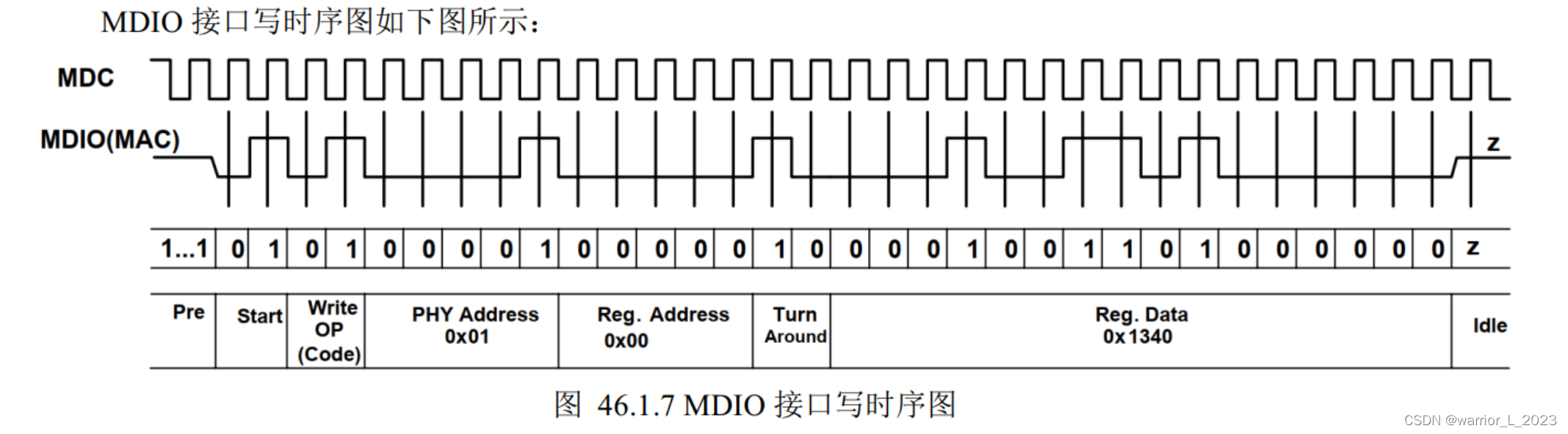

写时序

分析:

看图,写时序中,MDIO全程由MAC控制,(后面发送完MDIO无驱动)。

写时序中,先由MAC控制MDIO发送“32bit前导码”,然后发送“2bit帧开始信号01”,然后发送“2bit擦操作码01”,然后发送“5bitPHY地址”,然后发送“5bit寄存器地址”,然后发送“2bit转向码10,(无转向)”,然后发送“16bit的数据,写入PHY的内部寄存器中”。然后MAC释放MDIO,MDIO被上拉电阻拉高或者为高阻态。

以下是“原子哥”的分析:

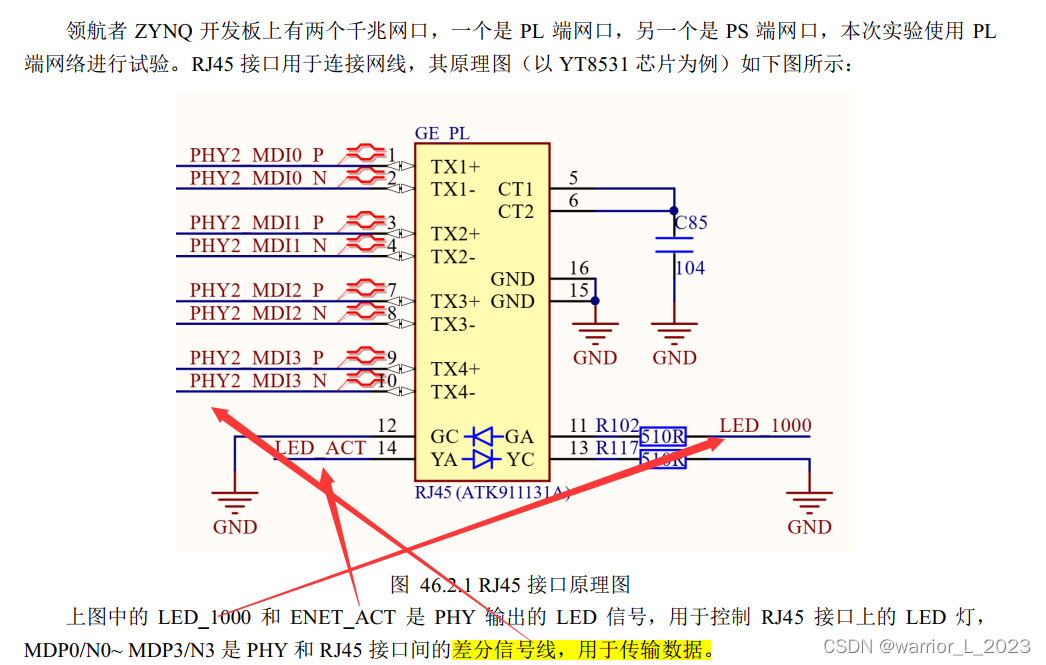

硬件电路:

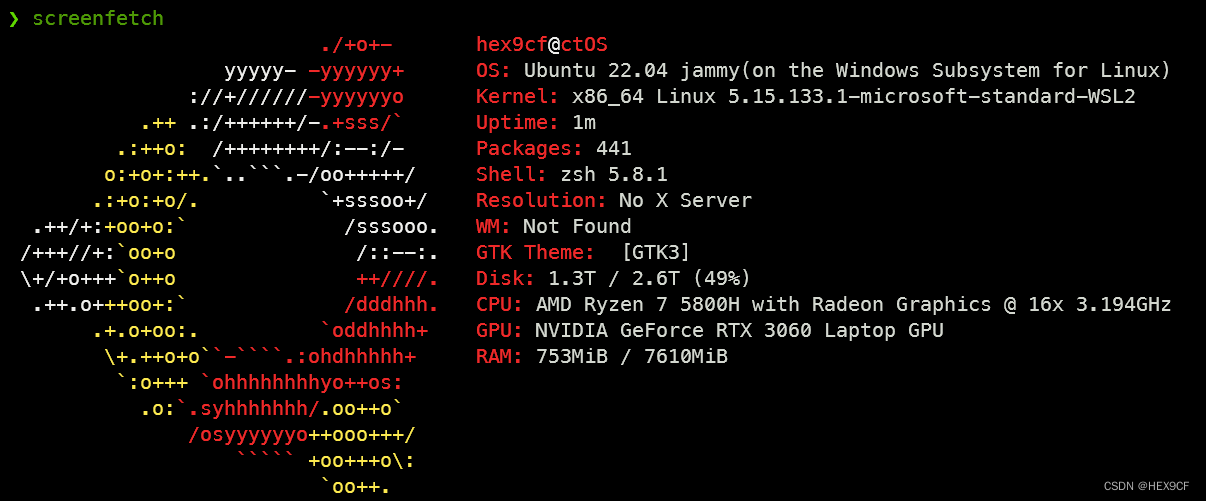

以太网的数据传输离不开以太网 PHY(物理层)芯片的支持, 物理层定义了数据发送与接收所需要的电信号、线路状态、时钟基准、数据编码和电路等,并向数据链路层设备提供标准接口。的领航者开发板上使用的 PHY 芯片为裕太车通公司的 YT8531 或 YT8511(原理图上两款芯片设计稍有差异,但网口驱动部分的例程是完全兼容的),其原理图如下图所示:

实验任务:

本节实验任务是使用领航者 ZYNQ 开发板上的以太网接口,完成 MDIO 接口的读写测试实验。板载的触摸按键(TPAD)控制 MDIO 接口进行软复位,并通过两个 LED 灯实时指示当前网口的连接速度。当 LED0 灯亮的时候,表示当前的网口速率为 10Mbps;当 LED1 亮的时候,表示当前网口的速率为100Mbps;当两个 LED 都亮的时候,表示当前网口的速率为 1000Mbps;当两个 LED 灯都熄灭时,说明当前网络自协商失败,硬件或者网络存在异常。